## 5. Performance Analysis of Distributed Embedded Systems

© Lothar Thiele

Ernesto Wandeler

ETH Zurich, Switzerland

## Contents of Lectures (Lothar Thiele)

### Outline

- Motivation / Problem Statement

- Modular Performance Analysis

- MPA Case Study

- Real-Time Interfaces / Interface-Based Design

- IBD Case Study

- Efficient Computation and Tool Support

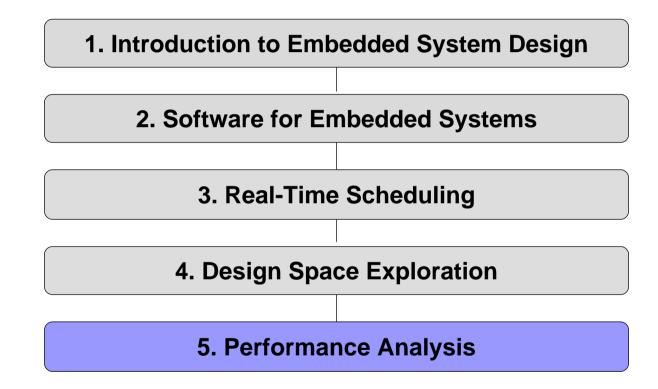

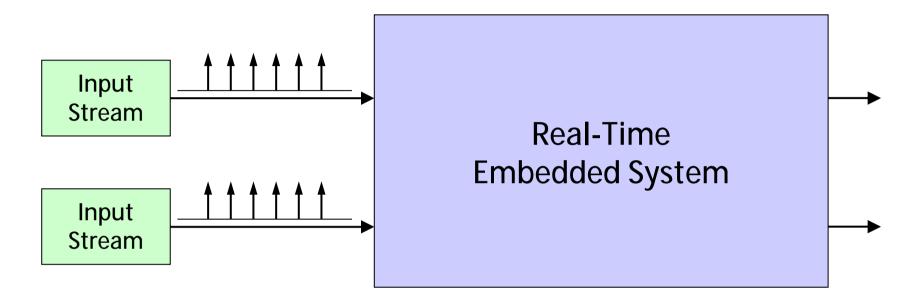

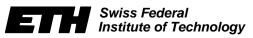

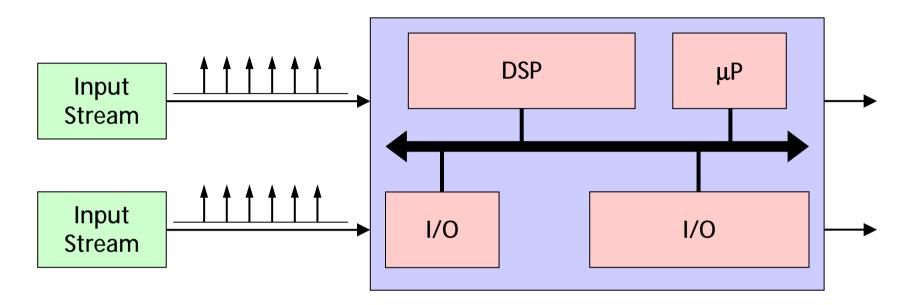

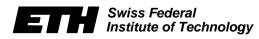

Real-Time Embedded System...

...System Level Performance Analysis

Computational Resources ...

Computational Resources ...

... Communication Resources ...

Computational Resources ...

... Communication Resources ...

... Tasks (HW/SW Components)

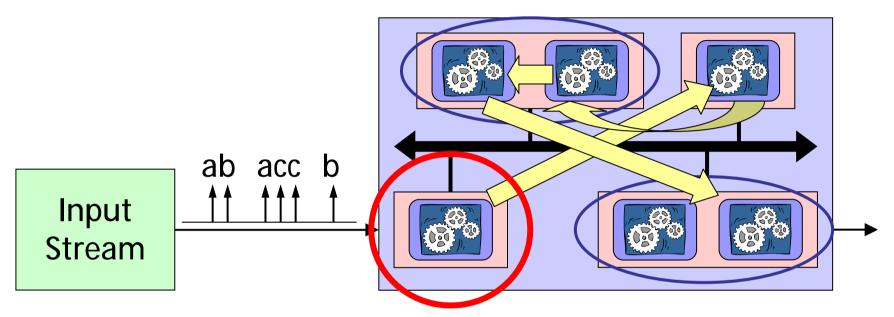

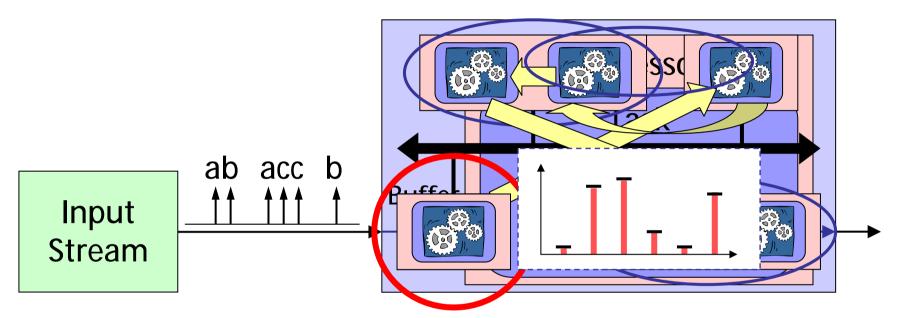

### System-Level Performance Analysis

#### **System-Level Performance Methods**

#### Difficulties

**Task Communication**

Task Scheduling

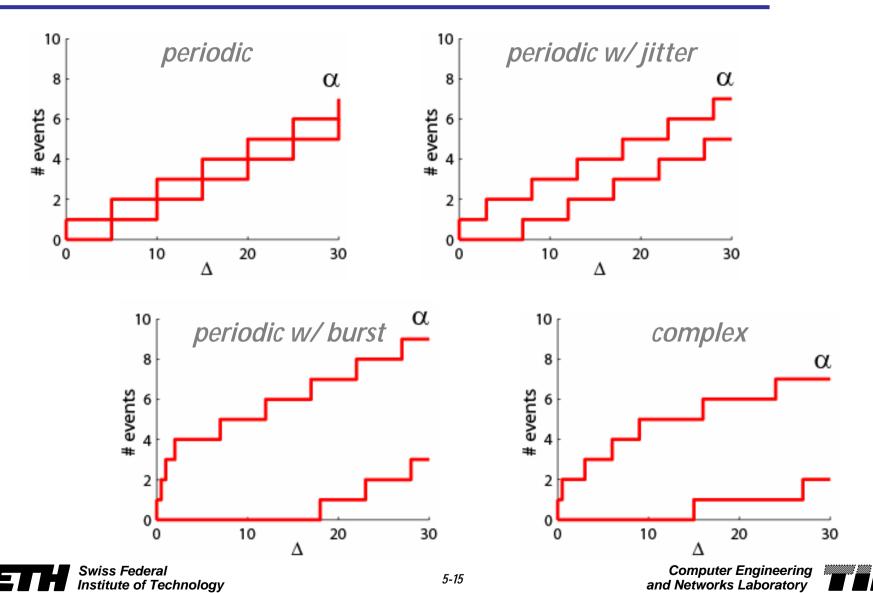

#### Complex Input:

- Timing (jitter, bursts, ...)

- Different Event Types

Swiss Federal Institute of Technology

### Difficulties

Task Communication

Task Scheduling

#### Complex Input:

- Timing (jitter, bursts, ...)

- Different Event Types

Swiss Federal Institute of Technology

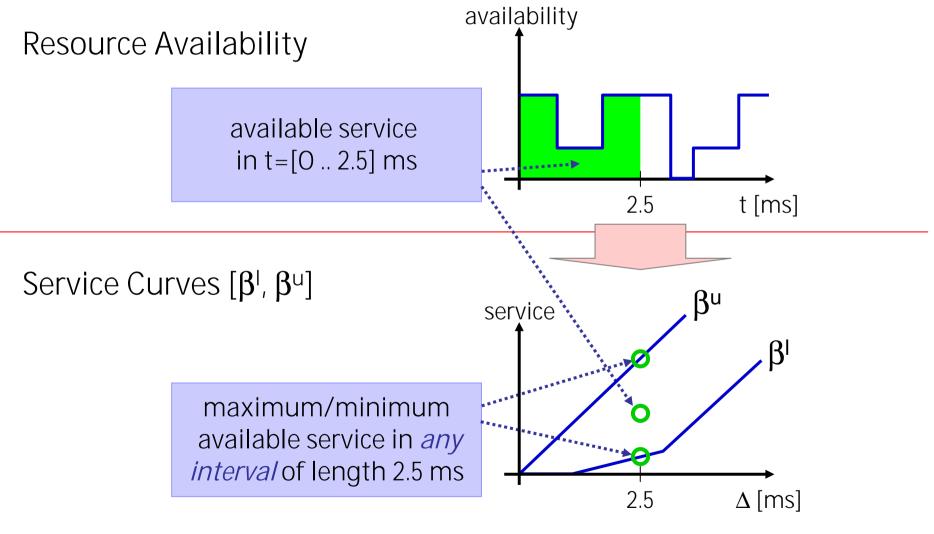

#### Variable Resource Availability

Variable Execution Demand

- Input (different event types)

- Internal State (Program, Cache, ...)

#### Outline

- Motivation / Problem Statement

- Modular Performance Analysis

- MPA Case Study

- Real-Time Interfaces / Interface-Based Design

- IBD Case Study

- Efficient Computation and Tool Support

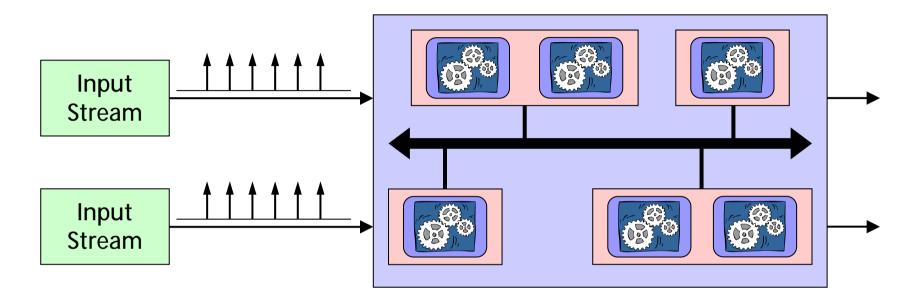

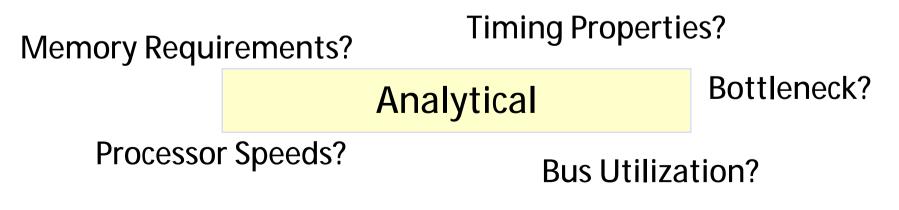

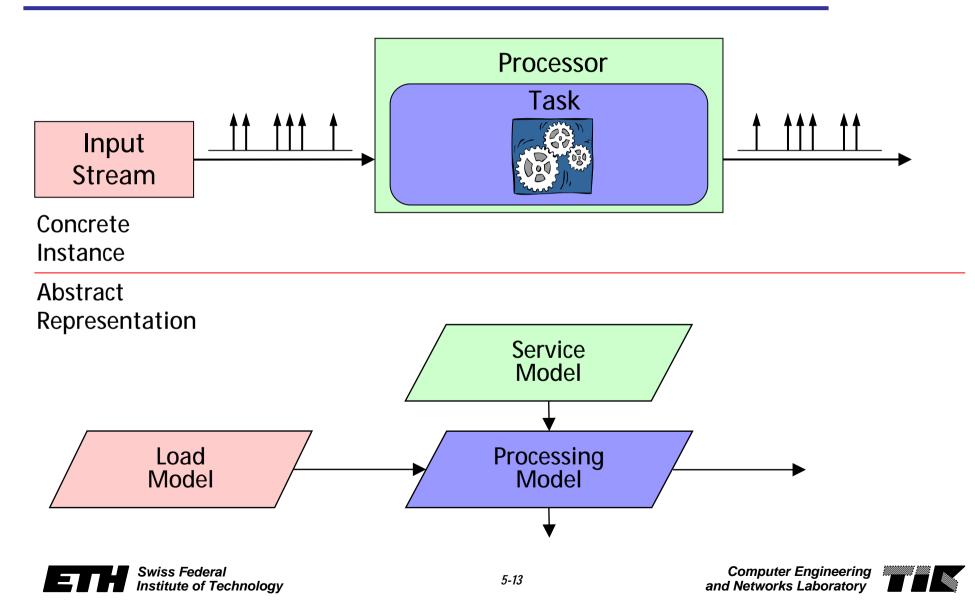

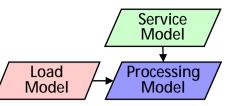

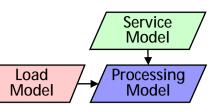

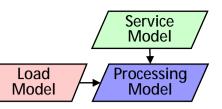

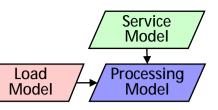

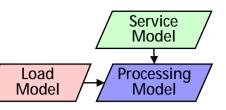

#### Abstract Models for Performance Analysis

Swiss Federal Institute of Technology

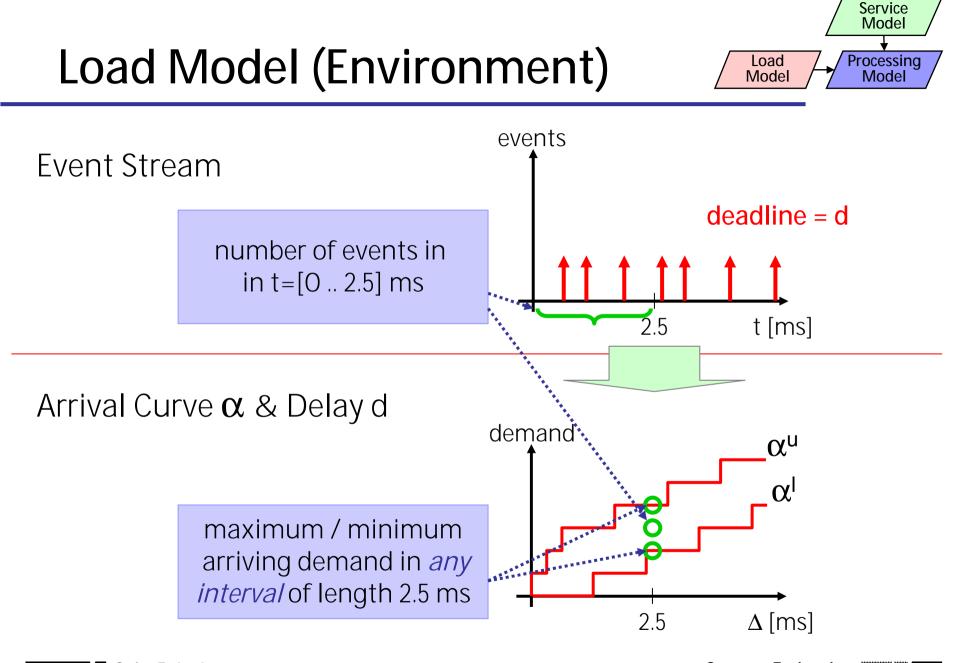

# Load Model - Examples

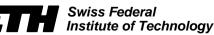

# Service Model (Resources)

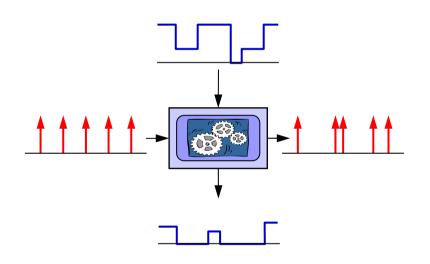

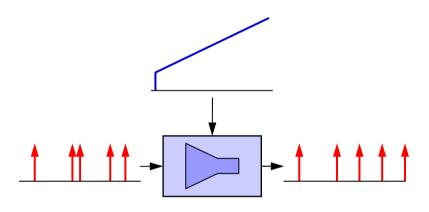

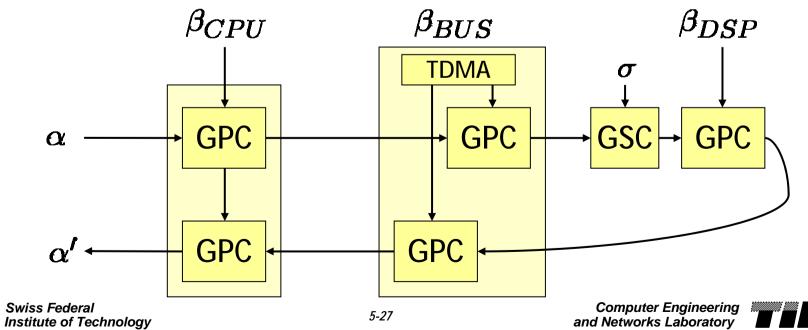

Greedy Processing Component

#### **Behavioral Description**

- Component is triggered by incoming events.

- A fully preemptable task is instantiated at every event arrival to process the incoming event.

- Active tasks are processed in a greedy fashion in FIFO order.

- Processing is restricted by the availability of resources.

Greedy Processing Component

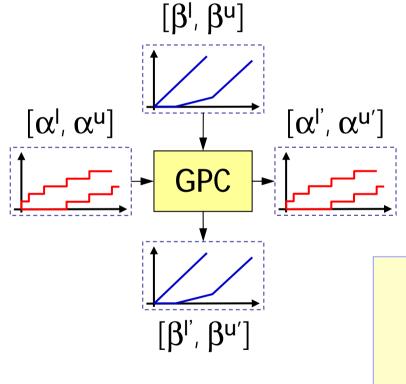

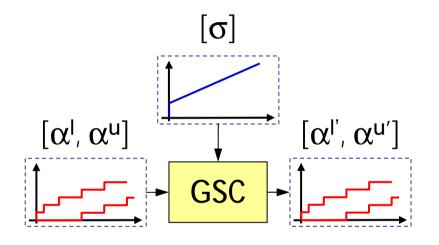

Real-Time Calculus

$$\alpha^{'u} = \min\{(\alpha^{u} \otimes \beta^{u}) \otimes \beta^{l}, \beta^{u}\}$$

$$\alpha^{'l} = \min\{(\alpha^{l} \otimes \beta^{u}) \otimes \beta^{l}, \beta^{l}\}$$

$$\beta^{'u} = (\beta^{u} - \alpha^{l}) \overline{\otimes} 0$$

$$\beta^{'l} = (\beta^{l} - \alpha^{u}) \overline{\otimes} 0$$

$$(f \otimes g)(\Delta) = \inf_{\substack{0 \le \lambda \le \Delta}} \{f(\Delta - \lambda) + g(\lambda)\}$$

$$(f \otimes g)(\Delta) = \sup_{\substack{\lambda \ge 0}} \{f(\Delta + \lambda) - g(\lambda)\}$$

$$(f \otimes g)(\Delta) = \sup_{\substack{0 \le \lambda \le \Delta}} \{f(\Delta - \lambda) + g(\lambda)\}$$

$$(f \otimes g)(\Delta) = \inf_{\substack{\lambda \ge 0}} \{f(\Delta + \lambda) - g(\lambda)\}$$

Swiss Federal Institute of Technology

Greedy Shaper Component

#### **Behavioral Description**

- Delays incoming events such that the output conforms to a given traffic specification.

- Guarantees that no events get delayed any longer than necessary.

- Works also with bursty traffic specifications.

Greedy Shaper Component

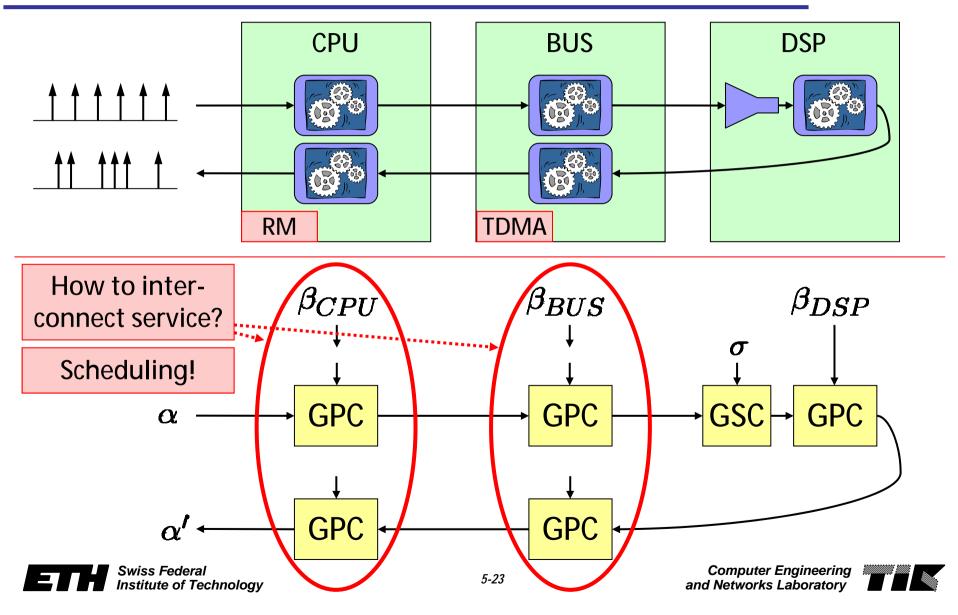

## System Composition

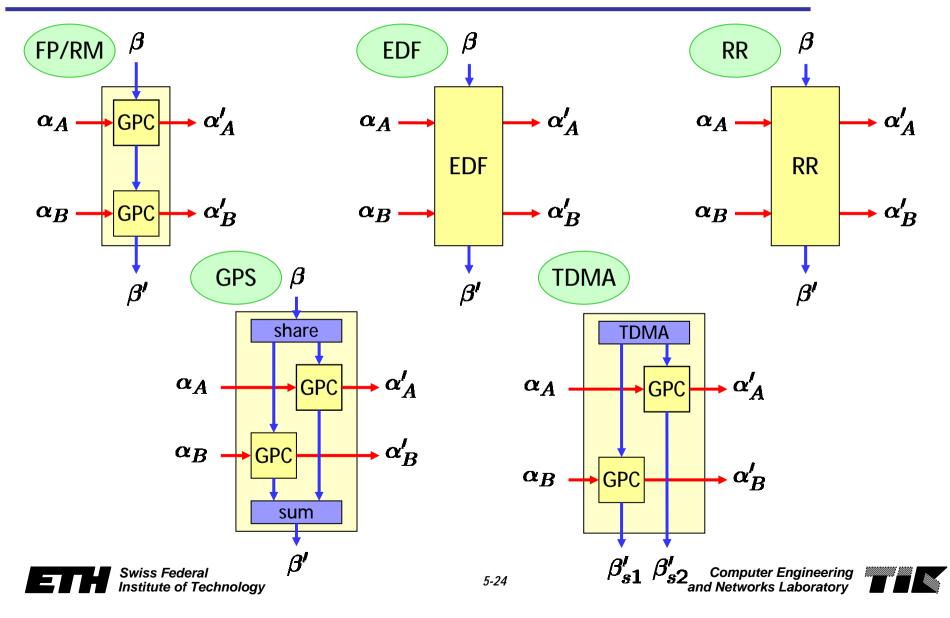

#### **Scheduling and Arbitration**

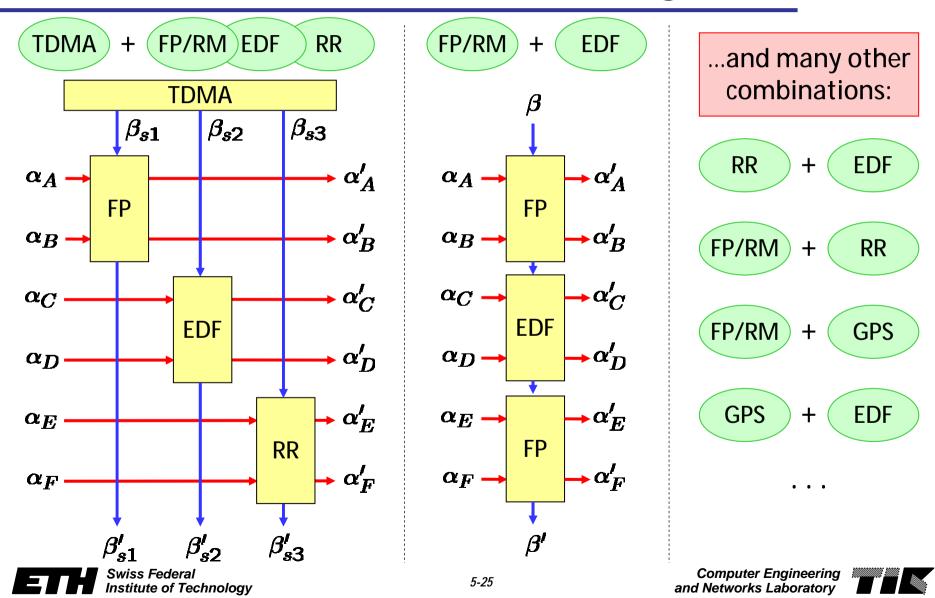

### **Mixed Hierarchical Scheduling**

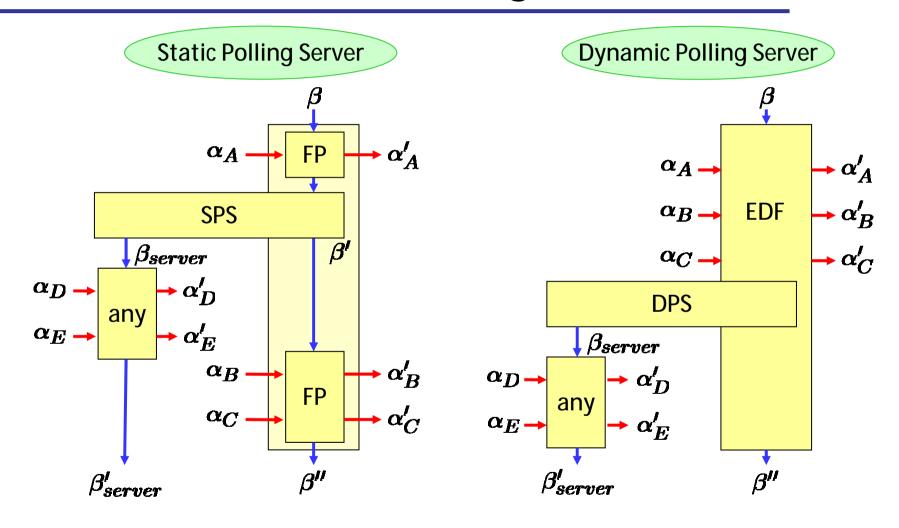

#### **Hierarchical Scheduling with Servers**

### **Complete System Composition**

#### Analysis: Delay and Backlog

5-28

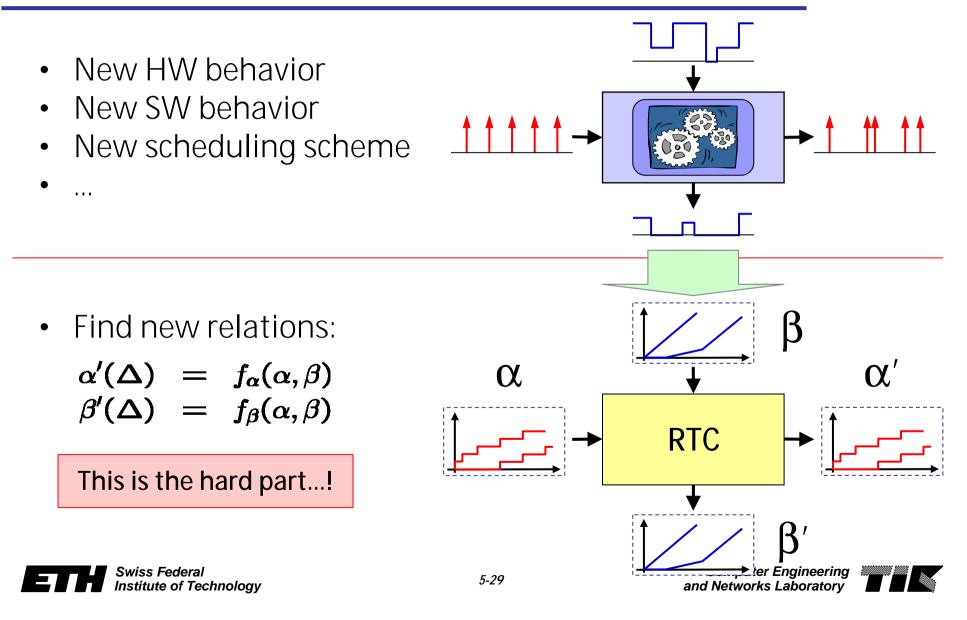

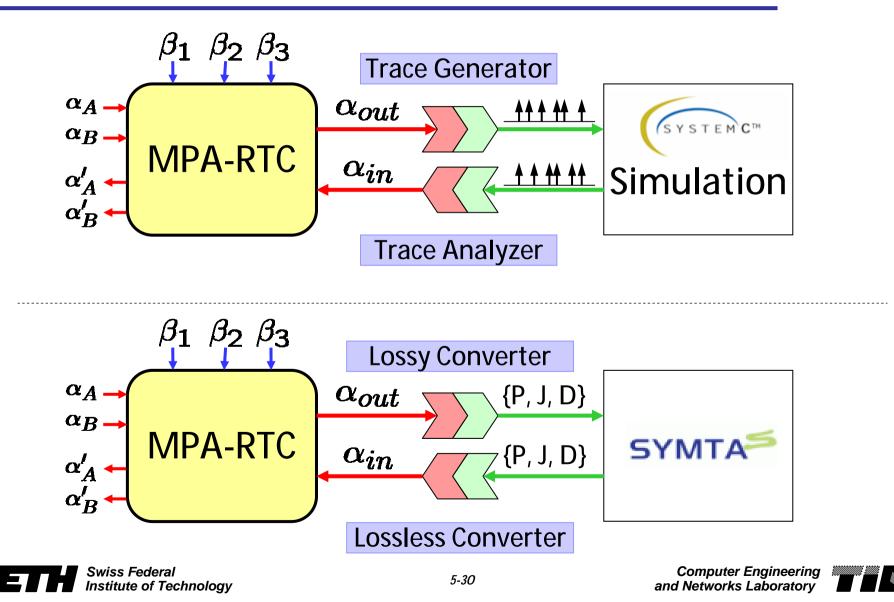

## Extending the Framework

### Embedding with other Frameworks

### Outline

- Motivation / Problem Statement

- Modular Performance Analysis

- MPA Case Study

- Real-Time Interfaces / Interface-Based Design

- IBD Case Study

- Efficient Computation and Tool Support

## **Case Study**

#### **Total Utilization:**

| - ECU1 | 5 <b>9</b> % |

|--------|--------------|

| - ECU2 | 87 %         |

| - ECU3 | 67 %         |

- BUS 56 %

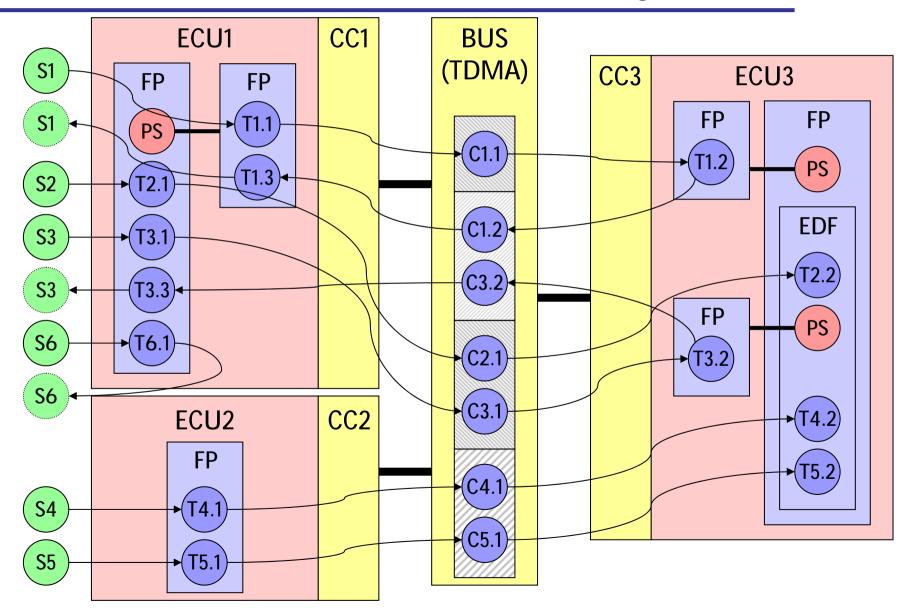

#### 6 Real-Time Input Streams

- with jitter

- with bursts

- deadline > period

#### 3 ECU's with own CC's

13 Tasks & 7 Messages - with different WCED

#### 2 Scheduling Policies

- Earliest Deadline First (ECU's)

- Fixed Priority (ECU's & CC's)

#### **Hierarchical Scheduling**

- Static & Dynamic Polling Servers

#### Bus with TDMA

- 4 time slots with different lengths (#1,#3 for CC1, #2 for CC3, #4 for CC3)

#### **Specification Data**

| Stream     | (p,j,d) [ms]      | D [s] | Task Chain                                                                                                            |

|------------|-------------------|-------|-----------------------------------------------------------------------------------------------------------------------|

| <b>S</b> 1 | (1000, 2000, 25)  | 8.0   | $\boxed{\text{T1.1} \rightarrow \text{C1.1} \rightarrow \text{T1.2} \rightarrow \text{C1.2} \rightarrow \text{T1.3}}$ |

| <b>S</b> 2 | (400, 1500, 50)   | 1.8   | $T2.1 \to C2.1 \to T2.2$                                                                                              |

| S3         | (600, 0, -)       | 6.0   | $T3.1 \rightarrow C3.1 \rightarrow T3.2 \rightarrow C3.2 \rightarrow T3.3$                                            |

| <b>S4</b>  | (20, 5, -)        | 0.5   | $T4.1 \to C4.1 \to T4.2$                                                                                              |

| S5         | (30, 0, -)        | 0.7   | $T4.1 \to C4.1 \to T4.2$                                                                                              |

| <b>S6</b>  | (1500, 4000, 100) | 3.0   | Т6.1                                                                                                                  |

| Task | е   |

|------|-----|

| T1.1 | 200 |

| T1.2 | 300 |

| T1.3 | 30  |

| T2.1 | 75  |

| T2.2 | 25  |

| T3.1 | 60  |

| T3.2 | 60  |

| T3.3 | 40  |

| T4.1 | 12  |

| T4.2 | 2   |

| T5.1 | 8   |

| T5.2 | 3   |

| T6.1 | 100 |

| Message | е   |

|---------|-----|

| C1.1    | 100 |

| C1.2    | 80  |

| C2.1    | 40  |

| C3.1    | 25  |

| C3.2    | 10  |

| C4.1    | 3   |

| C5.1    | 2   |

| Perdiodic Server    | p   | е   |

|---------------------|-----|-----|

| SPS <sub>ECU1</sub> | 500 | 200 |

| SPS <sub>ECU3</sub> | 500 | 250 |

| DPS <sub>ECU3</sub> | 600 | 120 |

| TDMA                 | t   |

|----------------------|-----|

| Cycle                | 100 |

| Slot <sub>CC1a</sub> | 20  |

| Slot <sub>CC1b</sub> | 25  |

| Slot <sub>CC2</sub>  | 25  |

| Slot <sub>CC3</sub>  | 30  |

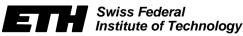

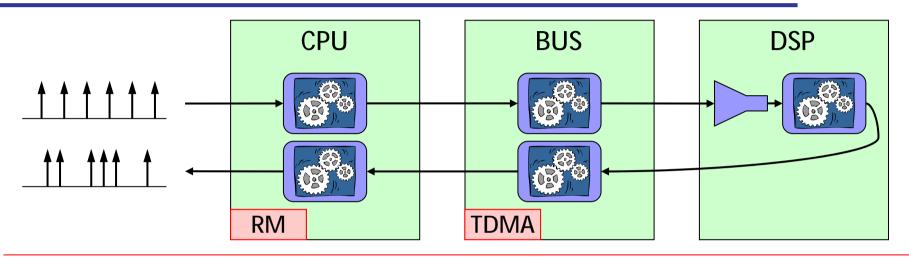

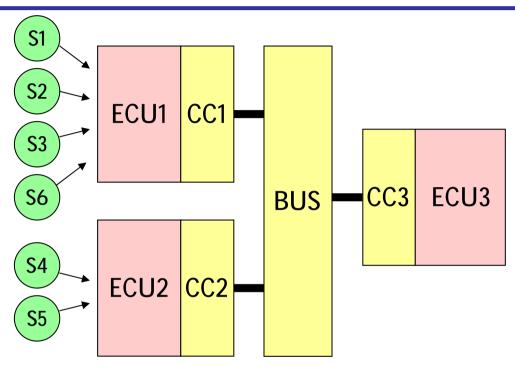

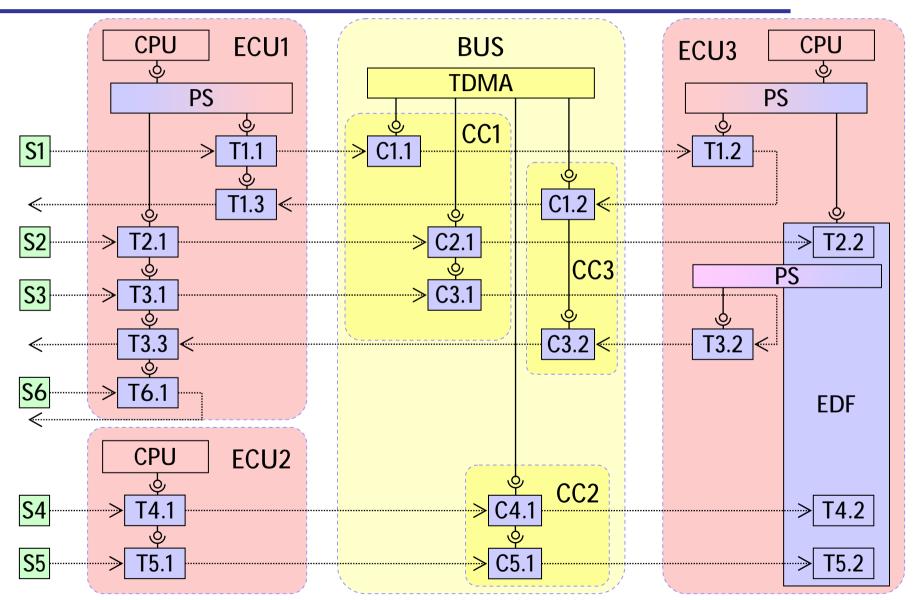

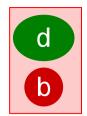

#### The Distributed Embedded System...

#### ... and its MPA Model

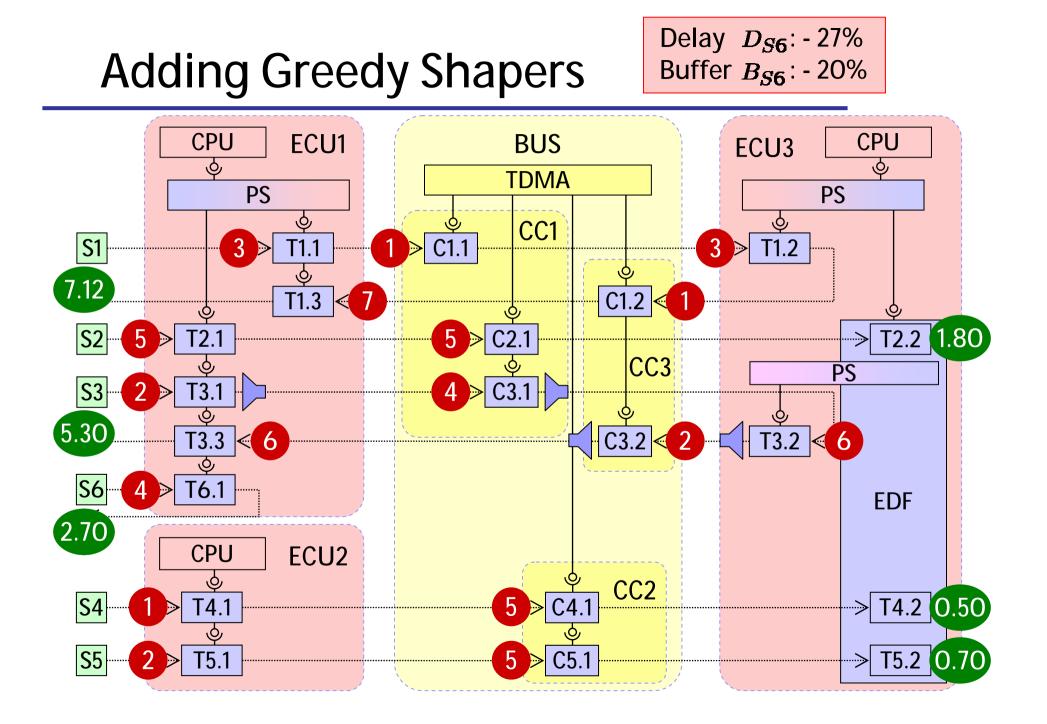

## **Buffer & Delay Guarantees**

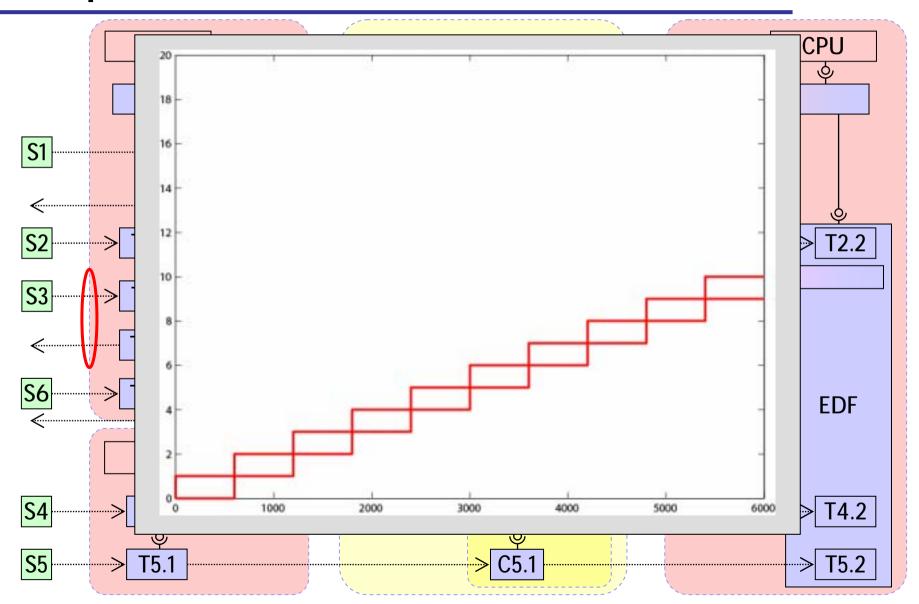

#### Input of Stream 3

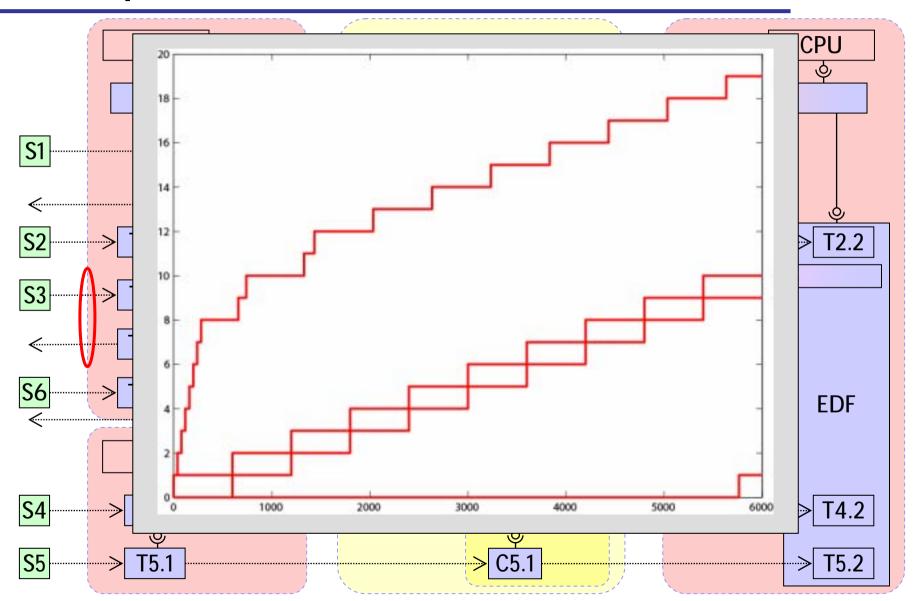

#### **Output of Stream 3**

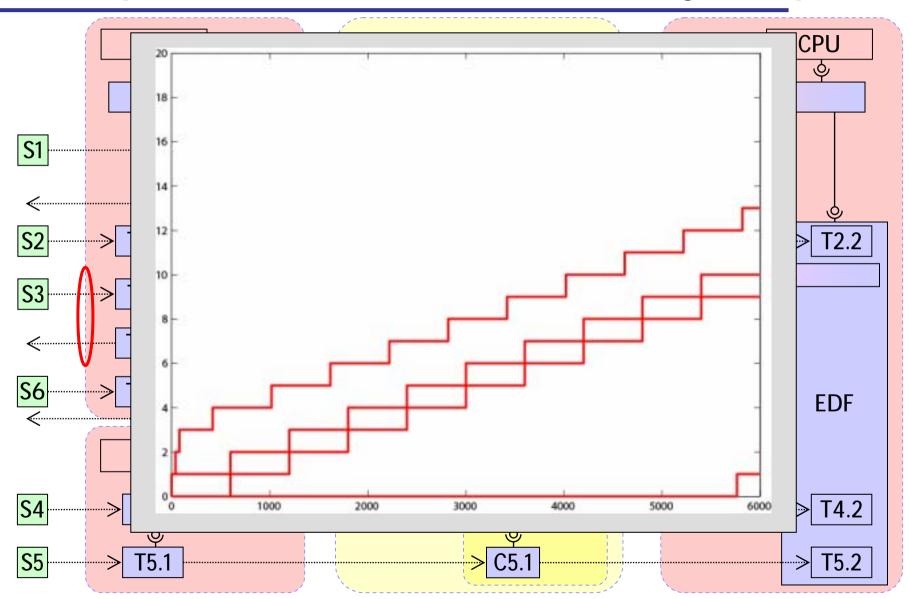

#### **Output of Stream 3 with Greedy Shapers**

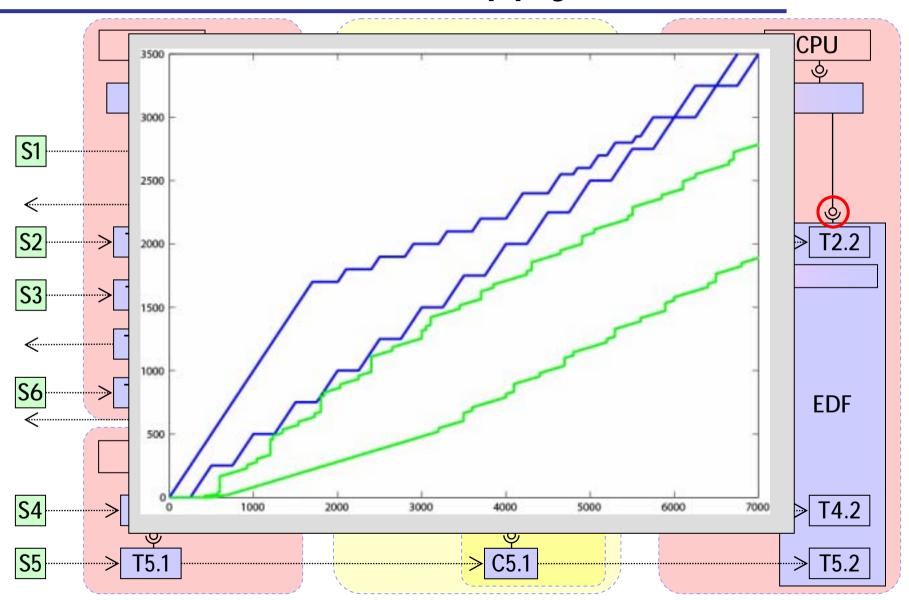

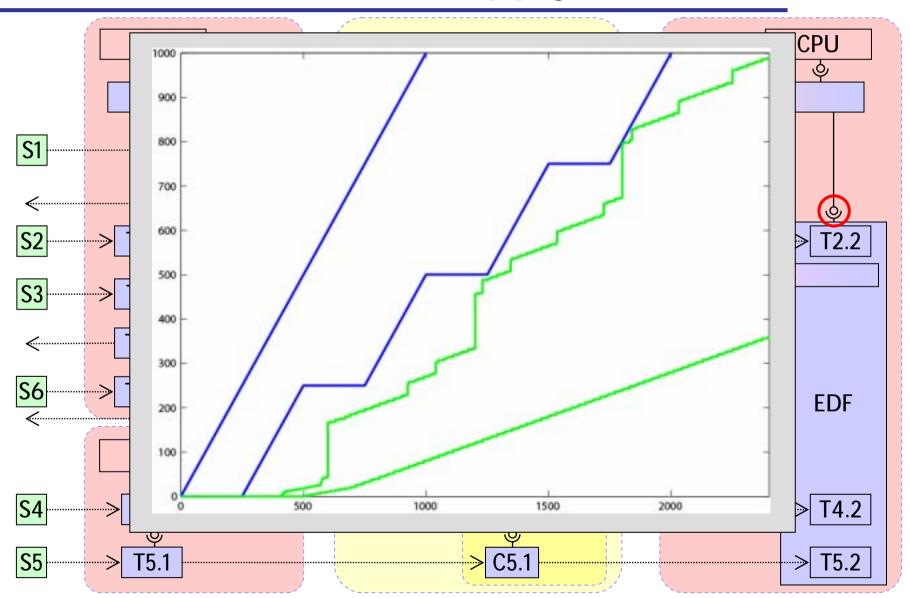

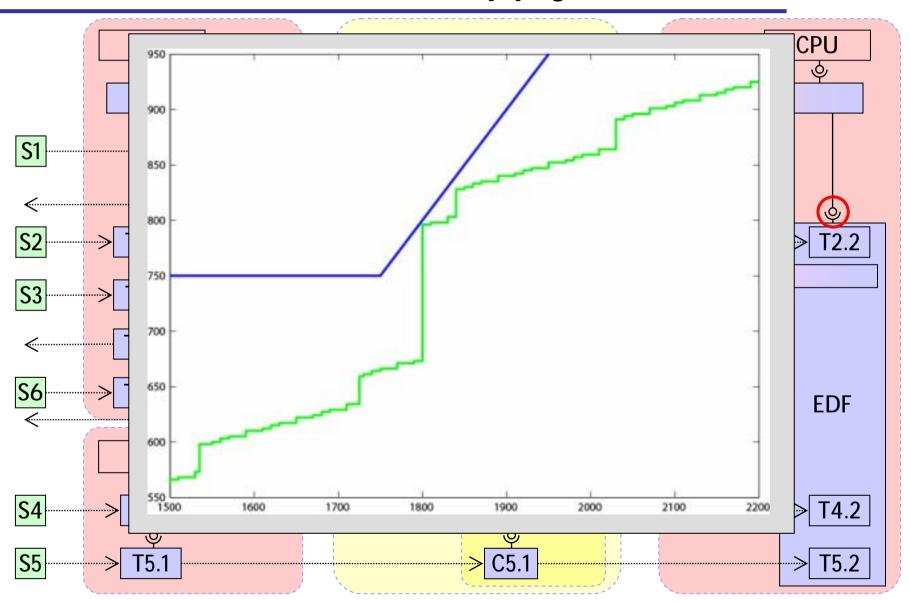

## Service Demand & Supply for EDF Block

## Service Demand & Supply for EDF Block

#### Service Demand & Supply for EDF Block

# System Analysis Time

- 10 seconds

- Pentium Mobile 1.6 GHz

- Matlab 7 SP2

- RTC Toolbox

## Outline

- Motivation / Problem Statement

- Modular Performance Analysis

- MPA Case Study

- Real-Time Interfaces / Interface-Based Design

- IBD Case Study

- Efficient Computation and Tool Support

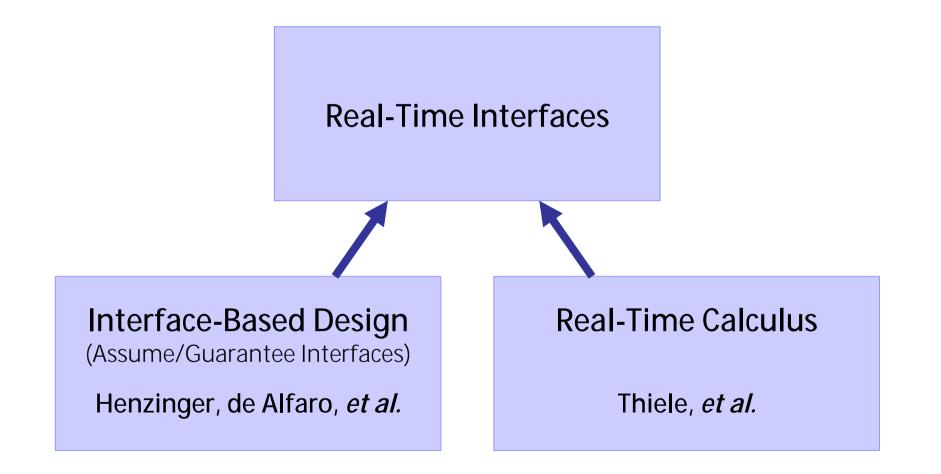

#### **Real-Time Interfaces**

# **Component-Based Design**

#### Schedulable?

Swiss Federal Institute of Technology 1. Design

#### 2. Analysis

- Given: *all* components, their interconnections structure and all inputs from environment

- Question: do the components work together properly?

# **Component-Based Design**

#### 1. Design and Composition

- Given: *some* components, their interconnection structure and some inputs from environment

- Questions: Is there the chance that the components *work together properly*? What are the *assumptions* towards the environment? How can I *change the environment* such that the components still work together?

# **Applications of Real-Time Interfaces**

- Interface-Based Design:

- Find minimum processor speed for complex systems with mixed hierarchical scheduling.

- Find optimal TDMA slot and cycle length allocations.

- Specify maximum allowable input stream rates.

- ...

- Interface-Based Schedulability Analysis

- On-Line Service & Load Adaption

- On-Line Admission Tests

## Outline

- Motivation / Problem Statement

- Modular Performance Analysis

- MPA Case Study

- Real-Time Interfaces / Interface-Based Design

- IBD Case Study

- Efficient Computation and Tool Support

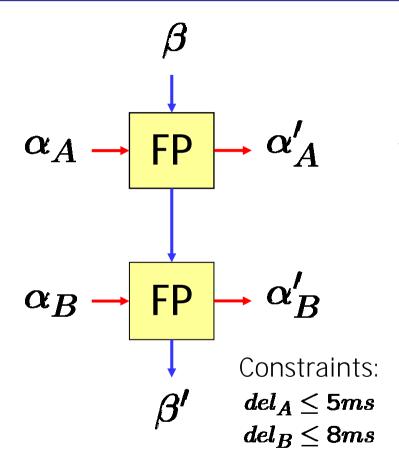

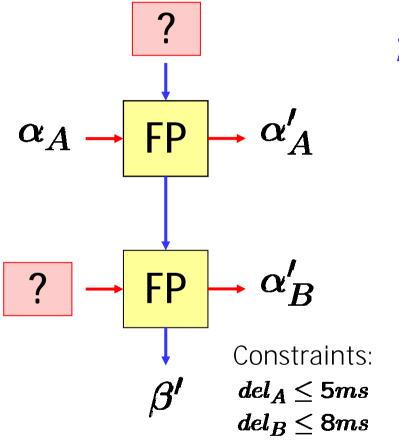

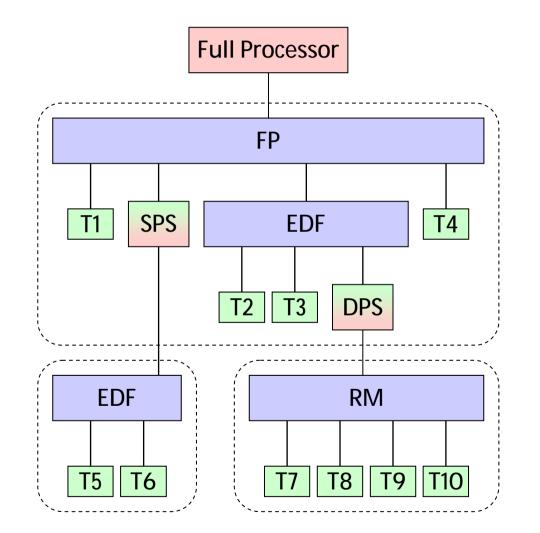

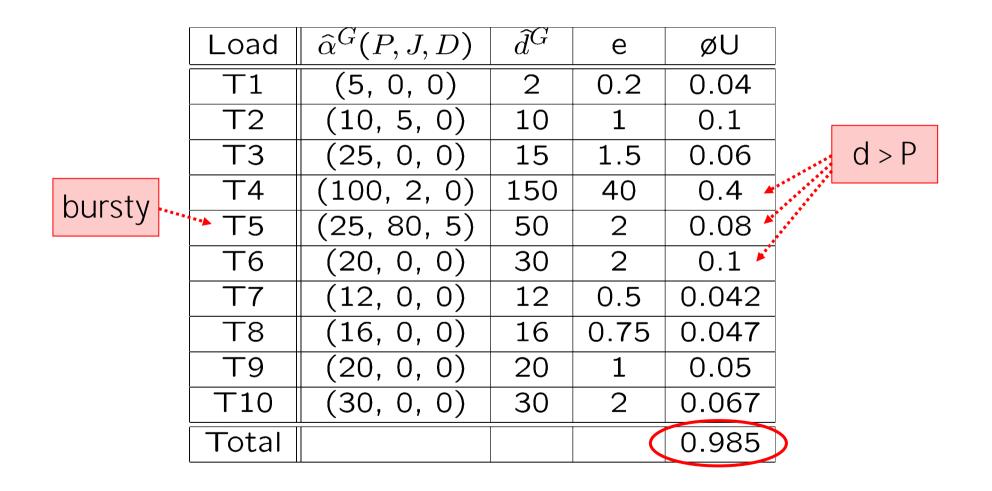

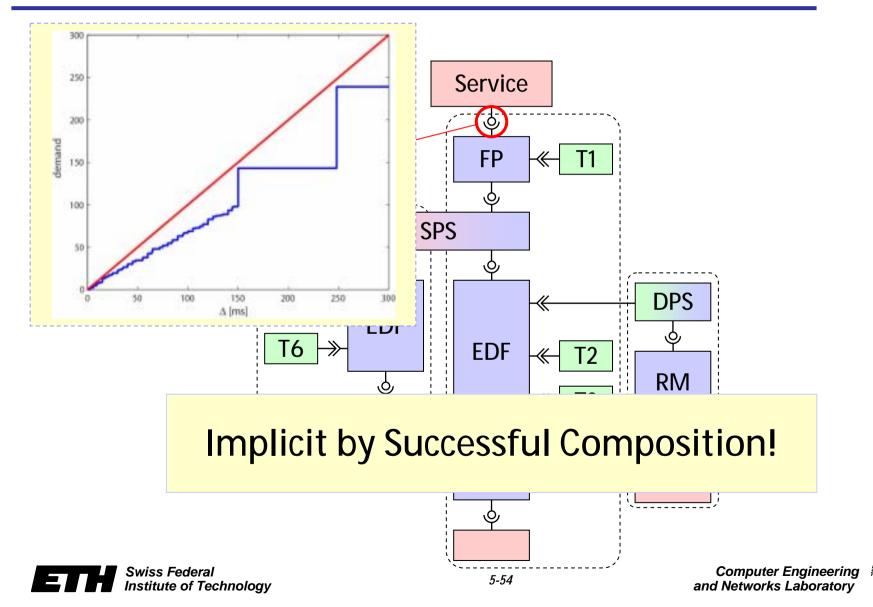

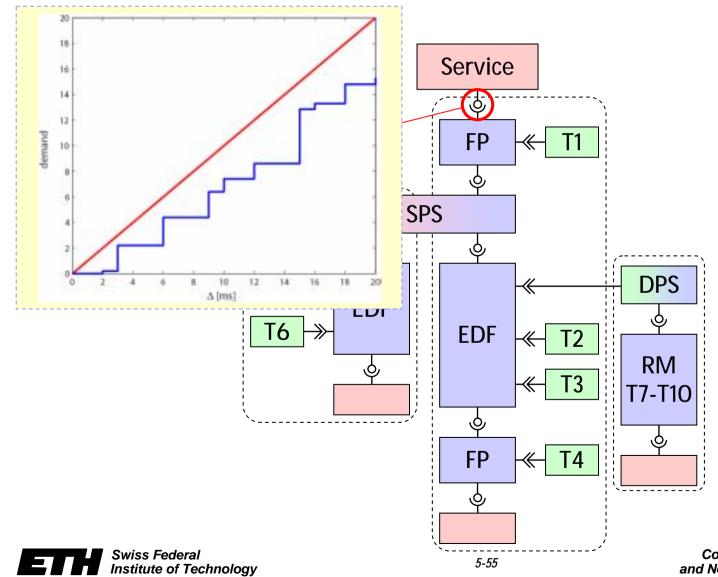

# A System with Complex Scheduling...

- 10 Tasks

- with jitter

- with bursts

- deadline = period

- deadline < period

- deadline > period

#### **3 Scheduling Policies**

- Rate Monotonic

- Earliest Deadline First

- Fixed Priority

Hierarchical Scheduling Static & Dynamic Polling Servers

Total Utilization: 98.5%

#### **Real-Time Load Specification**

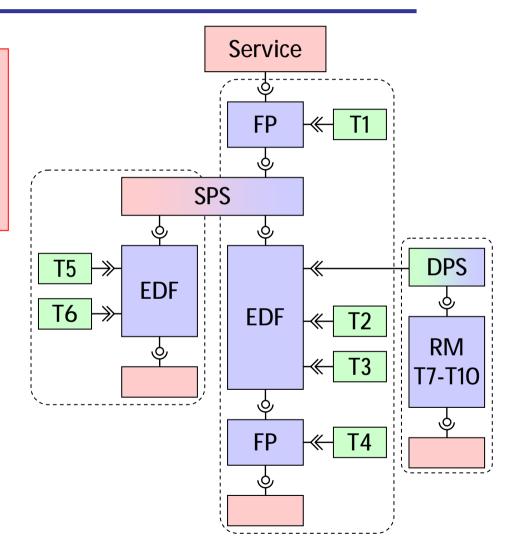

#### ... and its Real-Time Interface Model

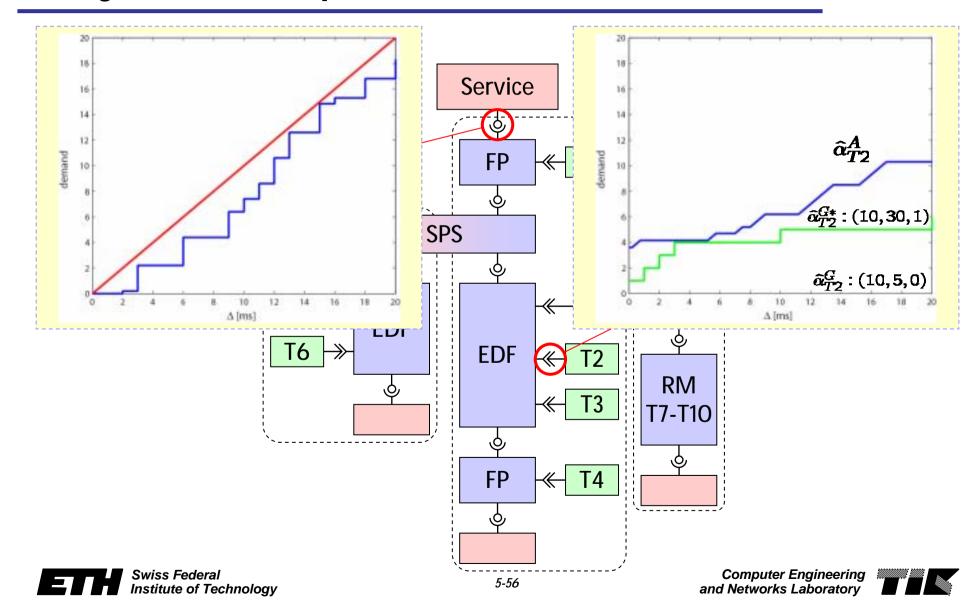

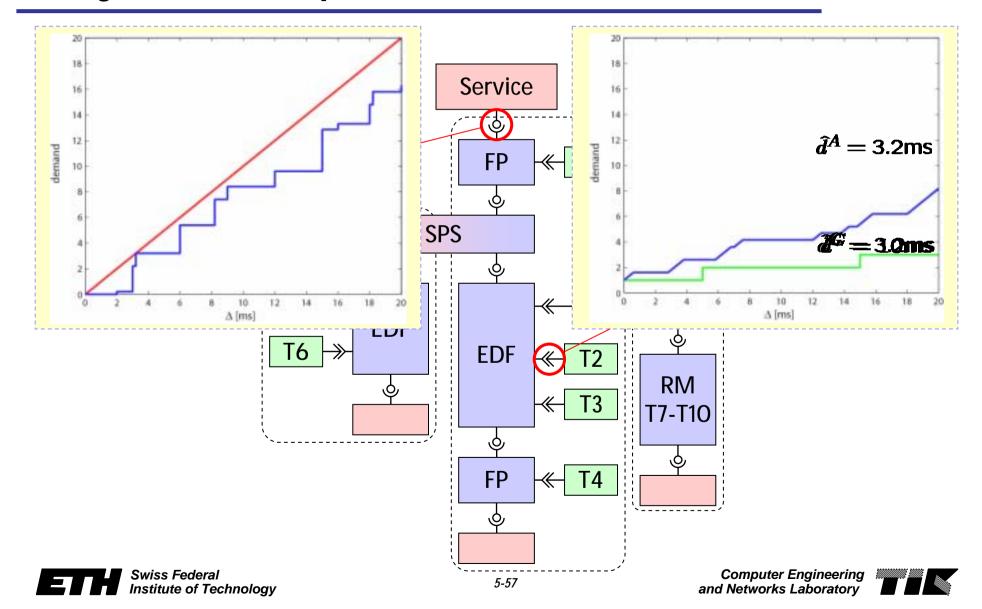

Combining RTC with Assume/Guarantee Interfaces

Constraint propagation!

# Schedulability Analysis

# Schedulability Analysis

Computer Engineering and Networks Laboratory

#### System Adaption I: Burstiness of T2

#### System Adaption II: Deadline of T2

# System Analysis Time

- <1second</pre>

- Pentium Mobile 1.6 GHz

- Matlab 7 SP2

- RTC Toolbox

## Outline

- Motivation / Problem Statement

- Modular Performance Analysis

- MPA Case Study

- Real-Time Interfaces / Interface-Based Design

- IBD Case Study

- Efficient Computation and Tool Support

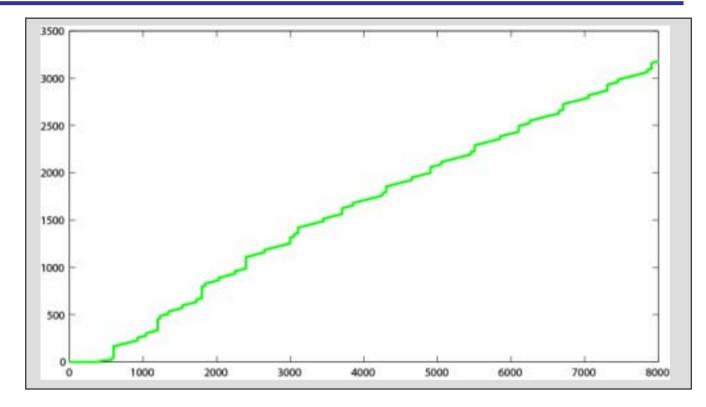

## An Efficient Curve Representation

A curve is defined by:

- a start segment of arbitrary length & form

- a *periodically repeated segment* of arbitrary length & form

Swiss F Institute

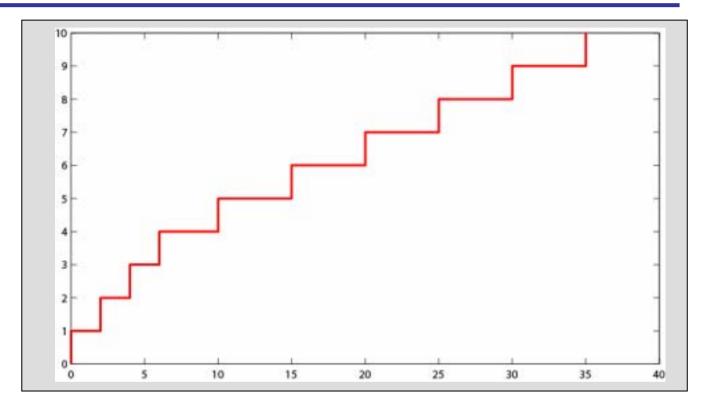

# Complex Start Segment ...

A curve is defined by:

- a start segment of arbitrary length & form

- a *periodically repeated segment* of arbitrary length & form

Swiss Fee Institute o

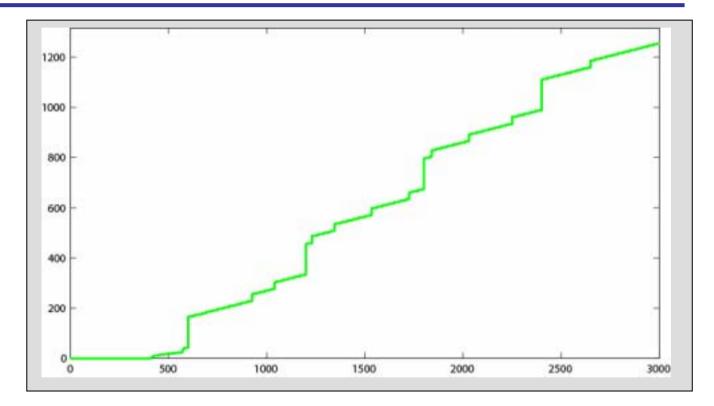

#### ... + Complex Periodic Segment ...

A curve is defined by:

- a start segment of arbitrary length & form

- a *periodically repeated segment* of arbitrary length & form

Swiss F Institute

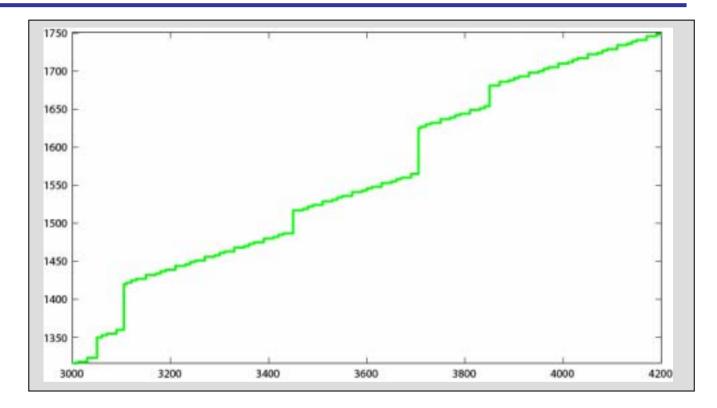

#### ... = Complex Curve (<sup>EDF Service Demand of</sup>) the IBD Case Study

A curve is defined by:

- a start segment of arbitrary length & form

- a *periodically repeated segment* of arbitrary length & form

## **RTC Toolbox**

| Matlab Command Line                  | Simulink    |

|--------------------------------------|-------------|

| RTC Toolbox                          |             |

| MPA Library                          | RTI Library |

| Min-Plus/Max-Plus Algebra Library    |             |

| Matlab / Java Interface              |             |

| Java API                             |             |

| Min-Plus/Max-Plus Algebra, Utilities |             |

| Efficient Curve Representation       |             |

#### **RTC Toolbox: Version 0.9 Released**

#### **RTC Toolbox: Simulink Frontend**

Computer Engineering and Networks Laboratory

# Acknowledgement

- Collaborators:

- Ernesto Wandeler

- Samarjit Chakraborty

- Simon Künzli

- Alexander Maxiaguine

- Funding:

- SNF, KTI, MEDEA+/SPEAC, ARTIST2 NOE