## CPU vs. outside CPU

- · WCET Research too focused on modelling the CPU

- But systems have:

- DMA, sharing same memory

- DSP, sharing the same bus

- Arbitration to access other devices

- Memory management units

- Focus on the feature that have the largest impact, others can be "approximated".

- Cache has by far the largest impact

- Cache misses "looks" like HD Page faults!.

- Example (real HW):

- Cache hit = 2 cycles

- Cache miss = 40 cycles

- Cache miss together at worst instant with DMA transfer = 80 cycles

- But very unlikely to happen every time.

(C) Guillem Bernat 5

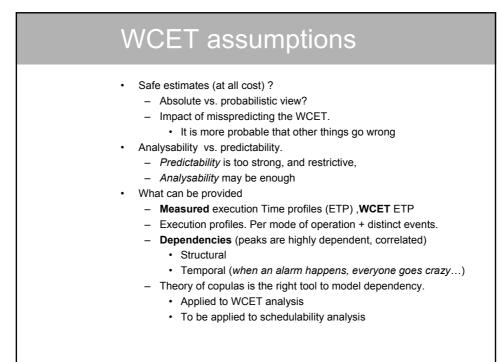

| WCET - Scheduling |                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •                 | <ul> <li>Typical assumptions on WCET <ul> <li>"task running in isolation, not interrupted, no preemptions"</li> </ul> </li> <li>Typical schedulability analysis assumptions: (<i>possibly all wrong</i>) <ul> <li><i>Ci</i> : WCET is known, constant and accurate.</li> <li><i>Ci</i> does not change over time <ul> <li>Mode changes</li> <li>HW impact (interrupts/ preemptions/)</li> </ul> </li> </ul></li></ul> |

|                   | <ul> <li>Actual execution time depends on schedule, circular dependency.</li> <li>Cooperative scheduling</li> <li>Cache Partitioning and Locking</li> <li>Locking interrupt code outside cache!</li> <li>Control of mode changes.</li> </ul>                                                                                                                                                                          |

|                   | <ul> <li>Strategies for scheduling:</li> <li>handle WCET overruns,</li> <li>Opportunities for gain time!!! LOTS (less on <i>slack time</i>)</li> <li>Careful with "Correlation" and dependencies</li> <li>Long execution times tend to happen together associated to single events. E.g. mode changes</li> </ul>                                                                                                      |

## Measured vs. Computed profiles

- Applicable to all resources

- Execution time (WCET)

- Cache misses

- Number of accesses to external buses, and other HW features

- Memory consumption

- "The best model of a system is the system itself"

- Observational systems:

- Trace Box

- · CPU support for observing behaviour system

- · CPU support for injecting HW test vectors

(C) Guillem Bernat 7