# ARTIST2

**Graduate Course on Embedded Control Systems**

April 3rd-7th, 2006 Prague, Czech Republic

Student

handouts

Organized by Zdeněk Hanzálek Department od Control Engineering Faculty of Electrical Engineering Czech Technical University in Prague

### **Program of Graduate Course on Embedded Control Systems**

### Department of Control Engineering, FEE, CTU Prague

### Karlovo náměstí 13, Building E, Room K112

### Monday 3<sup>rd</sup> of April

- 8:00 Registration

- 8:30 M1 Motivation and examples, Bengt Eriksson and Martin Torngren, 1.5 hour (KTH)

- 10:00 Coffee

- 10:15 M2 Control issues, Pedro Albertos, 2 hours (UPVLC)

- 12:15 Lunch

- 13:45 M3 RT issues, Alfons Crespo, 2 hours (UPVLC)

### Tuesday 4<sup>th</sup> of April

- 9:00 T1 Kernels and safe (back-up) operation, Pedro Albertos and Alfons Crespo, 1 hour (UPVLC)

- 10:00 Coffee

- 10:15 T2a Control design practical issues principles, Bengt Eriksson, 1 hour (KTH)

- 11:15 T2b Control design practical issues models, Jindrich Fuka, Jiri Roubal, 1 hour (laboratories K23 and K26 - CTU)

- 12:15 Lunch

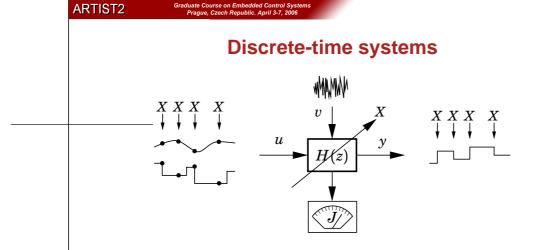

- 13:45 T3 Integrated control design and implementation, Karl-Erik Arzen and Anton Cervin, 2 hours (LTH)

### Wednesday 5<sup>th</sup> of April

- 8:00 W1 Control of Computing Systems, Karl-Erik Arzen and Anton Cervin, 2 hours (LTH)

- 10:00 Coffee

- 10:15 W2 Jitterbug and Truetime, Karl-Erik Arzen and Anton Cervin, 2 hours (laboratory K2 – LTH)

- 12:15 Lunch

- 13:45 W3 ECS Deployment, Bengt Eriksson and Martin Torngren, 2 hours (KTH)

### Thursday 6<sup>th</sup> of April

- 8:00 Th1 Off-line scheduling, Zdenek Hanzalek, 2 hours (CTU)

- 10:00 Coffee

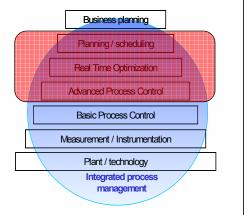

- 10:15 Th2 Platform for Advanced Process Control and Real Time Optimization, Vladimir Havlena and Jiri Findejs, 2 hours (Honeywell Laboratory Prague)

- 12:15 Lunch

- 13:45 Th3, RT practical issues, Michal Sojka and Ondrej Spinka, 2 hours (laboratory K09 - CTU)

### Friday 7<sup>th</sup> of April

- 8:00 F1, Torsche Matlab scheduling toolbox, Premysl Sucha and Michal Kutil, 2 hours (laboratory K2 - CTU)

- 10:00 Coffee

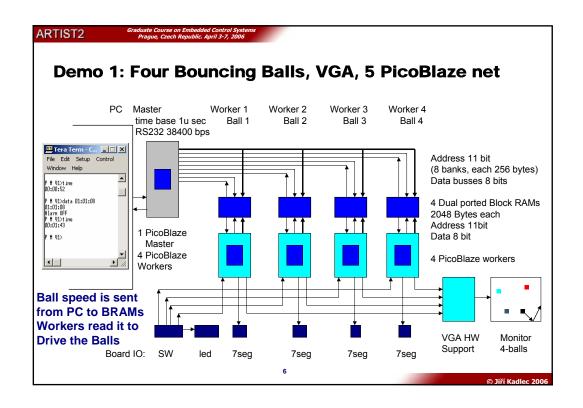

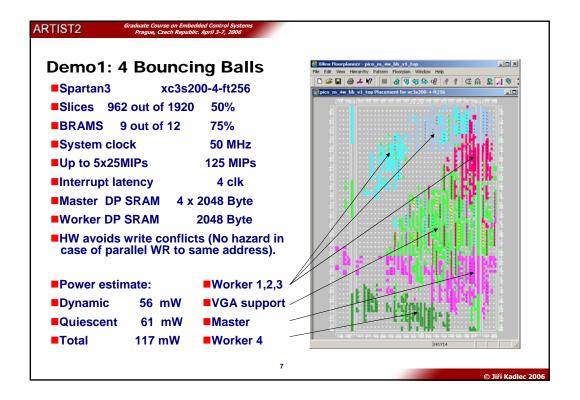

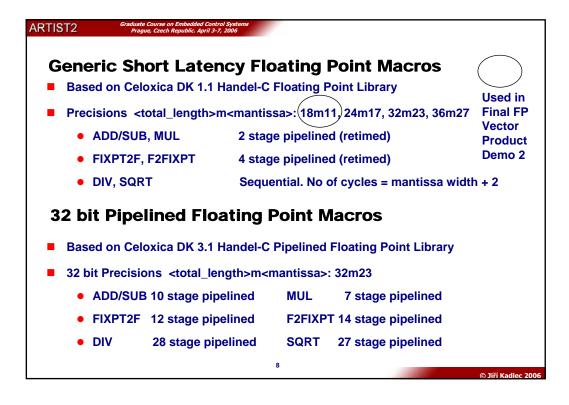

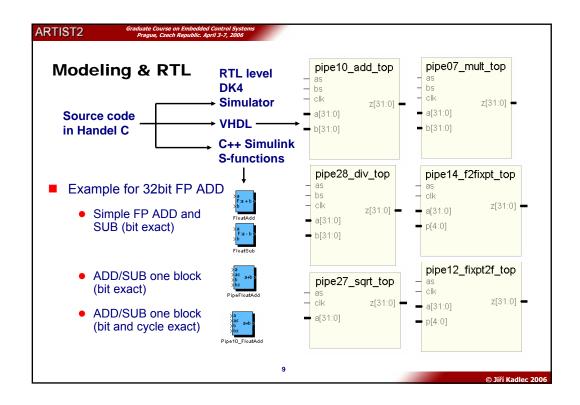

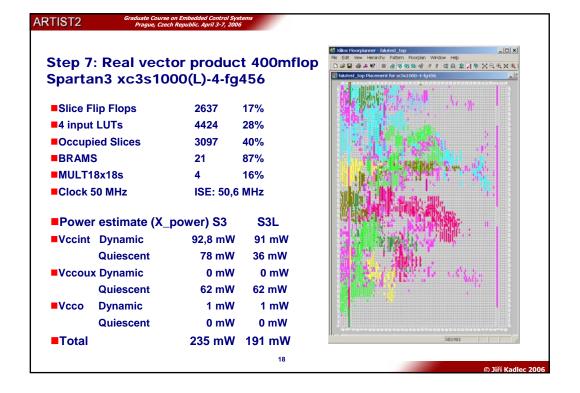

- 10:15 F2, Implementing Floating-Point DSP and Control with PicoBlaze Processors, Jiri Kadlec, 2 hours (CTU)

- 12:15 Closing remarks and discussion

### M1 Motivation and examples, Bengt Eriksson and Martin Torngren, 1.5 hour (KTH)

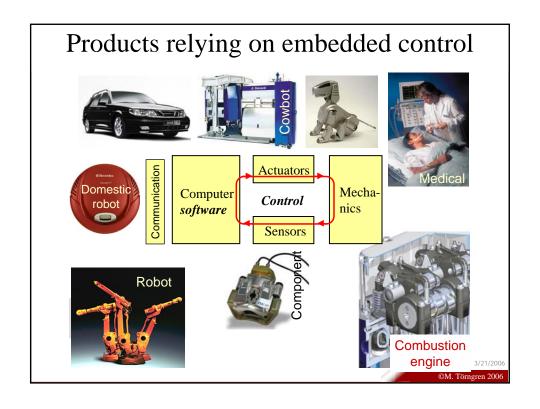

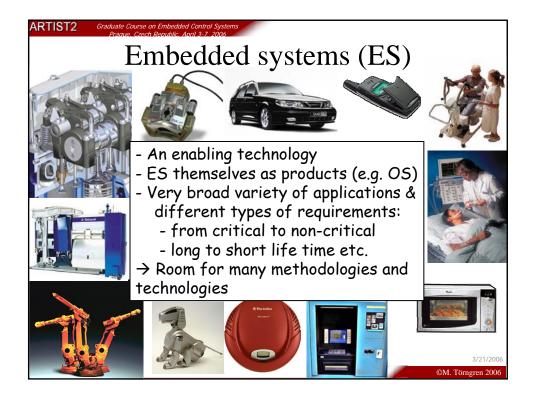

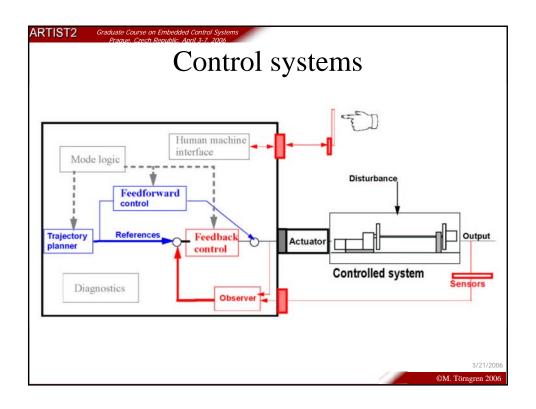

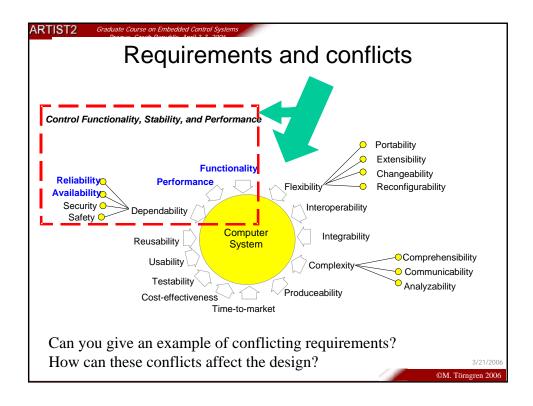

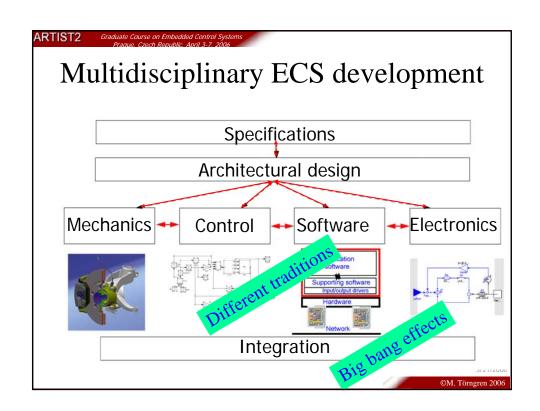

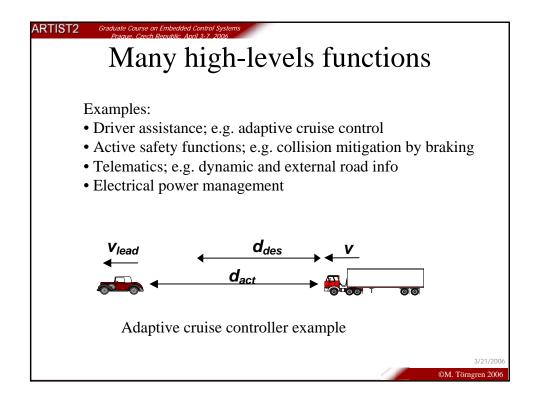

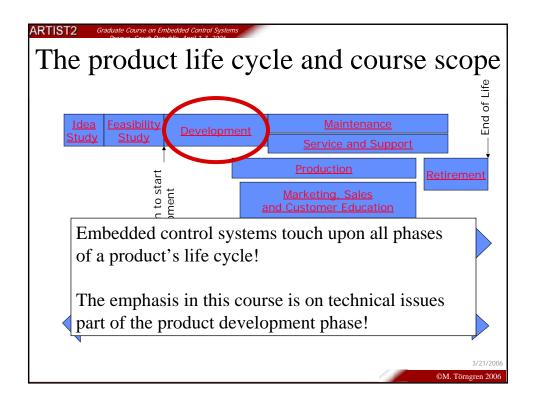

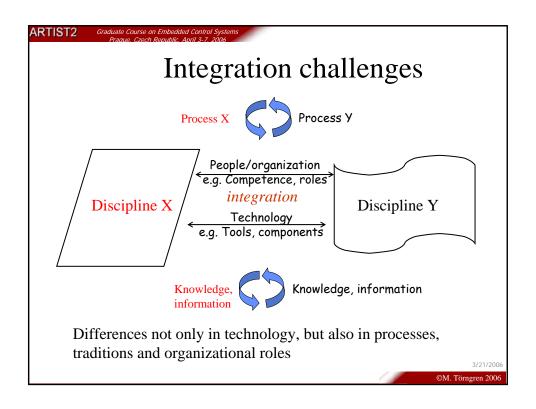

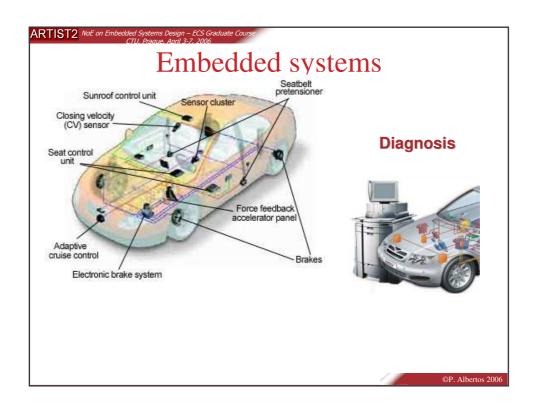

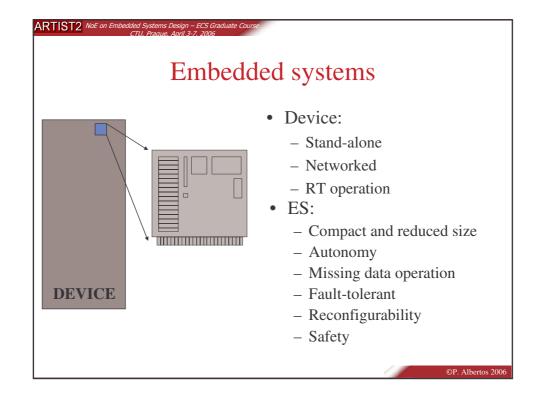

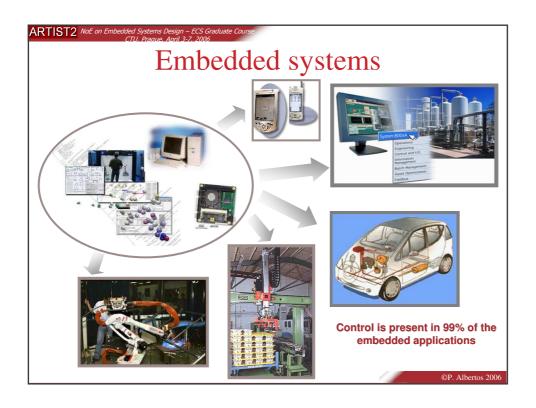

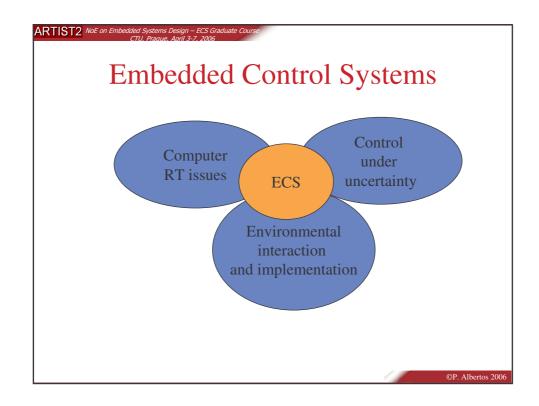

In this introductory session, the general problem of the course will be presented and motivated. What Embedded systems (ES) are? What Embedded control systems (ECS) are? Why? Motivating examples: inverted pendulum, mobile robot, car safety control. Main issues in the design of ECS: typical requirements, conflicting requirements, design trade-offs, typical architectures, design parameters.

### M2 Control issues, Pedro Albertos, 2 hours (UPVLC)

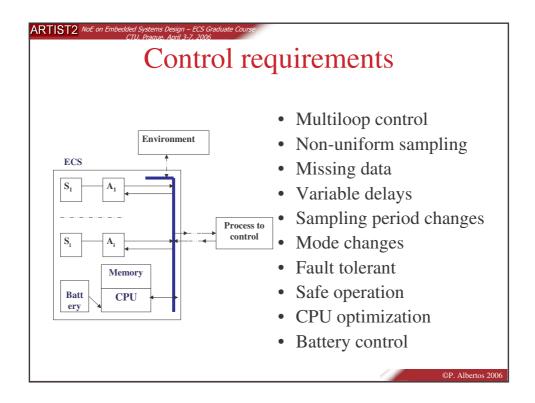

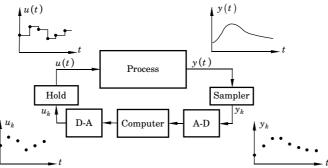

Real-time implementation of control algorithms in a multitasking environment involves a number of issues that should be taken into account. The unavoidable delays, both in computation and in data handling, the lost of data, the change of operation mode, the changes in sampling periods and the performance degrading are among the main issues to be considered. In this session, a review of these concepts for a general audience will be presented. The goal of this session would be to emphasize the relevance of these control design issues, to be strongly connected to the actual implementation of the control, to be discussed in the next sessions.

### M3 RT issues, Alfons Crespo, 2 hours (UPVLC)

The aim of this session is to introduce the most important concepts of ECS from the real-time (RT) systems perspective. The different types of RT tasks are introduced, and the importance of RT constraints is emphasized, especially in the context of control systems design. The central role of processor scheduling for guaranteeing RT constraints is motivated, and the main paradigms of RT scheduling are introduced. Fixed and dynamic priority scheduling methods are described, including temporal analysis methods. Resource usage and jitter control are also introduced. Finally, implementation approaches in view of the existing RT operating systems and programming languages technologies are discussed. The level of presentation of the topics is introductory, but a basic knowledge of operating systems, computer architecture, and programming in a high-level language is assumed.

# T1 Kernels and safe (back-up) operation, Pedro Albertos and Alfons Crespo, 1 hour (UPVLC)

ECS require to work in a variety of (unexpected) circumstances. The operating system (OS) should provide a number of basic options to guarantee the safe behaviour of ECS. In this session, a new set of operating services to provide the applications a higher control of faults and temporal constraints will be described. Some examples of this functionalities are: Execution timers, application defined scheduling, fault tolerant monitors, etc. From the control viewpoint, a hierarchical sorting of activities should be scheduled in agreement with the OS kernel to get the best, among the possible, control options. Safe (back-up) operation, basic control actions, optional and supervision are among the main issues to be discussed.

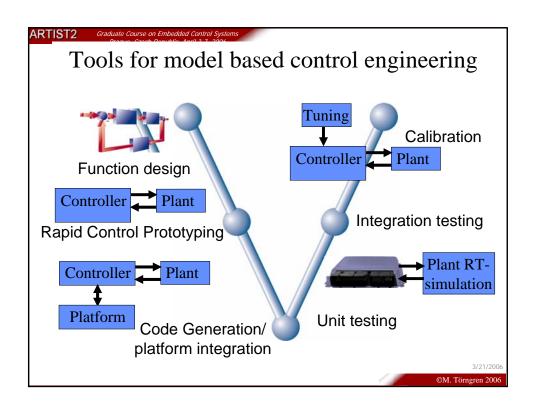

# T2 Control design practical issues – principles and models, Bengt Eriksson, Jindrich Fuka, Jiri Roubal, 2 hours (KTH, CTU)

Introductory and simple exercises about control design using CACD (computer aided control design) packages will allow a better insight into the RT control design algorithms. Moreover, using some simple rigs, the participants will get some hands-on control design approaches. Some principles will be demonstrated on laboratory models.

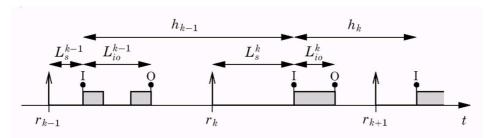

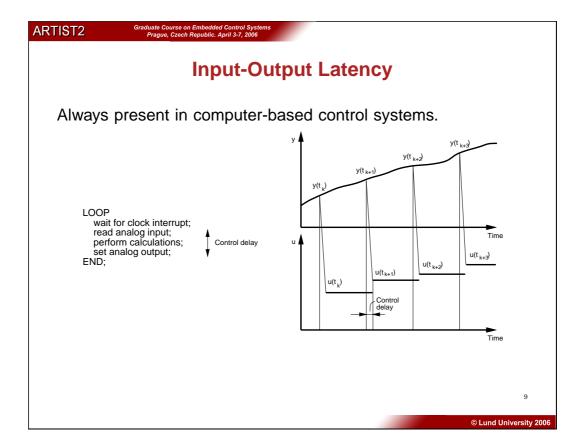

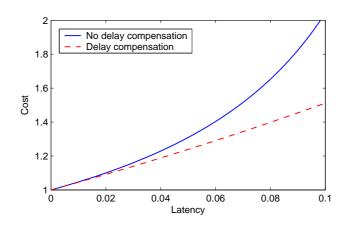

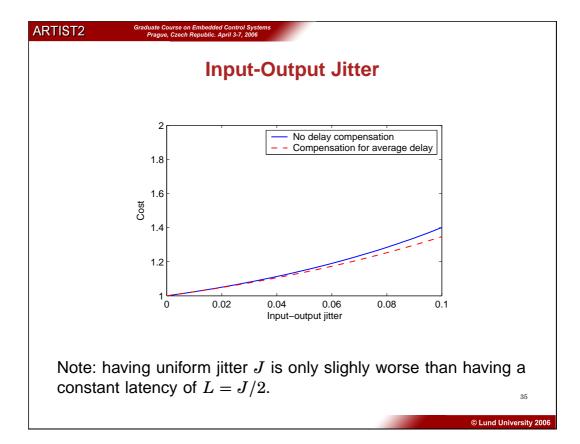

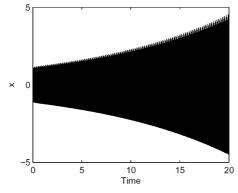

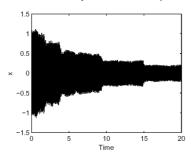

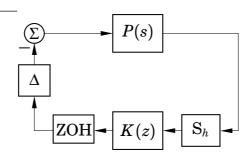

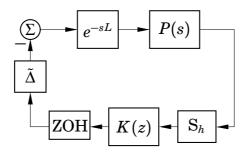

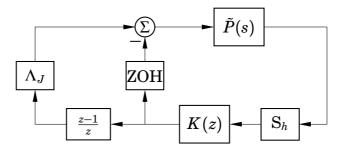

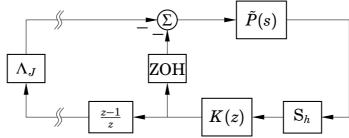

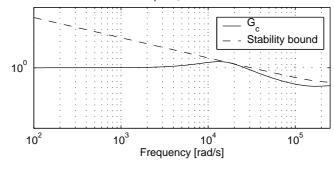

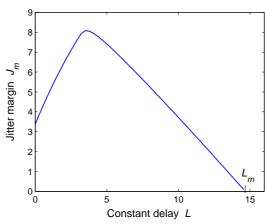

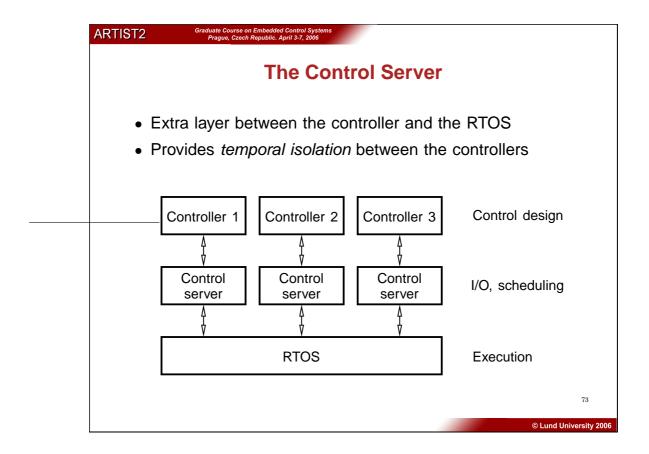

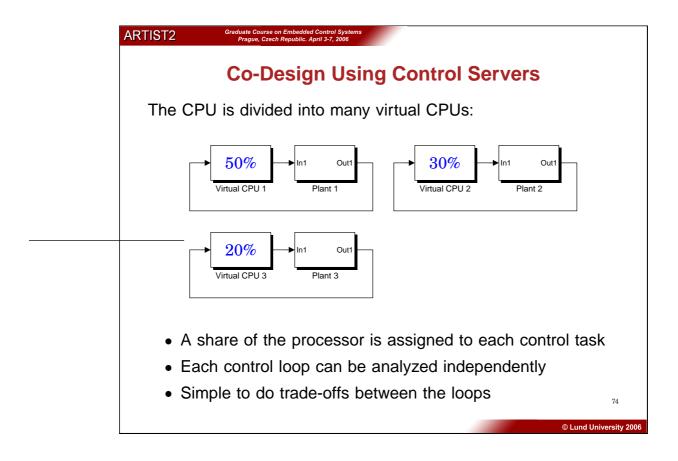

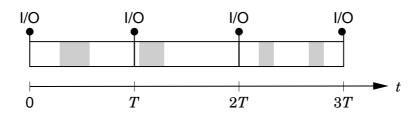

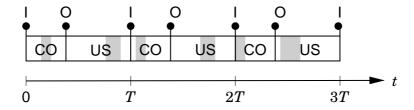

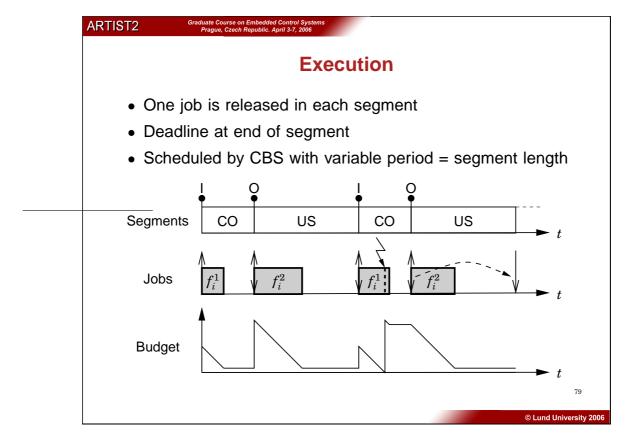

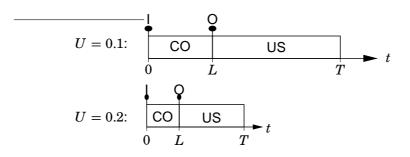

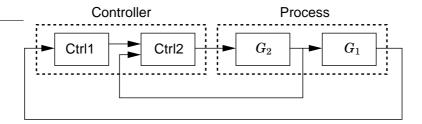

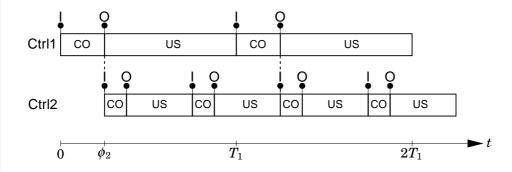

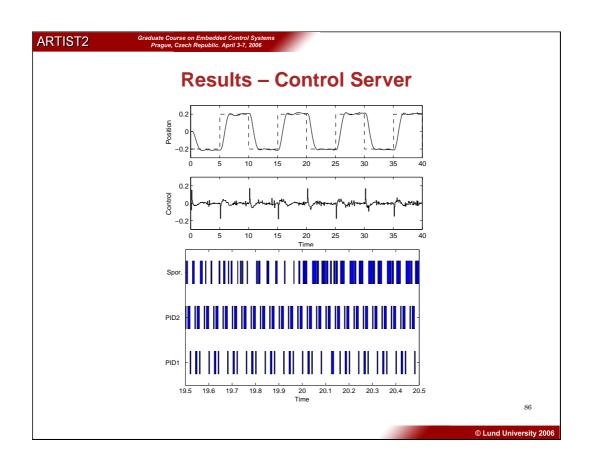

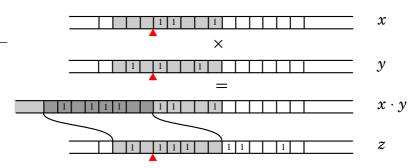

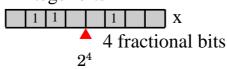

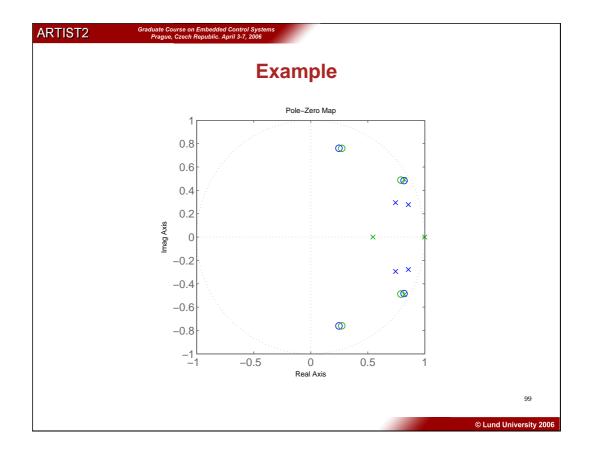

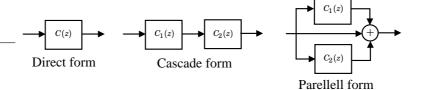

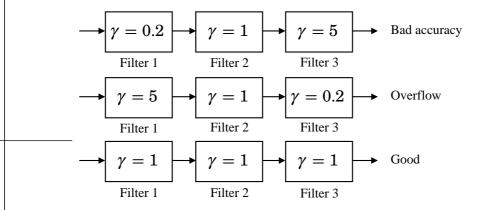

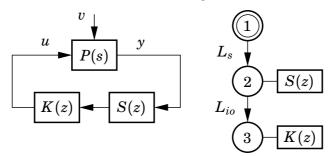

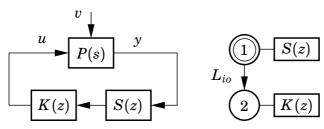

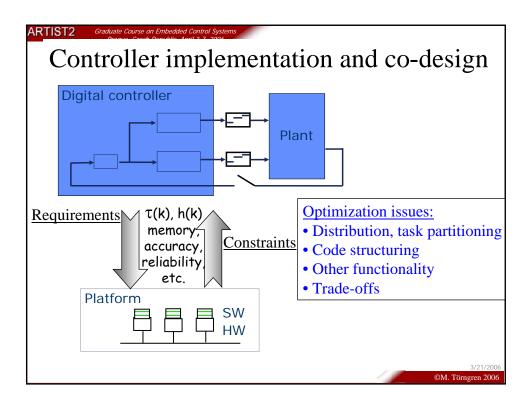

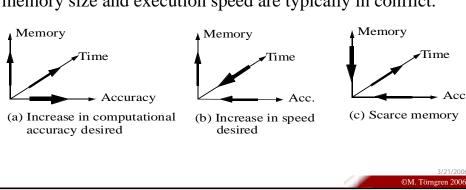

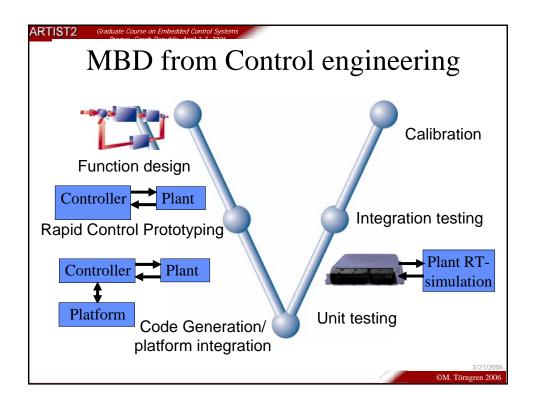

# T3 Integrated control design and implementation, Karl-Erik Arzen and Anton Cervin, 2 hours (LTH)

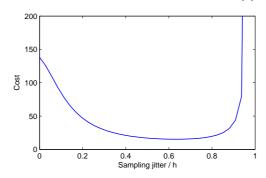

This session will focus on the interaction between the control design and control implementation. In embedded systems, floating point arithmetic is sometimes too costly. The problems associated with fixed point arithmetic are discussed. The implementation platform normally introduces input-output latencies due to computation and communication delays. The effects of this on control performance and how it can be compensated for will be discussed. Special emphasis will be given to the recent jitter margin concept. The implementation platform also introduces jitter in sampling intervals. This will also be discussed. The control server is a computational model for controller tasks that combines the benefits of static scheduling and dynamic event-based scheduling. Changing controller task parameters such as sampling periods on-line could sometimes be useful in order to adapt to changing conditions. The problems associated with this and the risk of switching induced instabilities will be discussed.

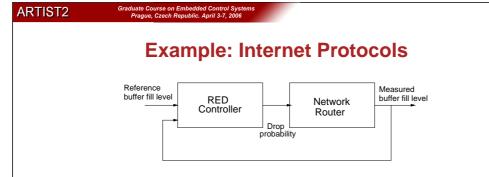

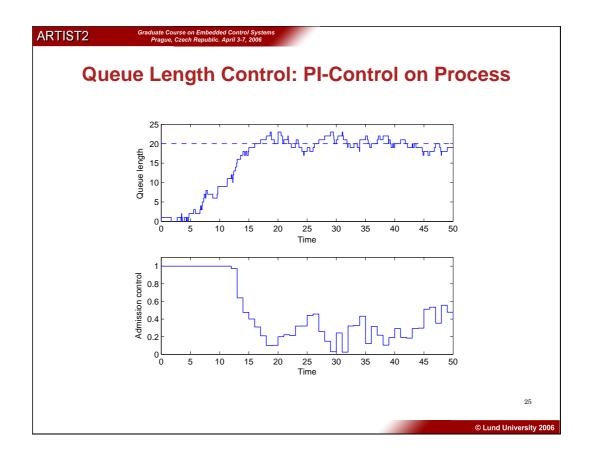

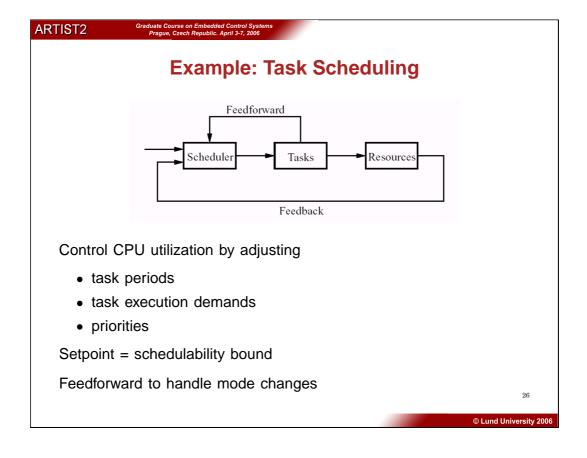

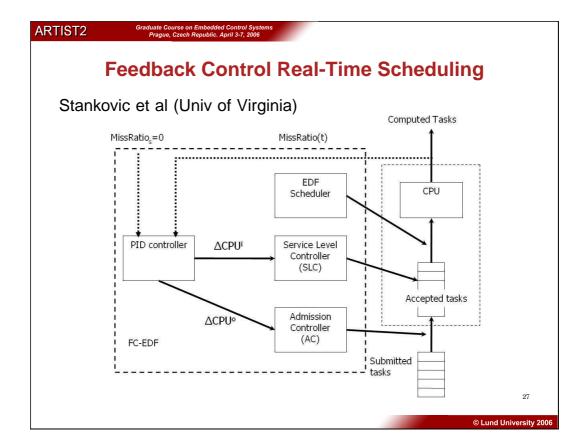

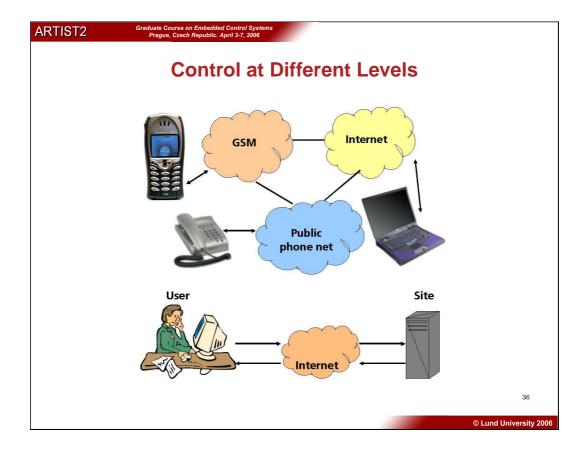

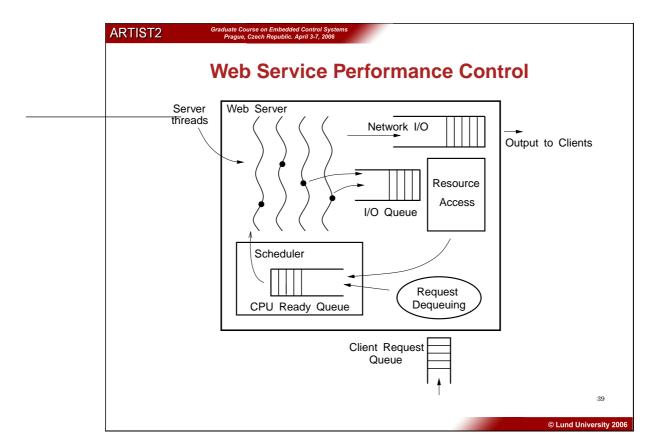

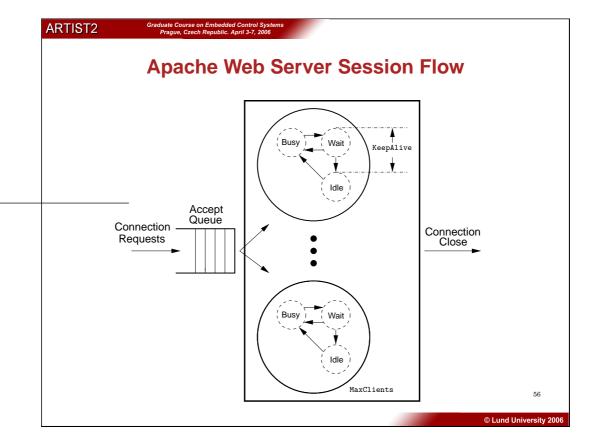

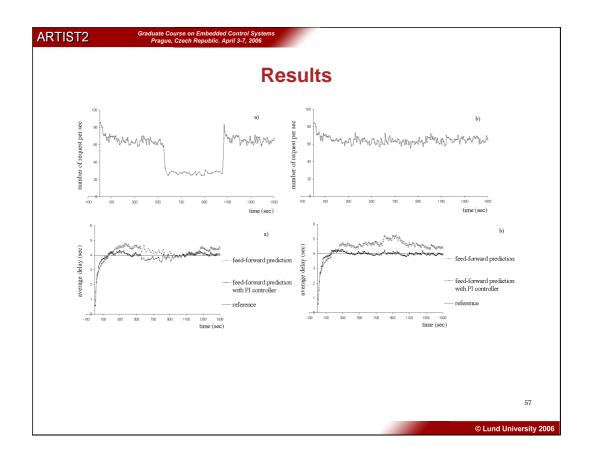

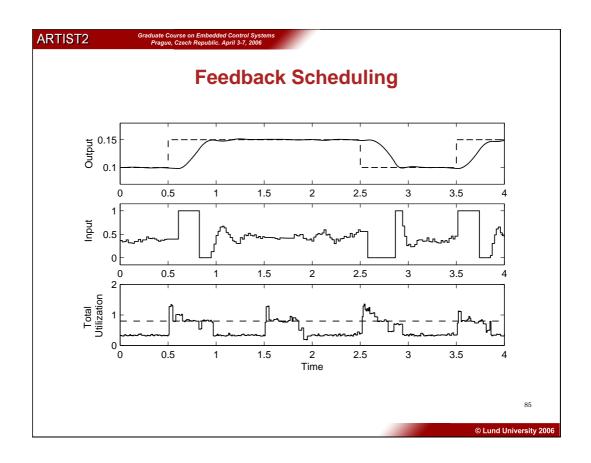

### W1 Control of Computing Systems, Karl-Erik Arzen and Anton Cervin, 2 hours (LTH)

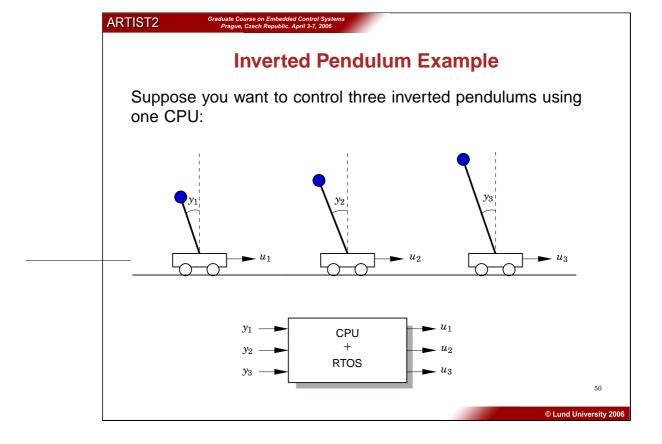

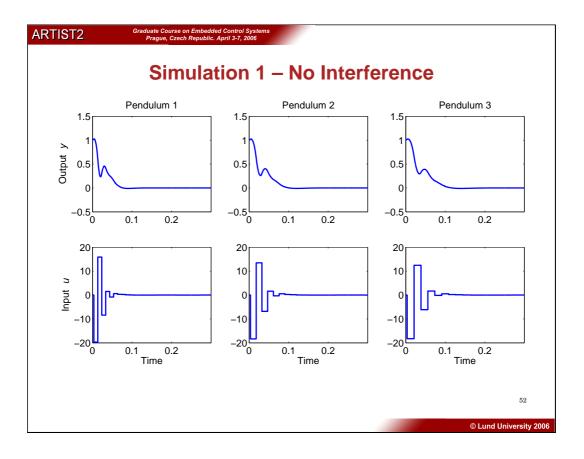

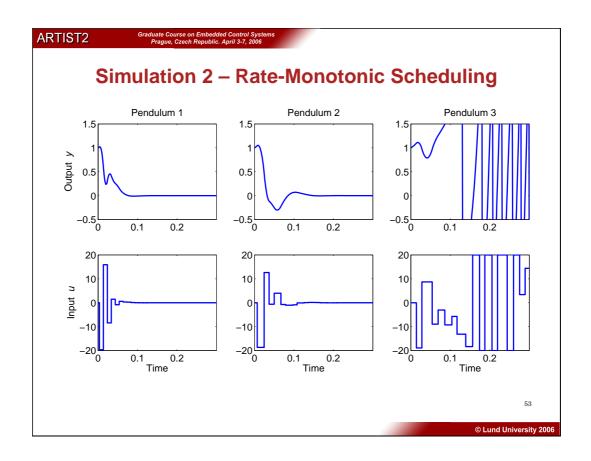

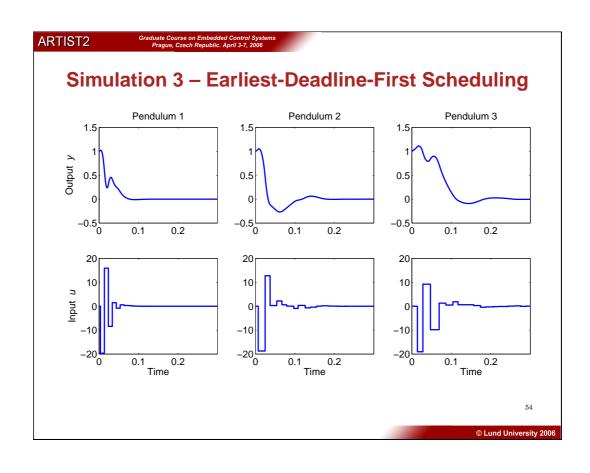

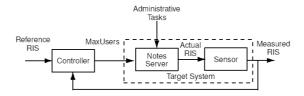

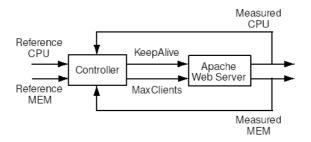

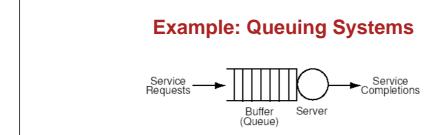

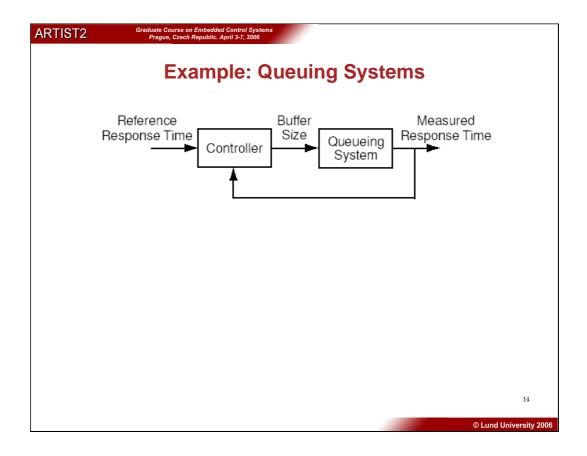

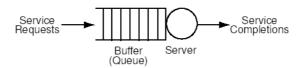

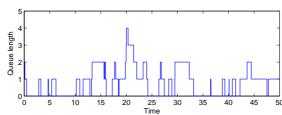

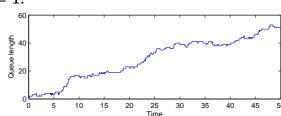

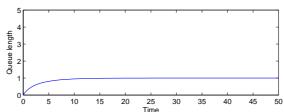

Using control-based approaches for modeling, analysis, and design of embedded computer and communications systems is currently receiving increased attention from the real-time systems community, as a promising foundation for controlling the uncertainty in large and complex real-time systems. The control-based approach has the potential to increase flexibility, while preserving dependability and efficiency. In this session we will give an overview of the work that is being done within the area with a special emphasis on two areas: Control of Web-servers and feedback scheduling of controller tasks. An inverted pendulum control example will illustrate some of the issues.

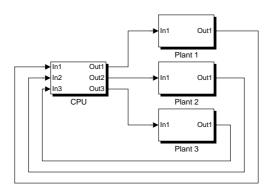

# W2 Jitterbug and Truetime, Karl-Erik Arzen and Anton Cervin, 2 hours (laboratory K2 – LTH)

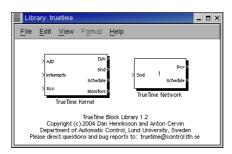

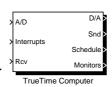

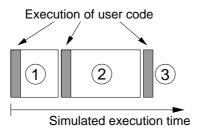

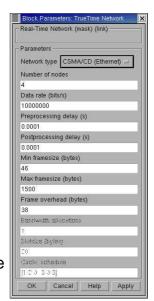

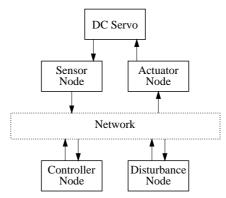

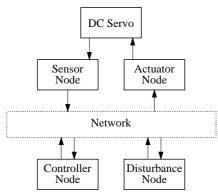

A hands-on session/exercise where the users will become familiar with the two co-design tools Jitterbug and TrueTime. Jitterbug is a MATLAB-based toolbox that computes a quadratic performance criterion for a linear control system under various timing conditions. Using the toolbox, one can easily and quickly assert how sensitive a control system is to delay, jitter, lost samples, etc., without resorting to simulation. The tool is quite general and can also be used to investigate jitter-compensating controllers, aperiodic controllers, and multi-rate controllers. TrueTime is a MATLAB/Simulink-based tool that facilitates simulation of the temporal behavior of a multitasking real-time kernel executing controller tasks. The tasks are controlling processes that are modeled as ordinary continuous-time Simulink blocks. TrueTime also makes it possible to simulate simple models of communication networks and their influence on networked control loops.

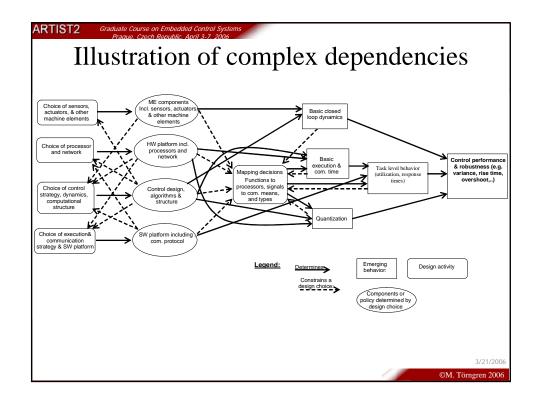

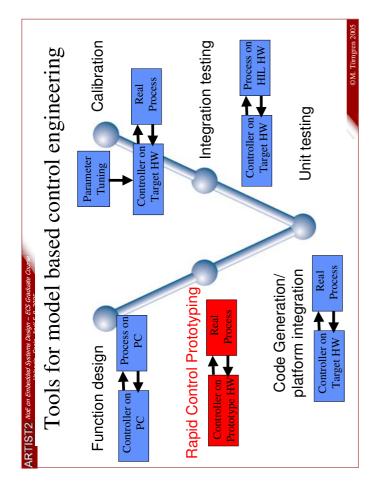

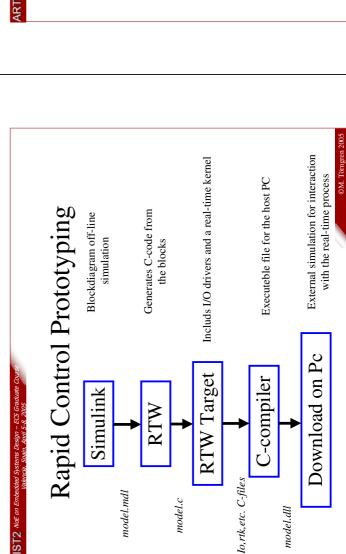

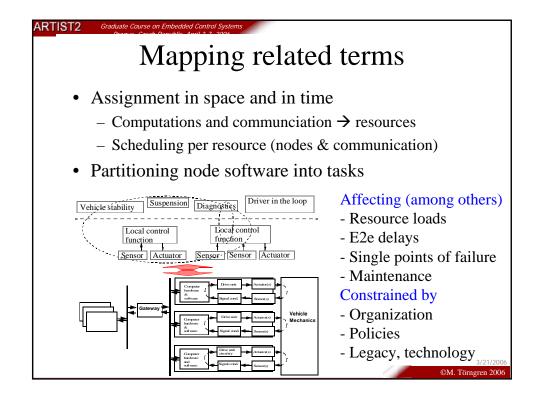

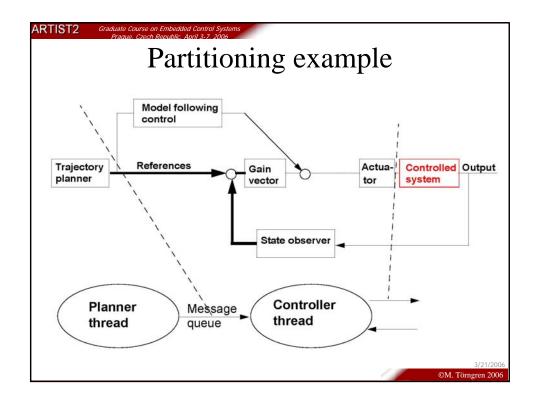

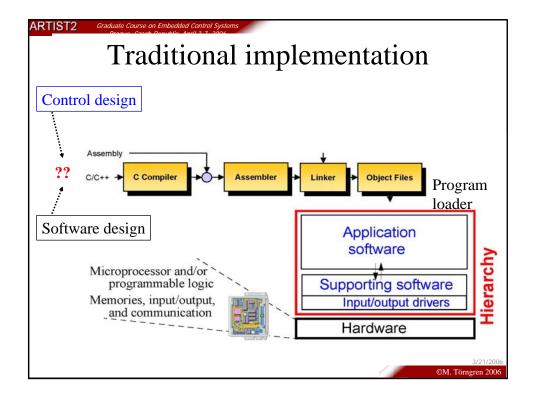

### W3 ECS Deployment, Bengt Eriksson and Martin Torngren, 2 hours (KTH)

The practical issues of ECS deployment will be discussed in this session, including: ECS implementation and platform selection (e.g. which type of OS?, which hardware?); OS configuration, components selection and loading (static vs dynamic OS types); Cross-compiling; Code generation; Verification and validation. A case study will illustrate the approach.

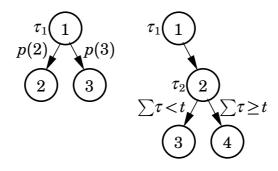

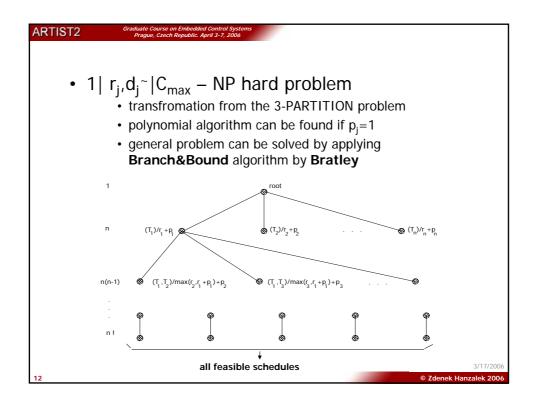

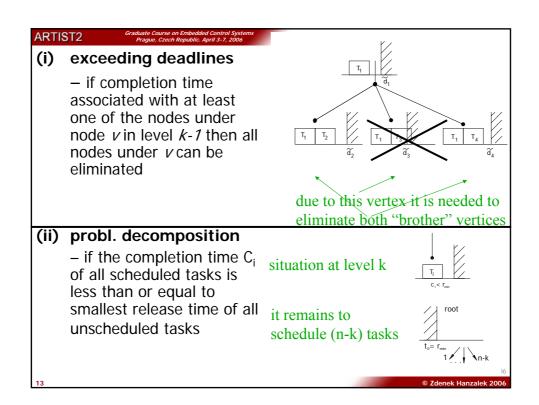

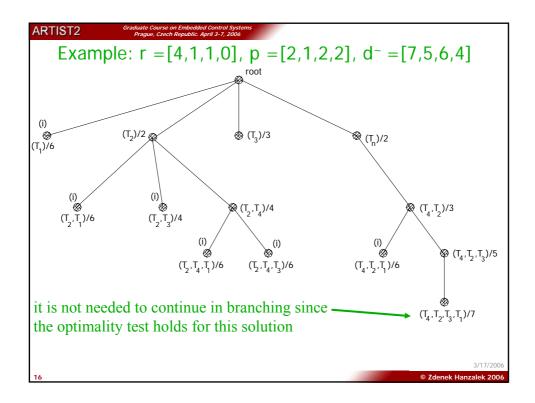

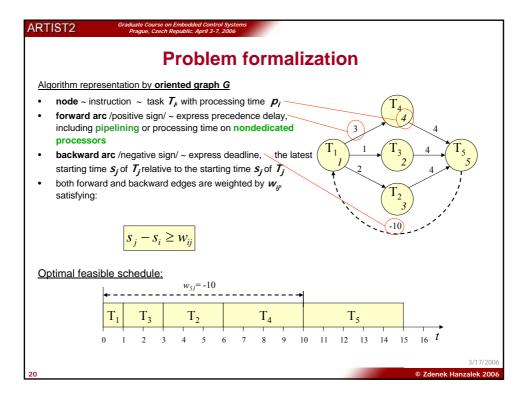

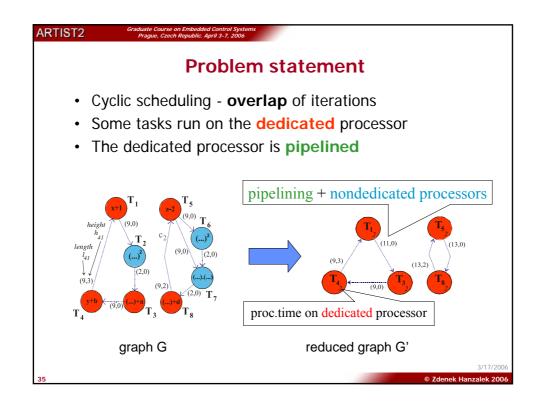

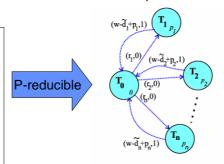

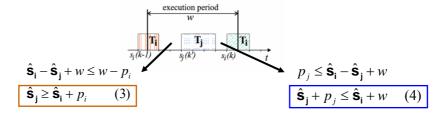

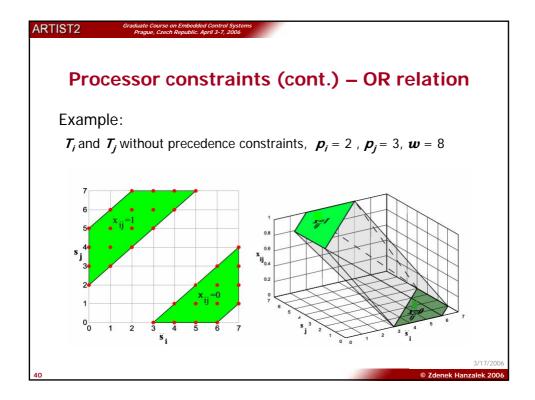

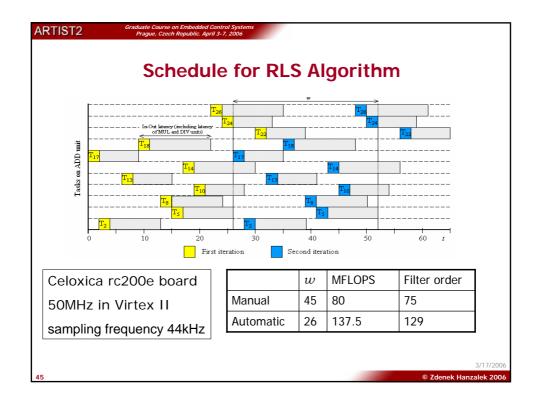

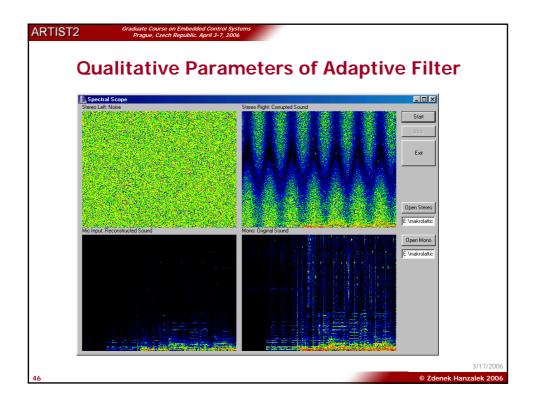

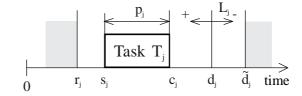

### Th1 Off-line scheduling, Zdenek Hanzalek, 2 hours (CTU)

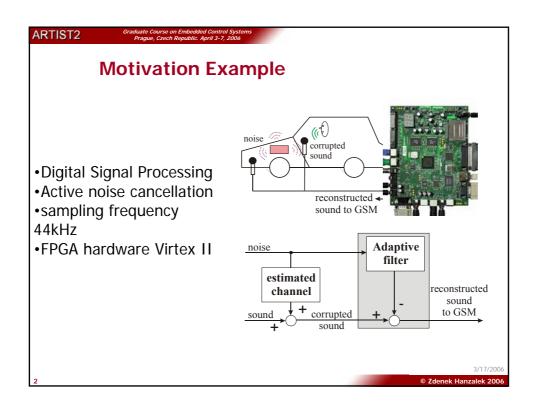

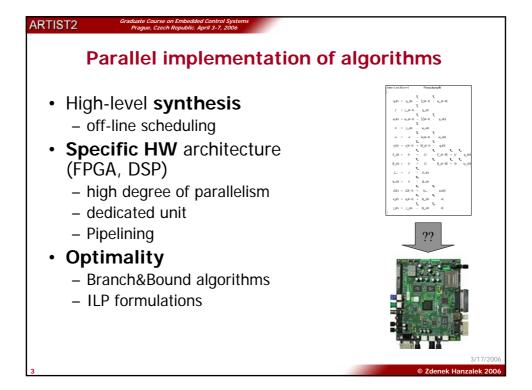

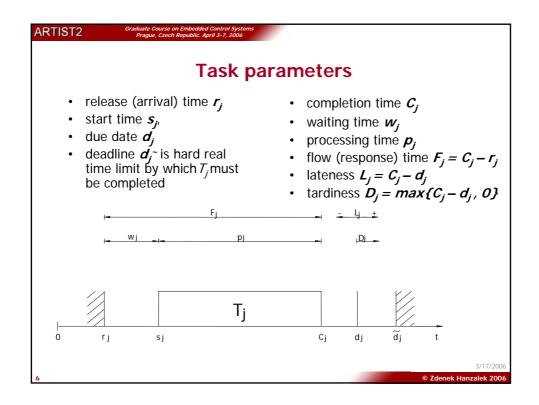

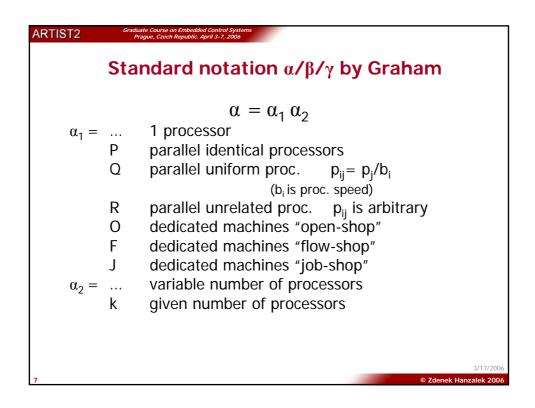

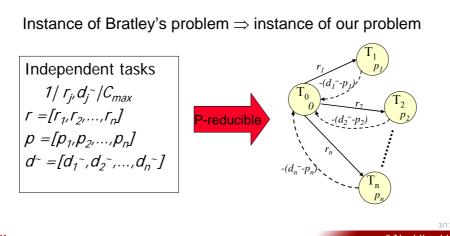

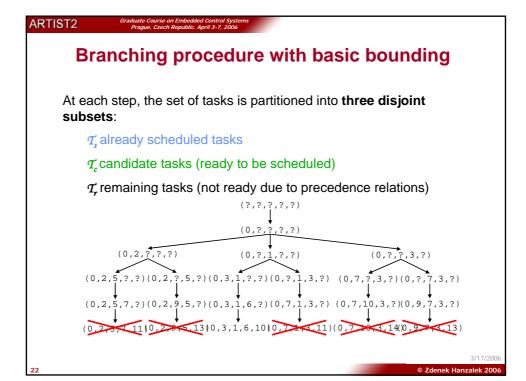

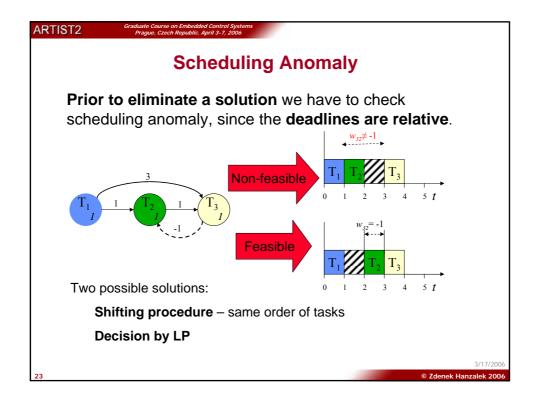

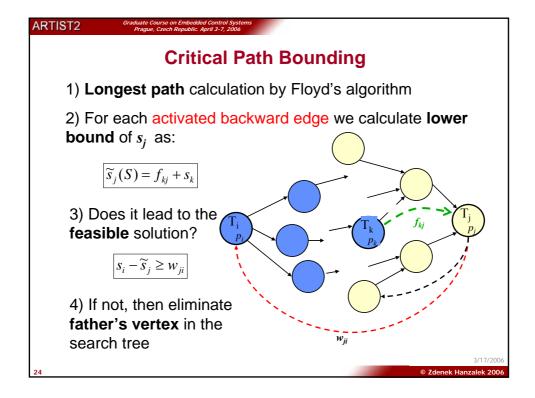

The objective of this course is to provide an overview of different off-line scheduling problems found in embedded systems. In order to classify the scheduling problems, we show

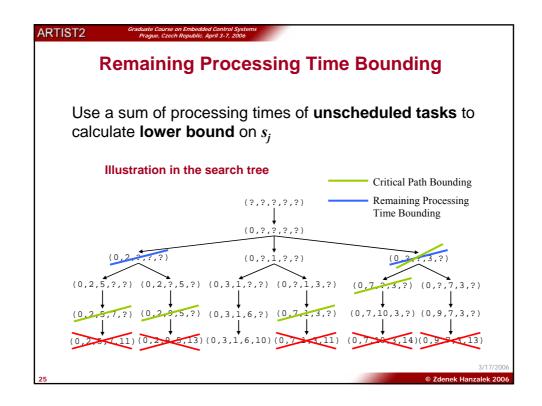

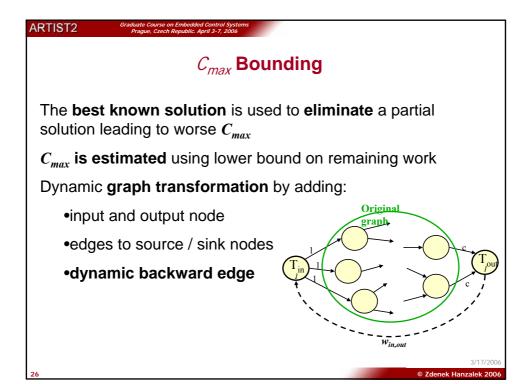

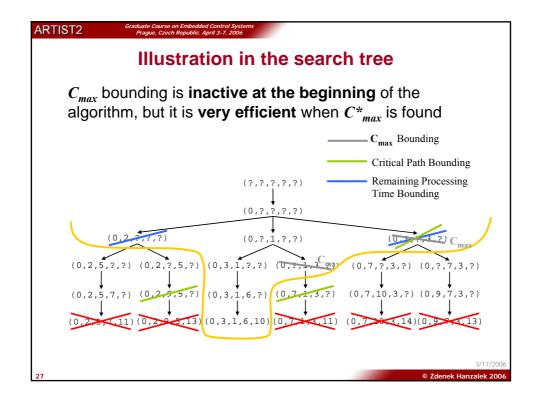

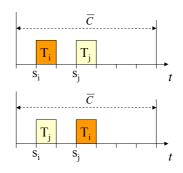

alpha|beta|gamma notation first. Then we develop several algorithms for real-time monoprocessor applications. Namely we show Bratley's branch&bound algorithm for Cmax optimization with release dates and deadlines and we underline main ideas of 0/1 programming solution for weighted completion time optimization with precedence constraints. The class of monoprocessor problems is concluded by minimization of maximum latency, i.e. Earliest Due-Date First algorithm and Earliest Deadline First algorithm. Finally we give an insight into the scheduling on dedicated processors and we provide examples on code synthesis for FPGA.

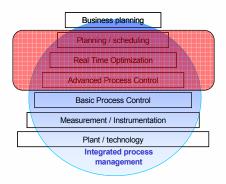

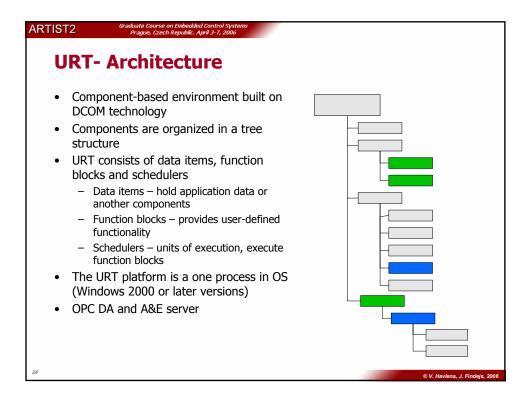

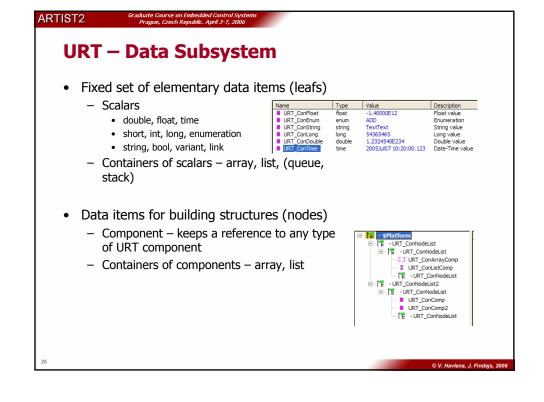

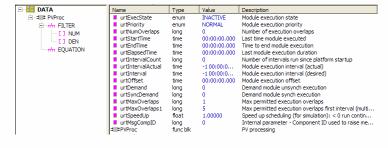

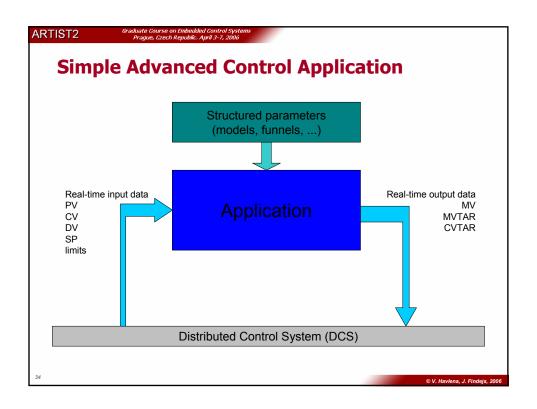

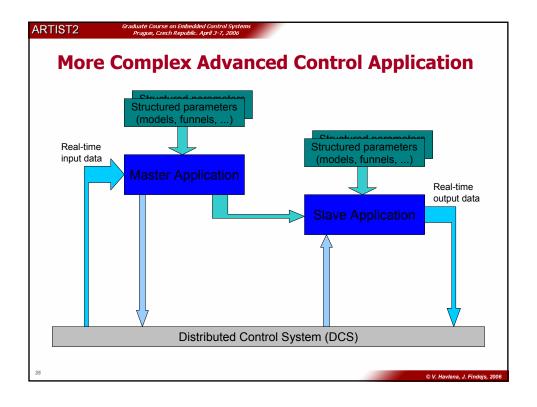

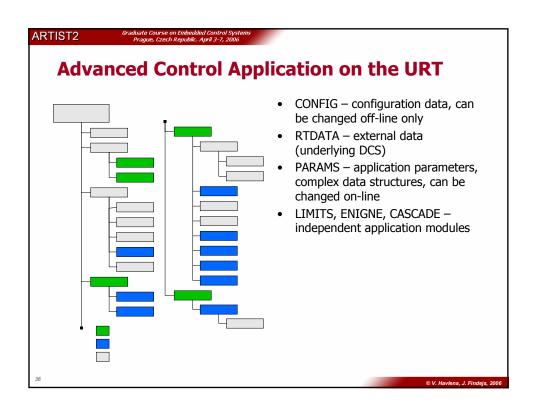

# Th2 Platform for Advanced Process Control and Real Time Optimization, Vladimir Havlena, 2 hours (Honeywell Prague)

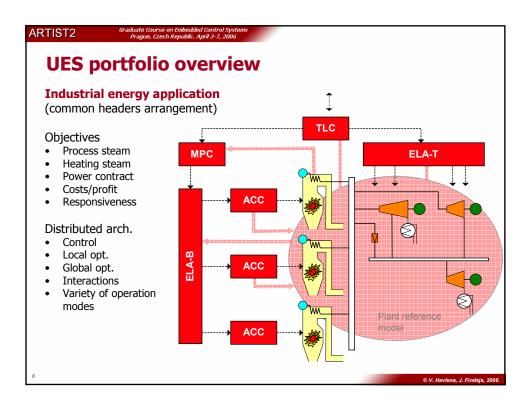

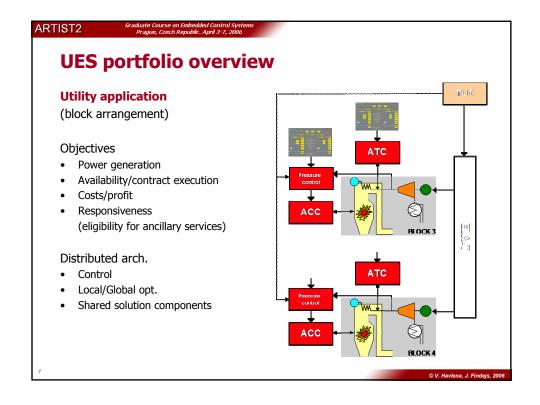

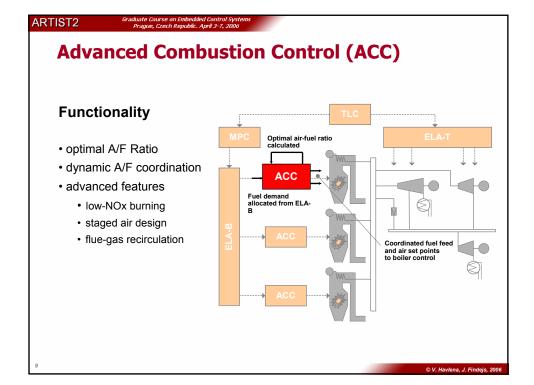

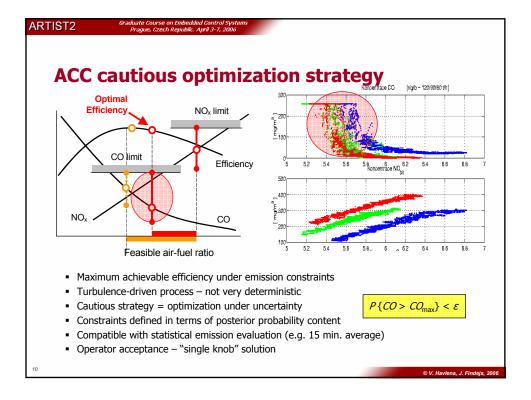

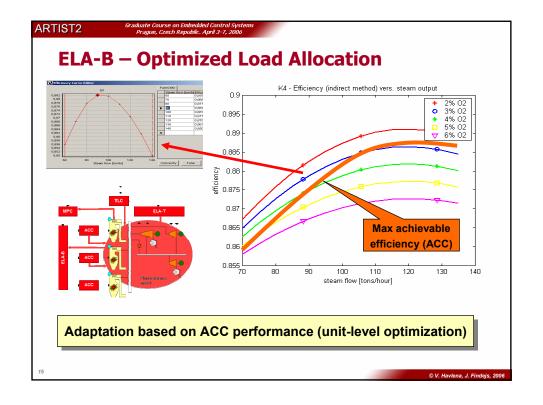

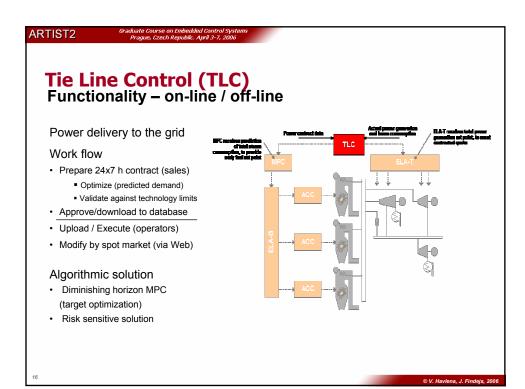

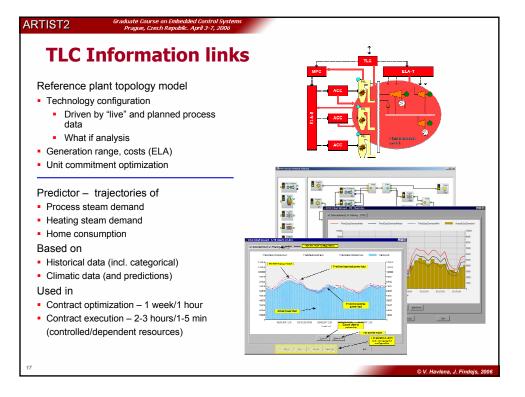

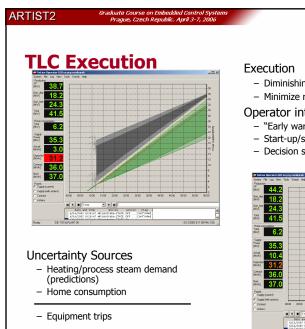

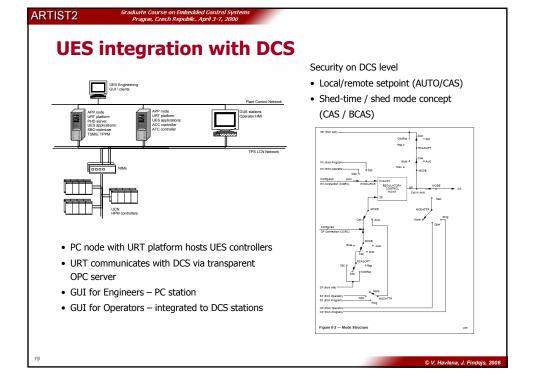

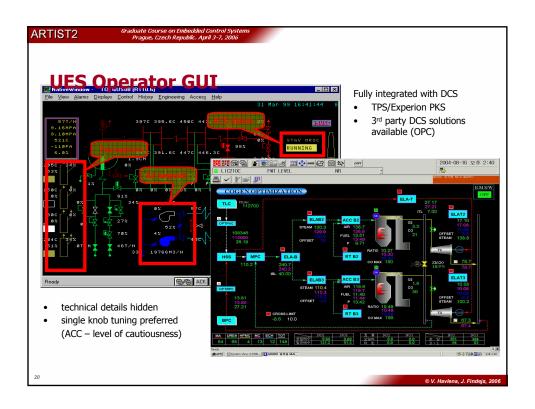

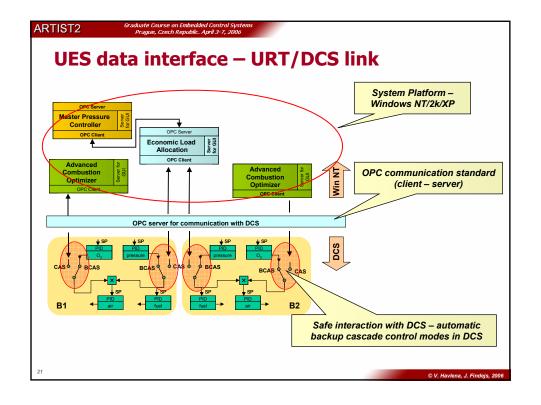

The talk will demonstrate componentised architecture for Advanced Process Control and Real Time Optimization. The concept will be illustrated by the Unified Energy Solutions (UES) package developed by the Honeywell Laboratory in Prague, a portfolio of advanced control and optimization components for utilities and industrial energy, with the objective to operate the plant with maximum achievable profit (maximum efficiency) under the constraints imposed by technology and environmental impacts.

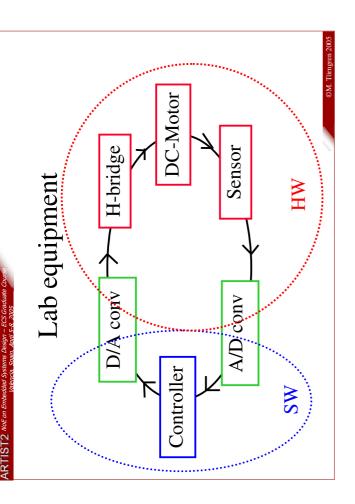

# Th3, RT practical issues, Michal Sojka and Ondrej Spinka, 2 hours (laboratory K09 - CTU)

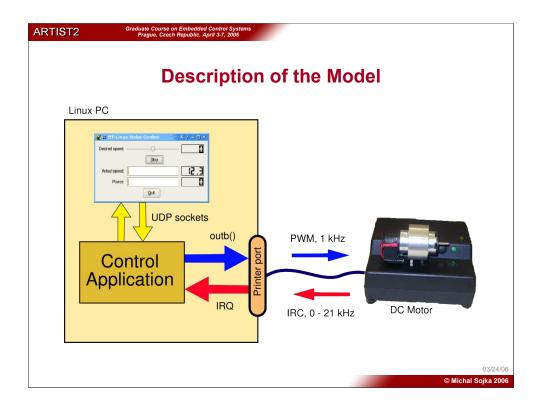

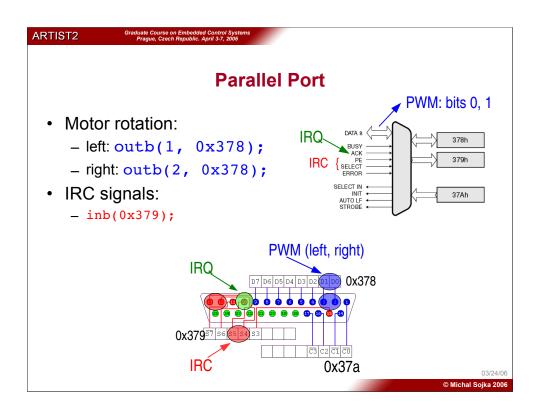

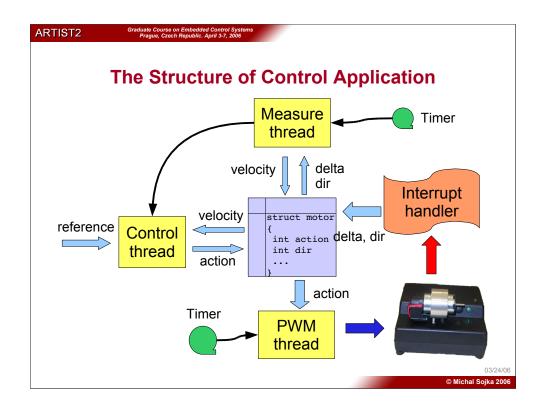

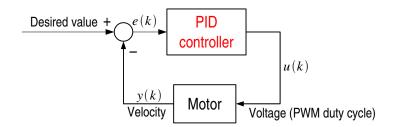

In this laboratory exercise the students will learn, how to use the Linux for low level control of a laboratory model. The main goal of this session will be to control the velocity of a DC motor. The motor is actuated by a PWM signal realized via two bit outputs as one periodic thread. The measured velocity is derived from two phase-shifted signals while implementing IRC (Incremental Radial Counter) sensor as an aperiodic thread. The motor is connected to a PC using printer port through a simple electronics consisting of a motor driver and basic logic circuits. The organization of the session will be as follows (it is assumed the students know to write a simple RT Linux program, Session T3): First, the students will be provided with information on how to control parallel port circuits through the configuration registers. Second, the students will try to generate the PWM signal for motor control. Third, they will write the code to measure the rotation velocity and they will program a simple PID controller for velocity control. Finally the use of RT Linux will be discussed.

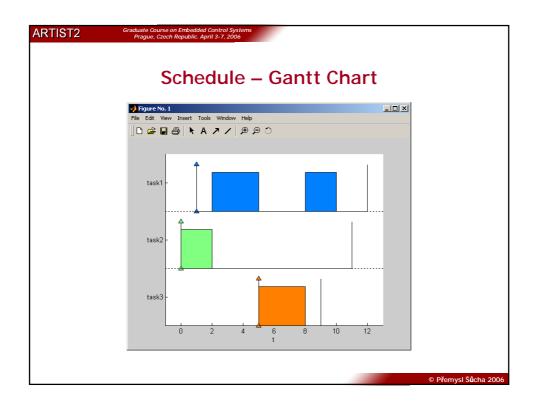

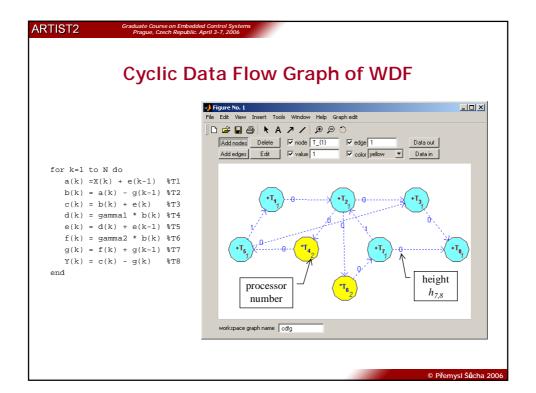

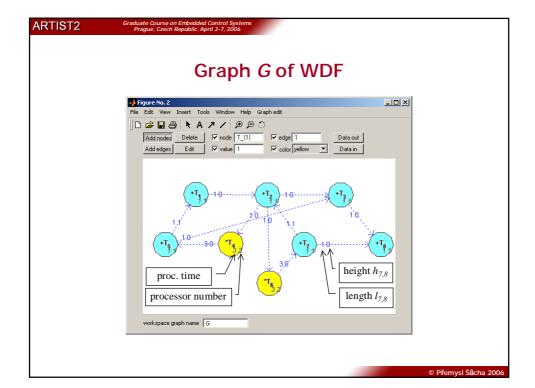

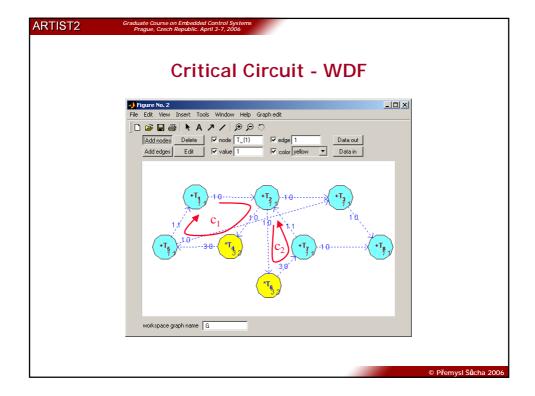

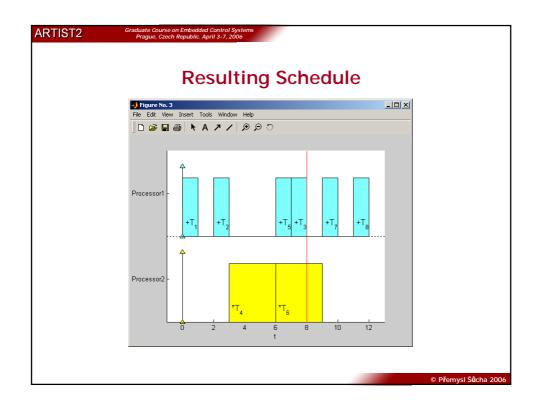

# F1, Torsche – Matlab scheduling toolbox, Premysl Sucha and Michal Kutil, 2 hours (laboratory K2 - CTU)

The aim of the seminar is to present a Matlab based Scheduling toolbox TORSCHE (Time Optimization of Resources, SCHEduling). The toolbox is intended mainly as a research tool to handle control and scheduling co-design problems. It offers a collection of data structures that allow the user to formalize various off-line and on-line scheduling problems. Potential of the toolbox will be shown on a high level synthesis of parallel algorithms.

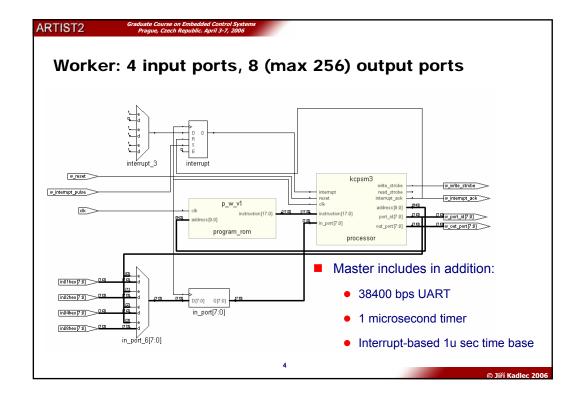

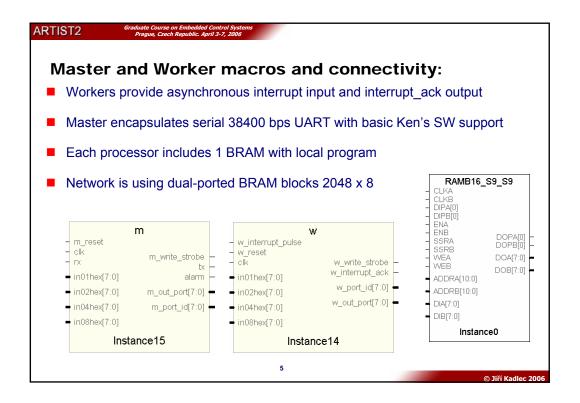

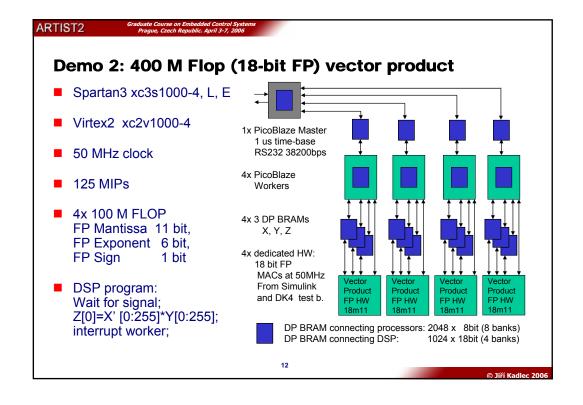

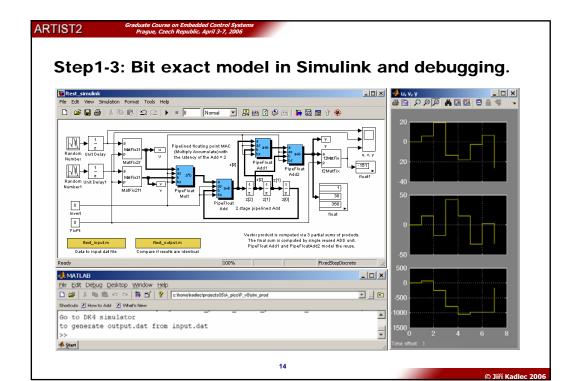

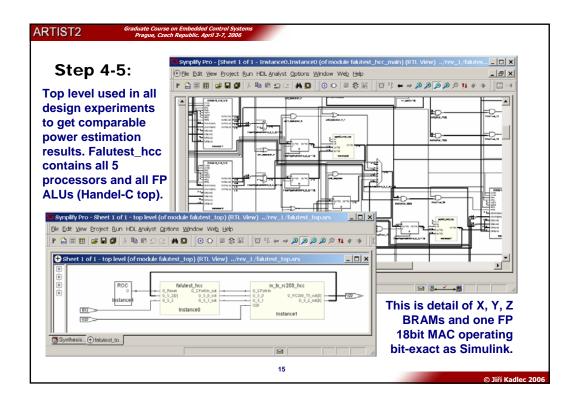

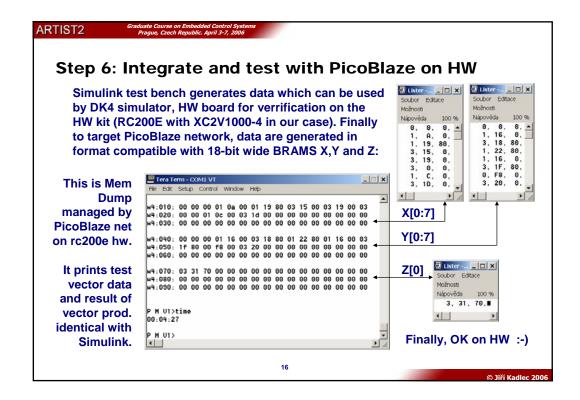

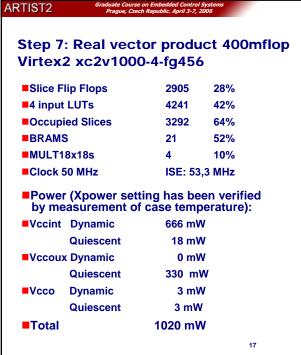

# F2, Implementing Floating-Point DSP and Control with PicoBlaze Processors, Jiri Kadlec, 2 hours (CTU)

For developers using reconfigurable HW for the implementation of floating-point DSP and Control algorithms, one key challenge is how to decompose the computation algorithm into sequences of parallel hardware processes while efficiently managing data flow through the parallel pipelines of these processes. Lecture, will summarize our current experiences with architecture based on network of Xilinx PicoBlaze controllers on a single chip. Complete design path from model-based (Simulink) and C-based designs (Handel-C) to the concrete reconfigurable HW will be demonstrated.

# ARTIST2

# Embedded Control Systems: Motivation and Examples

### M. Törngren and B. Eriksson

Division of Mechatronics, Dept. of Machine Design KTH - Royal Institute of Technology, Stockholm www.md.kth.se e-mail: martin@md.kth.se

3/21/200

©M Törngren 2006

ARTIST2 Graduate Course on Embedded Control System.

### **Outline**

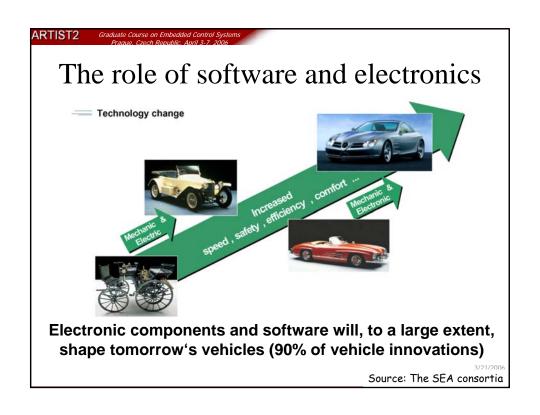

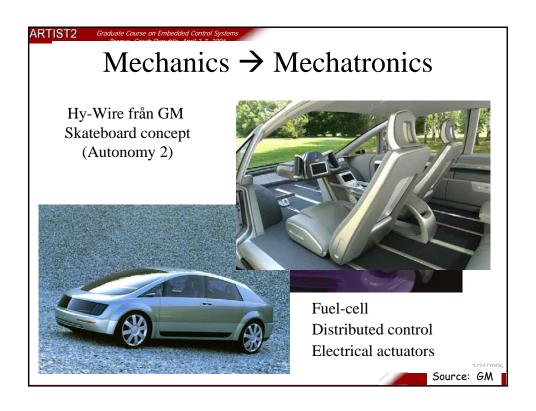

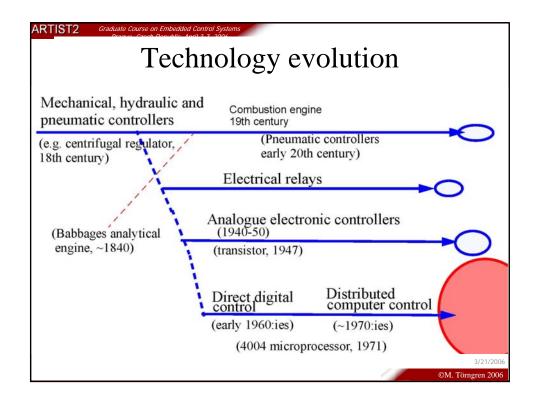

- Background: evolution of electronics and software

- Basic concepts and characteristics

- Embedded vs. general purpose computing systems

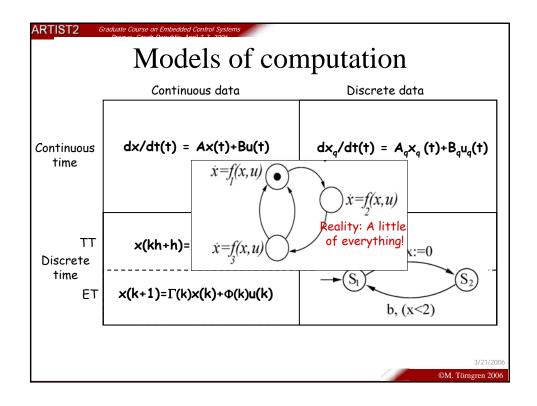

- Concepts in real-time control

- Characteristics

- Technical issues in ECS design

- Application examples

- Concluding Remarks

3/21/2006

# Historical perspectives

- "I think there is a world market for about five computers", Tomas J Watson Sr, IBM 1943

- "There are no reasons for any individuals to have a computer in their home", Ken Olson, Digital Equipment 1977

- "The current rate of progress cannot continue much longer", various computer technologists, 1950

- 'Moore's law' (Intel, 1965): Microelectronics performance is ~doubled every 18 months and chip size is reduced by 50%

- Compare: Intel 4004/1971 vs. Intel Pentium/1996

→ from 2300 to 5.5 million transistors

3/21/20

### **Outline**

- Background: evolution of electronics and software

- Basic concepts and characteristics

- Embedded vs. general purpose computing systems

- Concepts in real-time control

- Characteristics

- Technical issues in ECS design

- Application examples

- Concluding Remarks

2/21/20/

©M Törngren 2006

ARTIST2 Graduate Course on Embedded Control Systems

# Definition of embedded computer system

### **Embedded computer system (IEEE)**

A computer system that is part of a larger system and performs some of the requirements of that system; for example, a computer system used in an aircraft or rapid transit system.

3/21/2006

# Computer Architecture Trends

### Present proposals for future billion-transistor computers:

- Desktop uniprocessors for technical applications

- Multiprocessor servers for transaction processing

- Large continuous data-processing capability

### Future embedded system computers:

- Harsh environment tolerance; temperature, vibration, radiation

- Low power dissipation, power down modes

- On-chip input-output units, communication and memory

- Predictable behavior, support for concurrency

/21/2006

# Definition of real-time

A system, where correct timing behavior is strongly related to functionality, performance and reliability

### Common definitions:

- A computer system is a real-time one if it explicitly manages resources in order to meet timing constraints (Douglas Jensen, 1992)

- A real-time system is a system where the correctness depends not only on the logical result of computation but also on the time at which the results are produced". (Jack Stankovic, 1988).

3/21/2006

## Characteristics of ECS

- Rich functionality

- Resource constraints

- Increasing connectivity

- Tight process relation

- RT constraints

- ET and TT, parallelism

- Roughness

- Dependability: safety, reliability/availability, security

- Multidisciplinarity

3/21/2000

ARTIST2 Graduate Course on Embedded Control Systems

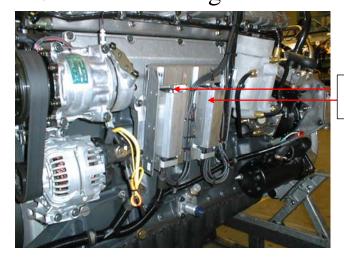

Scania diesel engine and controller

ECU connectors on top of the ECU

Engine ECU tasks: control of engine, fan, alternator, engine brake, turbo, and the EGR valve + CAN communication, + diagnostics, ...

R/21/200/

Courtesy of Scania

# Conflicts? Cost vs. Quality (in general) vs. Time Testability vs. performance Performance vs. flexibility Reliability vs. cost Safety vs. availability Control robustness vs. performance ....

### ARTIST2 Graduate Course on Embedded Control System Prague, Czech Republic, April 3-7, 2006

### **Outline**

- Background: evolution of electronics and software

- Basic concepts and characteristics

- Embedded vs. general purpose computing systems

- Concepts in real-time control

- Characteristics

- Technical issues in ECS design

- Application examples

- Concluding Remarks

3/21/200

©M Törngren 2006

#### ARTIST2 Graduate Course on Embedded Control Systems

# A sample of technical issues in ECS design and implementation

- Discretization

- Quantization

- Delays

- Jitter in delays and periods

- Aliasing

- Triggering and tasking partitioning, scheduling

- Code implementation

- Sensor and actuator limitations

- Calibration/diagnostics

- Error detection and error handling

3/21/2006

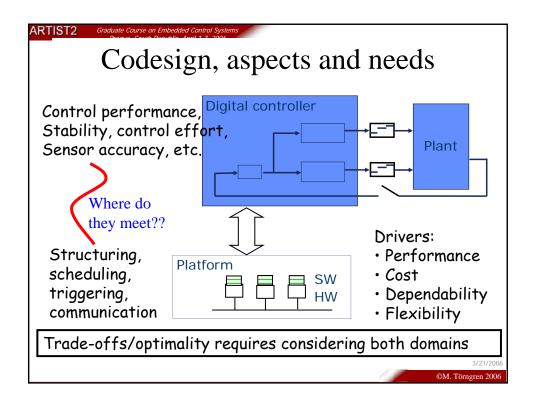

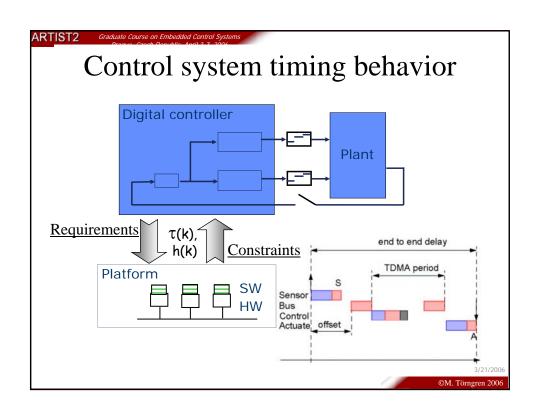

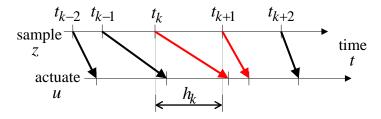

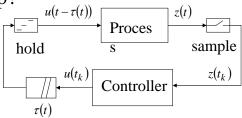

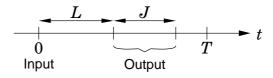

# Examples of timing properties caused by a particular implementation

Period:  $h(k) = t_k - t_{k-1}$  and jitter

E2e delay,  $\tau(k)$ , and jitter, e.g.  $\tau_{min}(k) <= \tau(k) <= \tau_{max}(k)$

How does the given timing scenario affect control performance? How does choices in computer system design parameters affect the timing behavior and thereby the control performance?

3/21/200

©M Törngren 2006

#### ARTIST2 Graduate Course on Embedded Control System

## Control analysis/compensation

• How do the timing properties affect the closed loop?

- Analysis of steady state and transient behavior  $x(t_{k+1}) = \Phi(h_k)x(t_k) + \sum \Gamma(h_k)u(t_{k-(nd-\alpha)})$

- Potential compensation for jitter

- Run-time information example: Actual data delay

3/21/2006

# Co-design with respect to timing

Has to be defined to ensure proper operation Typical solutions:

- $\tau \ll T$  enforced (costly)

- $\tau$  < T assumed (jitter neglected)

- $\tau$  =T, with deterministic solution, however causing some performance degradation and reduced flexibility (trade-offs!)

Computer system options: Design for predictability if possible Control system options: Analyse, and compensate if possible Co-design options:

- May leave some unpredictability in computer system design

- May be able to handle non-perfect existing computer system

3/21/200

ARTIST2 Graduate Course on Embedded Control System

Prague, Czech Republic, April 3-7, 2006

## **Outline**

- Background: evolution of electronics and software

- Basic concepts and characteristics

- Embedded vs. general purpose computing systems

- Concepts in real-time control

- Characteristics

- Technical issues in ECS design

- Application examples

- Concluding Remarks

3/21/20

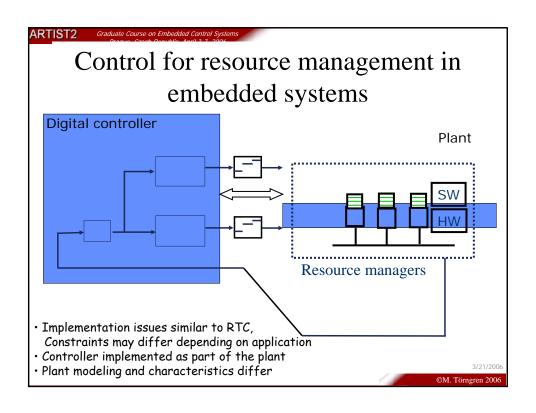

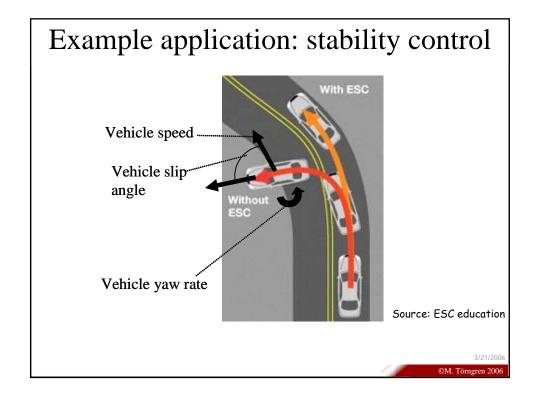

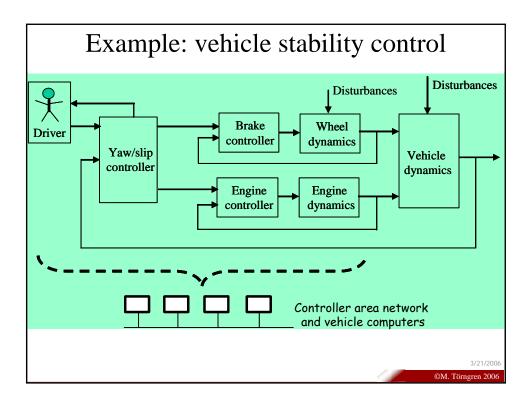

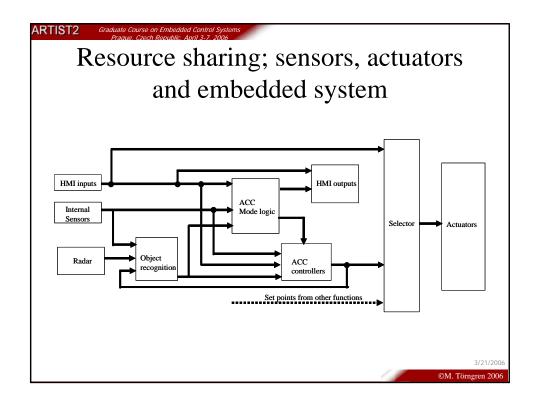

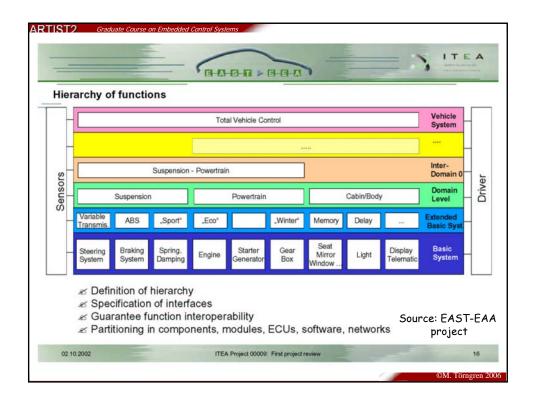

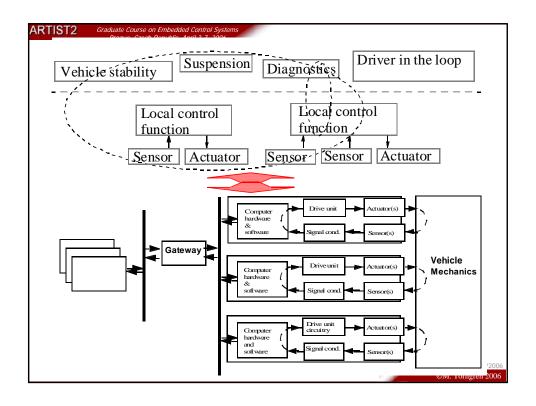

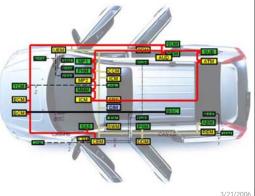

### Vehicle stability control - characteristics

- Several modes of operation

- · Hierarchical and cascaded control

- Multiple input, multiple output

- Control loop closed over in-vehicle network(s)

- Availability critical (graceful degradation)

- Safety critical, real-time operation

- Redundancy in hardware (sensors, actuators, processors), information and algorithms

### Some challenges:

- Software upgrades (and security)?

- Who is in charge (driver vs. computer control)?

- How to define a suitable scaleable architecture?

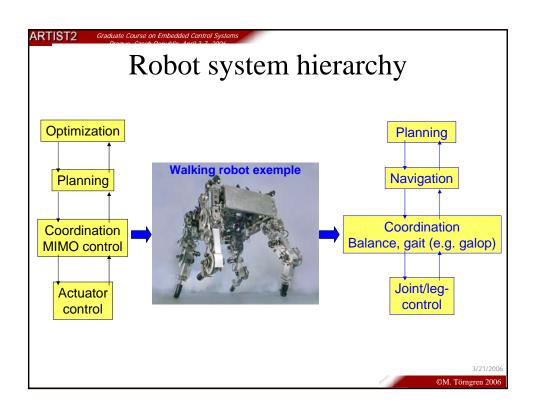

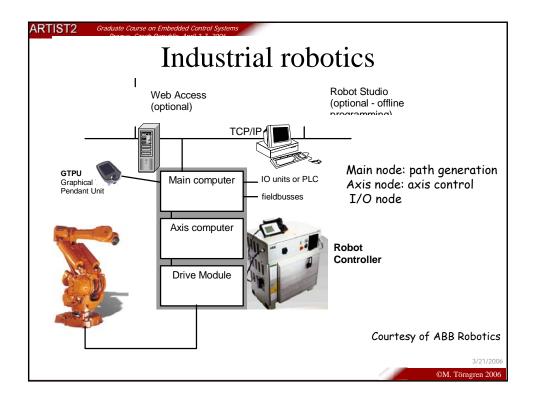

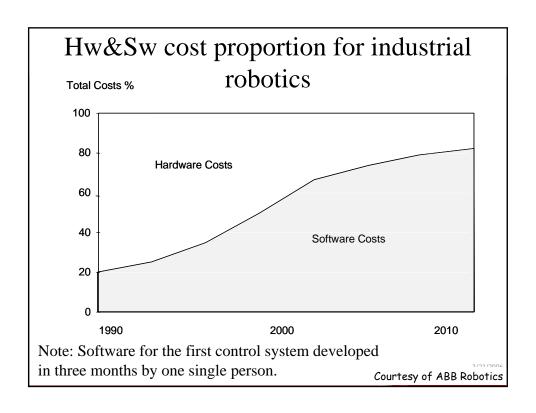

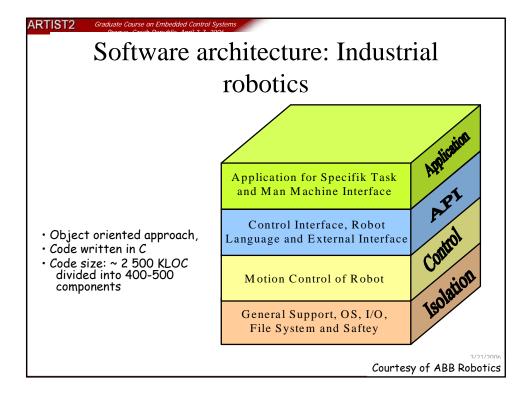

### Industrial robots: characteristics

- The same controller type is often used for different kinds of robots for cost efficiency

- Core part: motion control, the application packages (welding, assembling, etc) and robot programming

- Most other parts provided by suppliers, e.g. I/O and HW

- Systems integration into e.g. an assembly line for cars

- PLC systems

- Production systems from other vendors

- Central requirement: Availability

- Volume: ~ 10 thousands per year (for leading company)

- including different kinds of robots

Courtesy of ABB Robotics

# Industrial robotics; architecture requirements

- Openness, to facilitate integration

- Integration with different communication protocols (Profibus, Interbus, Foundation fieldbus, FIP, ...)

- The control system to be configurable to facilitate reuse

- SW has to be easy to port, 'lives' longer than HW

- Typical reliability requirement: MTBF > 60000 h

→ ~ production line with 800 robots with one robot

failing per week in average

3/21/2006

# Outline Background: evolution of electronics and software Basic concepts and characteristics Embedded vs. general purpose computing systems Concepts in real-time control Characteristics Technical issues in ECS design Application examples Concluding Remarks

# Concluding remarks

- A very broad spectra of ECS applications!

- Multidisciplinary development a key challenge

- Needs for co-design relates to conflicting requirements

- Closed-loop control of increasing importance

- Many other issues such as reliability/safety, diagnostics, reuse, upgrades, ...

3/21/2006

Törngren 2006

# ARTIST2

# Embedded Control Systems: Control Issues

### P. Albertos

Universidad Politécnica de Valencia Dept. of Systems Engineering and Control POB. 22012 E-46071 Valencia, Spain.

Fax: +34 96 3879579 e-mail: pedro@aii.upv.es

### ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cours

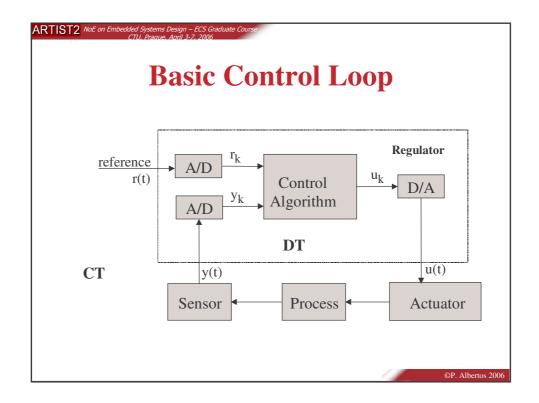

### **Outline**

- Embedded Systems

- RT constraints

- Embedded Control Systems

- Control issues

- Non-uniform sampling

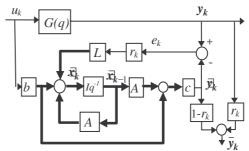

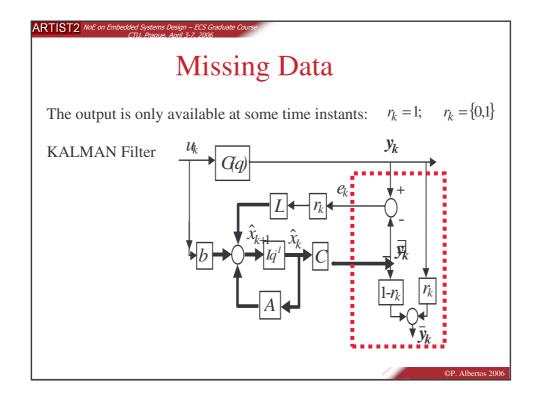

- Missing data

- Changes in sampling period

- Performance degrading

- Concluding Remarks

©P. Albertos 2006

# Embedded systems: RT Issues

- Resource constraints

- Power aware

- Task Management: Critical and soft real-time activities

- Task definition

- Priority assignment

- Time units (periods)

- Full range of communication devices

- Changeable operating conditions

- CPU utilization control

- Adaptable to the changing conditions

- Self-organizing

- On-line scheduling

©P. Albertos 2006

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cours

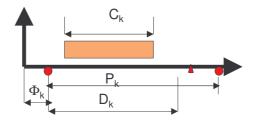

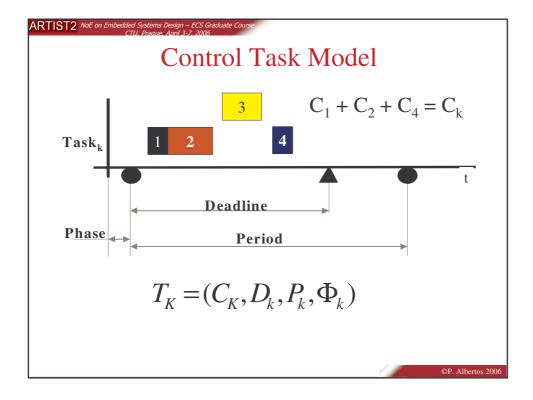

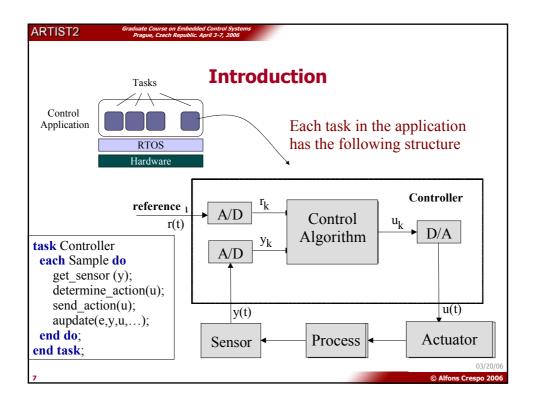

### **Real-Time Task Model**

- A task (T<sub>k</sub>) is defined by four parameters:

- C<sub>k</sub>: Worst Case Execution Time (WCET)

- D<sub>k</sub>: Deadline

- P<sub>k</sub>: Period

- $-\Phi_{\kappa}$ : Phase

```

Control task

...

loop

convert _sensor _analog_ digital (y);

compute _control _action (u);

compute _error (e)

compute _control _action (u)

send _ converted _ control_ action (u);

update_internal_variables(y,u, ...);

Next _Iteration:= Next _Iteration + Period;

delay until Next _Iteration;

end loop;

...

```

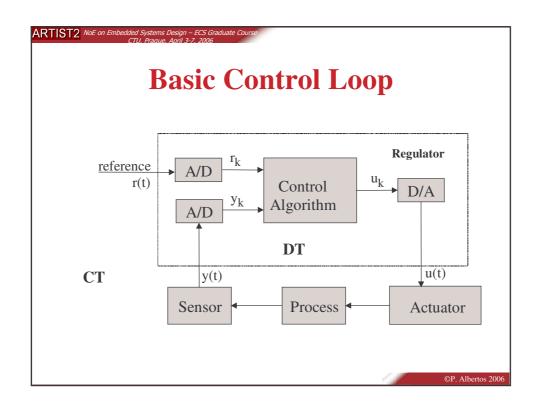

### Basic assumptions in Computer control

- The Data Acq. system provides the required data

- The actuators' drivers deliver the control actions

- The CPU computes on-time the control action

- The required data are stored in the memory

- The sampling pattern is regular (constant, synchronous and uniform for any control task)

- The control algorithm is well defined

- Alternative controllers are independent

- Power supply is guaranteed

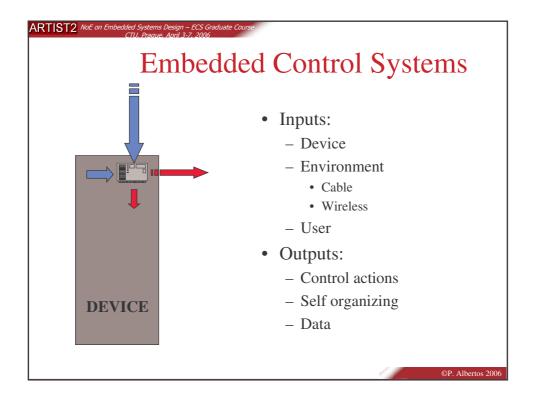

# **Embedded Control Systems**

- Embedded systems with:

- hard RT constraints

- guarantee of safe operation

- best possible performances

- Additional issues from viewpoint of:

- implementation

- computation

- algorithmic

### **RT Control Issues**

- RT Constraints:

- Maximize the time determinism

- For many controllers a worst-case approach works well e.g., PI, PID, State Feedback, ...

#### however, many exceptions:

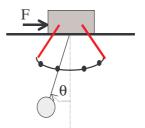

- hybrid controllers that switch between different modes with different characteristics

- model-predictive controllers (MPC)

- convex optimization problem solved every sample execution time can vary an order of magnitude

- Compensate the variations:

- · Measure and react

- Feedback robustness

©P Albertos 2006

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cours

### **Control Performances**

• Relevance of the control actions

### The Control Effort concept

- Sensitive to time delays

- Changes in the sampling period:

- Controller parameters

- Past data

- Commutation bumping

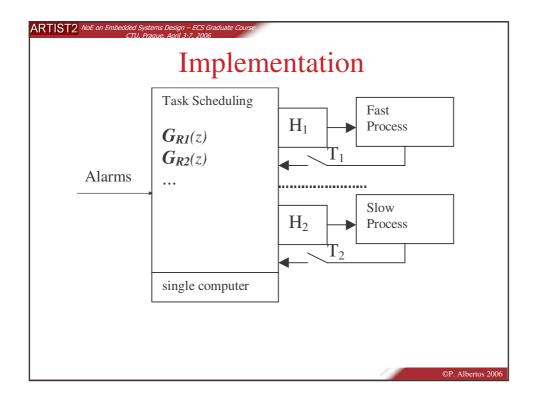

# **ECS:** Implementation

- The same resources must be **shared** between different tasks

- Alternative control algorithms should be ready to get the control of the process

- Working conditions, such as priority, allocated time and memory or signals availability may change

- Variable delays should be considered

- Validation and certification

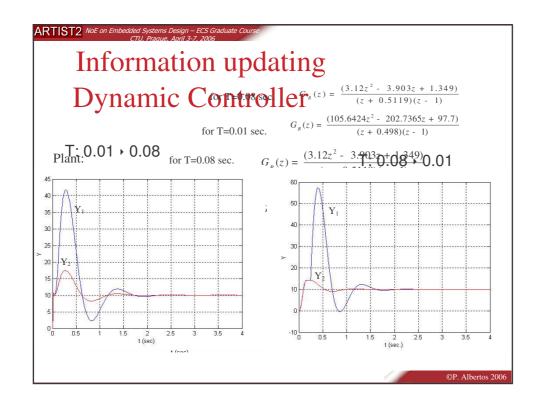

# ECS: Computational viewpoint

- Economic algorithms

- Information updating

- Optional tasks

- Hybrid systems

- CPU use measurement and optimisation

- On-line scheduling

- Memory saving

- Economic hardware redundancy

- Fault detection and isolation

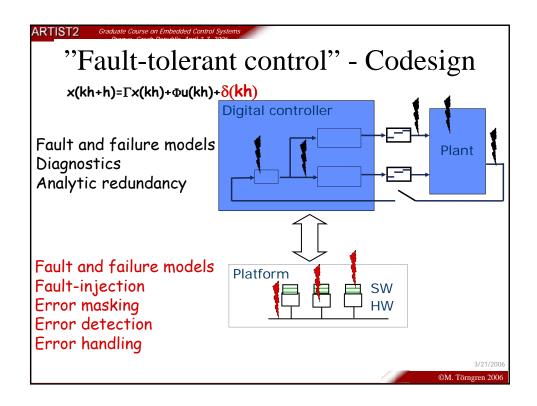

### ECS: Control algorithm viewpoint

- Reduced order models

- Non-conventional sampling and updating patterns

- Missing data control

- Event-triggered control

- Hybrid control systems

- Decision and supervisory control

- Multimode control

- Sampling rate changes

- Fault-tolerant control

- Degraded and back-up (safe) control strategies

- Battery monitoring and control

©P Albertos 2006

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cours

# ECS: Control algorithm viewpoint

- Reduced order models

- Non-conventional sampling and updating patterns

- Missing data control

- Event-triggered control

- Hybrid control systems

- Decision and supervisory control

- Multimode control

- Sampling rate changes

- Fault-tolerant control

- Degraded and back-up (safe) control strategies

- Battery monitoring and control

# ECS: Control algorithm viewpoint

- Reduced order models

- Non-conventional sampling and updating patterns

- Missing data control

- Event-triggered control

- Hybrid control systems

- Decision and supervisory control

- Multimode control

- Sampling rate changes

- Fault-tolerant control

- Degraded and back-up (safe) control strategies

- Battery monitoring and control

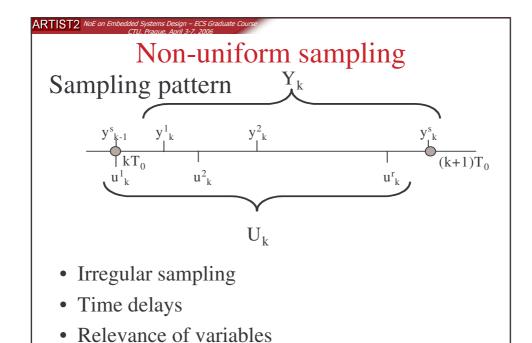

# Variable Sampling Time

#### **PID Controller:**

$$u(t) = K_p e(t) + K_d \frac{d}{dt} e(t) + K_i \int_{0}^{t} e(\tau) d\tau;$$

$$u_k - u_{k-1} = q_0 e_k + q_1 e_{k-1} + q_2 e_{k-2}$$

$$\begin{split} q_o &= K_p + \frac{K_d}{t_k - t_{k-1}} = K_p + \frac{K_d}{T_1} & T_1 = t_k - t_{k-1} \\ q_2 &= \frac{K_d}{t_{k-1} - t_{k-2}} = \frac{K_d}{T_2} & T_2 = t_{k-1} - t_{k-2} \\ q_1 &= -K_p - K_d \, \frac{t_k - t_{k-2}}{(t_k - t_{k-1})(t_{k-1} - t_{k-2})} + K_i(t_k - t_{k-1}) = -K_p - K_d \, \frac{T_1 + T_2}{T_1 T_2} + K_i T_1 \end{split}$$

©P. Albertos 2006

#### ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cours

### Control task

```

loop

convert _sensor _analog_ digital (y), get t_k;

compute _control _action (u);

compute T_1,T_2

compute coefficients q_i

compute _error (e)

compute _control _action (u) \leftarrow \Delta

send _ converted _ control_ action (u);

update_internal_variables(y,u, ...);

Next _Iteration:= Next _Iteration + Period;

delay until Next _Iteration;

end loop;

```

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cour CTU Prague April 3-7 2006

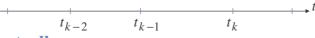

# PID: Time delay effect

- Open loop control

- Discretized controller, independently of the plant

- Degrading as the time delay increases

- EXAMPLE: Plant:  $G(s) = \frac{1.5}{(s+0.5)(s+1.5)}$

Parameters:  $K_P = 8$   $T_D = 0.2$   $T_I = 3.2$

Sampling period: T=0.1 sec

$$q_0 = K_p + \frac{K_d}{T};$$

$q_1 = -K_p - \frac{2K_d}{T} + K_i T;$   $q_2 = \frac{K_d}{T}$

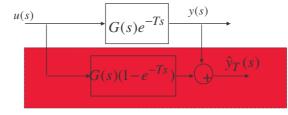

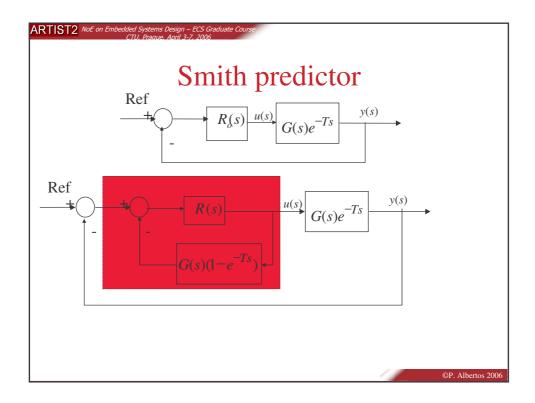

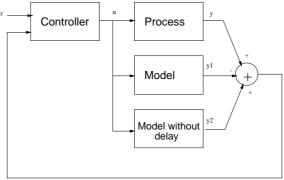

# **Delay Counteraction**

• Input/output delay

$$\mathcal{X}(t) = Ax(t) + Bu(t-\tau); y(t) = Cx(t)$$

$$\mathcal{X}(t) = Ax(t) + Bu(t); y(t) = Cx(t-\tau)$$

$$y(s) = G(s).e^{-s\tau}u(s)$$

- Smith Predictor

- Error prediction

- Output prediction

©P. Albertos 2006

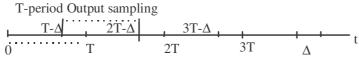

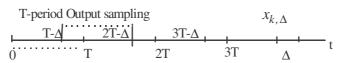

T-period Control updating

• Classical Smith Predictor Option

PID: error prediction loop convert\_sensor\_analog\_digital(y);

$$e_{k,\Delta} = e_k + \frac{\Delta}{T}(e_{k,\Delta} - e_{k-1,\Delta}) \text{ compute _control _action (u); } \\ e_{k,\Delta} = \frac{T}{T-\Delta}e_k - \frac{\Delta}{T-\Delta}e_{k-1,\Delta} \text{ compute _actual _error (eA)} \\ e_{k,\Delta} = \frac{T}{T-\Delta}e_k - \frac{\Delta}{T-\Delta}e_{k-1,\Delta} \text{ compute _control _action (u); } \\ e_{k,\Delta} = \frac{T}{T-\Delta}e_k - \frac{\Delta}{T-\Delta}e_{k-1,\Delta} \text{ compute _control _action (u); } \\ e_{k,\Delta} = \frac{T}{T-\Delta}e_k - \frac{\Delta}{T-\Delta}e_{k-1,\Delta} \text{ compute _control _action (u); } \\ e_{k,\Delta} = \frac{T}{T-\Delta}e_k - \frac{\Delta}{T-\Delta}e_{k-1,\Delta} + \frac{\Delta}{T-\Delta}e_{k-1,\Delta} \text{ compute _control _action (u); } \\ e_{k,\Delta} = \frac{T}{T-\Delta}e_k - \frac{\Delta}{T-\Delta}e_{k-1,\Delta} + \frac{\Delta}$$

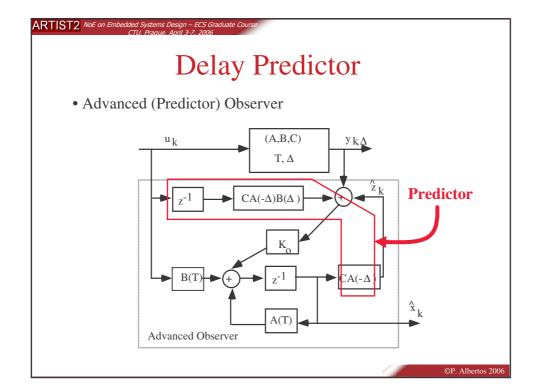

# Output/State prediction

T-period Control updating

$$\begin{split} \overline{x}_k &= A(\Delta)x_{k,\Delta} + B(\Delta)u_{k-1} & u_k = K.\left[A(\Delta)x_{k,\Delta} + B(\Delta)u_{k-1}\right] + r_k \\ y_{k,\Delta} &= C_{-}^{x_{k,\Delta}}, & x_{k,\Delta} = A(-\Delta)x_k - A(-\Delta)B(\Delta)u_{k-1} \\ z_k &= C.A(-\Delta)x_k = y_{k,\Delta} + C.A(-\Delta).B(\Delta)u_{k-1} \\ \hat{x}_{k+1} &= A(T)\hat{x}_k + B(T)u_k + K_o(z_k - \hat{z}_k) \\ \hat{z}_k &= CA(-\Delta)\hat{x}_k \end{split}$$

# ECS: Control algorithm viewpoint

- Reduced order models

- Non-conventional sampling and updating patterns

- Missing data control

- Event-triggered control

- Hybrid control systems

- Decision and supervisory control

- Multimode control

- Sampling rate changes

- Fault-tolerant control

- Degraded and back-up (safe) control strategies

- Battery monitoring and control

©P Albertos 2006

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cours

# Output prediction

Model-based open-loop prediction

$$\hat{y}_{k} = -\sum_{i=1}^{n} a_{i} \hat{y}_{k-i} + \sum_{i=1}^{n} b_{i} u_{k-i} = \hat{\psi}_{k-1}^{T} \cdot \theta$$

$$u_{k} \qquad y_{k}$$

$$G(q) \qquad y_{k}$$

$$Store \ u$$

$$y_{k} \qquad y_{k}$$

$$y_{k} \qquad y_{k}$$

$$\varphi_{b} \qquad \varphi_{b}$$

#### Drawbacks:

- Error dynamics is that of the process.

- Lack of robustness against disturbances.

# Output prediction (2)

Output estimation with mixed vector of past outputs

# Other options

Enlarged polynomials

$$\frac{d_1q^{-1} + \Lambda + d_Lq^{-L}}{1 + c_1q^{-1} + \Lambda + c_Lq^{-L}} = \frac{(b_1q^{-1} + \Lambda + b_nq^{-n}) \cdot E(q^{-1})}{(1 + a_1q^{-1} + \Lambda + a_nq^{-n}) \cdot E(q^{-1})} = \frac{D(q^{-1})}{C(q^{-1})}$$

Linear state observer:

$$\hat{x}_{k} = A^{N} \hat{x}_{k-N} + A^{N-1} b u_{k-N} + \Lambda + b u_{k-1} + L \left( y_{k} - c (A^{N} \hat{x}_{k-N} + A^{N-1} b u_{k-N} + \Lambda + b u_{k-1}) \right)$$

$$\hat{y}_{k+j} = c(A^{j}\hat{x}_{k} + A^{j-1}bu_{k} + \Lambda + bu_{k+j-1}), j = 1, K, N-1$$

### Parameter estimation

Regular pattern: dual rate model

$$G(z) = \frac{B_N(z^{-1})}{A_N(z^{-1})} = \frac{c_{N \cdot n-1}z^{-1} + c_{N \cdot n-2}z^{-2} + \Lambda + c_1z^{-(N \cdot n-1)} + c_0z^{-N \cdot n}}{1 + d_{n-1}z^{-N} + \Lambda + d_1z^{-N(n-1)} + d_0z^{-N \cdot n}}$$

Regression vector and parameters:

$$\psi_{k} = \left[ -y_{k-N} - y_{k-2N} \Lambda - y_{k-n-N} u_{k-1} u_{k-2} \Lambda u_{k-n-N} \right]^{T}$$

$$\theta_{N} = \left[ d_{n-1} d_{n-2} \Lambda d_{0} c_{n-N-1} c_{n-N-2} \Lambda c_{0} \right]^{T}$$

Irregular pattern or fast model

$$\hat{\psi}_{k} = [-\hat{y}_{k-1} - \hat{y}_{k-2}\Lambda - \hat{y}_{k-n}u_{k-1}\Lambda u_{k-n}]^{T}$$

Output predictor:

edictor:

$$\hat{y}_k = f(\hat{\theta}_k, y_j r_j, u_j, \hat{y}_j)$$

$$\hat{y}_k = (1 - r_k) \left( \hat{\psi}_y (k - 1)^T \cdot \theta_a + \psi_u (k - 1)^T \cdot \theta_b \right) + r_k y_k$$

©P. Albertos 2006

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Course

# Fast parameter estimation $\gamma_k = \frac{P_k}{\lambda + \vec{\psi}_k^T P_k \vec{\psi}_k}$

$$\gamma_{k} = \frac{P_{k}}{\lambda + \overrightarrow{\psi}_{k}^{T} P_{k} \overrightarrow{\psi}_{k}}$$

$$\overrightarrow{\theta}_{k} = \overrightarrow{\theta}_{k-1} + \gamma_{k} \cdot \overrightarrow{\psi}_{k} (y_{k} - \overrightarrow{\psi}_{k}^{T} \cdot \overrightarrow{\theta}_{k-1}) \cdot r_{k}$$

$$P_{k+1} = \frac{1}{\lambda} (I - \gamma_{k} \overrightarrow{\psi}_{k} \overrightarrow{\psi}_{k}^{T}) P_{k} \cdot r_{k} + P_{k} (1 - r_{k})$$

$$\overrightarrow{y}_{k} = f(\overrightarrow{\theta}_{k}, y_{j} r_{j}, u_{j}, \overrightarrow{y}_{j})$$

$(r_k=1 \text{ if measurement and } 0 \text{ if not}).$

- Convergence depend on sampling period and data availability ra

- The stability of the output predictor is a necessary but not sufficient condition for convergence.

- For small T wrong attractors appear close to the dual-rate poles.

(Poles in those positions have an oscillating impulse response with the periodicity of the lower-rate sampling).

# Convergence

**Example:**

$$G(s) = \frac{2}{s^2 + 3s + 1}$$

, with N=3.

If T = 0.02, the estimates are

$$G^*(z) = 10^{-4} \frac{0.224z + 5}{z^2 + 0.986z + 0.984}$$

instead of the correct one  $10^{-3} \frac{0.392z - 0.384}{z^2 - 1.941z + 0.942}$ .

If T = 0.7, the estimates are the correct parameters.

ARTIST2 NoE on Embedded Syste

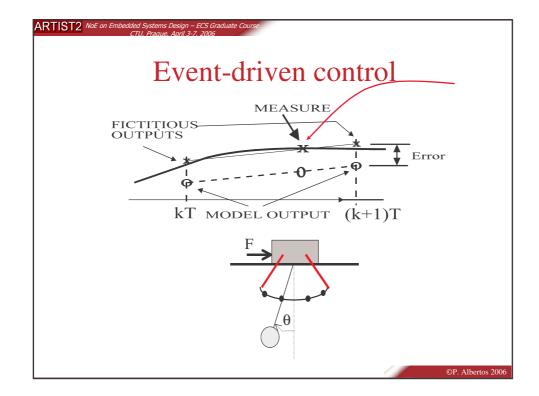

### Event-driven sensor

$$M_m = F + T \sin\theta - k_m^{\text{A}}$$

$$m_m = -T \sin\theta m_m^{\text{A}} = T \cos\theta - mg$$

$$x_m = x_l + L \sin\theta y_m = -l \cos\theta$$

$$\theta = \frac{-(F - k \Re)\cos\theta - mlsin\theta\cos\theta \Re - g\overline{M}sin\theta}{\overline{M}L - mL\cos^2\theta}$$

$\overline{M} = F - k - ml \cos \theta + ml \sin \theta$

$$\overline{M} = M + m$$

$$M=15$$

:

$$G(z) = \frac{-7.39 \cdot 10^{-4} (z - 1)(z - 0.9952)}{(z - 0.9945)((z - 0.5242)^2 + 0.8464^2)}$$

$$G(z) = \frac{-7.39 \cdot 10^{-4} (z - 1)(z - 0.9952)}{(z - 0.9945)((z - 0.5242)^2 + 0.8464^2)} \qquad G(z) = \frac{-7.541 \cdot 10^{-4} (z - 1)(z - .9953)}{(z - 0.9928)((z - 0.6261)^2 + 0.7751^2)}$$

ARTIST2 NoE on Embedded Systems Design – ECS Graduate C

# Partial parameter set

$$\theta \approx \begin{pmatrix} -2.043 \\ 2.038 \\ -0.986 \\ -7.39 \cdot 10^{-4} \\ 3.5 \cdot 10^{-6} \\ 7.36 \cdot 10^{-4} \end{pmatrix} + \begin{pmatrix} -0.0135 \\ 0.0135 \\ 0 \\ -10^{-6} \\ 2.8 \cdot 10^{-9} \\ 10^{-6} \end{pmatrix} \Delta m$$

# ECS: Control algorithm viewpoint

- Reduced order models

- Non-conventional sampling and updating patterns

- Missing data control

- Event-triggered control

- Hybrid control systems

- Decision and supervisory control

- Multimode control

- Sampling rate changes

- Fault-tolerant control

- Degraded and back-up (safe) control strategies

- Battery monitoring and control

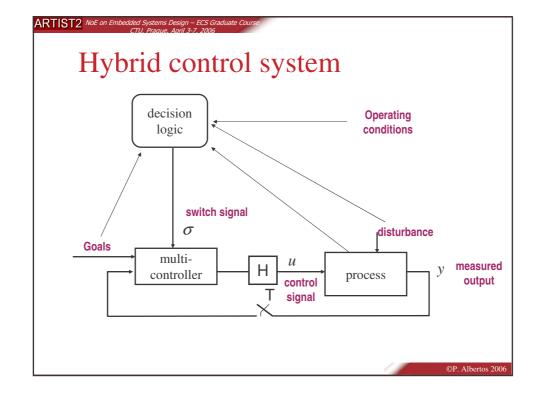

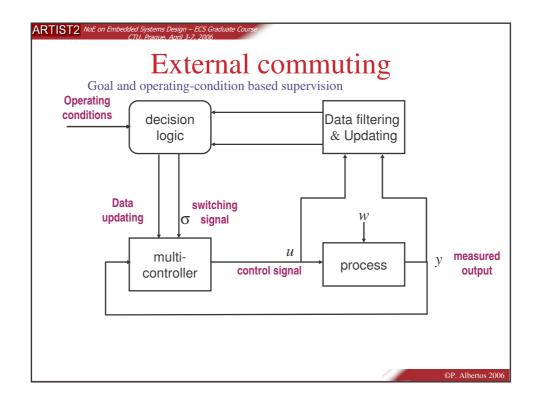

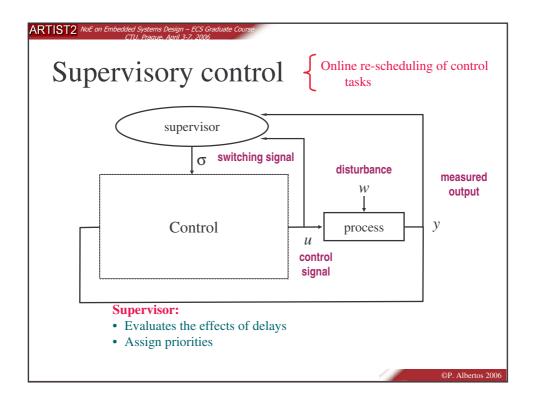

# Types of supervision

- try one controller after another in a pre-defined sequence

- Pre-routed supervision

- · Estimator-based supervision

- Performance-based supervision stop when the performance seems acceptable

- Goal and Operating-conditions based supervision

keep controller while observed performance is acceptable

- · when performance of current controller becomes unacceptable, switch to controller that leads to best expected performance based on available data

- · estimate process model from observed data

- select controller based on current estimate Certainty Equivalence

- On-line re-scheduling of the control tasks

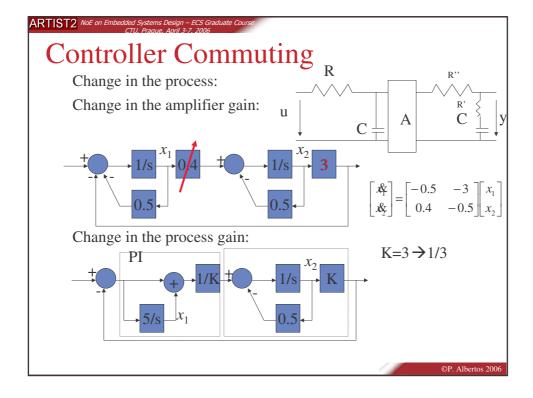

# Controller commuting

- · Given a change on:

- Goal

- Working point

- Operating conditions

# Change in controller

$$q_0 = K_p + \frac{K_d}{T}; \ q_1 = -K_p - \frac{2K_d}{T} + K_i T; \ q_2 = \frac{K_d}{T}$$

**♯** Controller selection (or computation)

$$u_k = (K + K * T)x_k$$

- **■** Transfer:

- Parameter updating

- Controller initialization

- Stability

- Performances

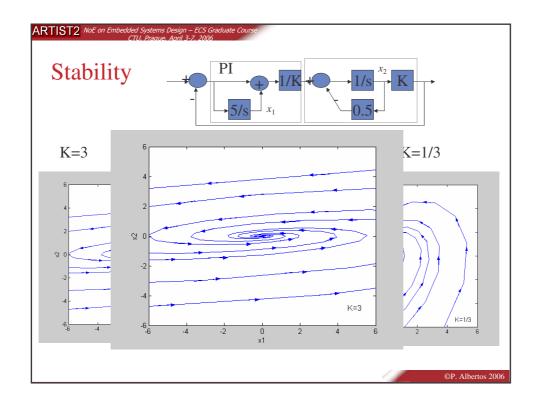

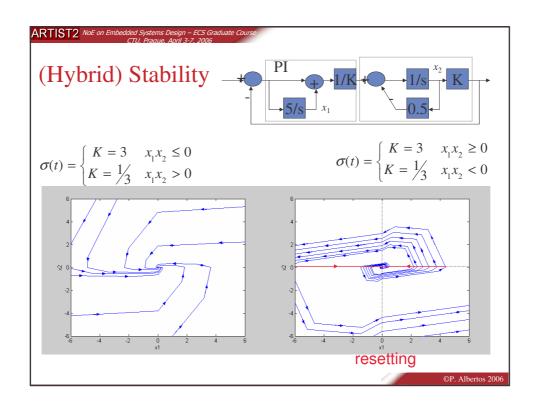

# Controller commuting: Stability issues

Each controller stabilizes the plant under control, But ... what under commuting?

- Common Lyapunov function

- Controller initialization

- Controller resetting

#### ARTIST2 NoE on Embed

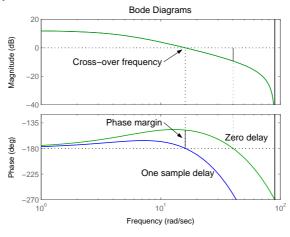

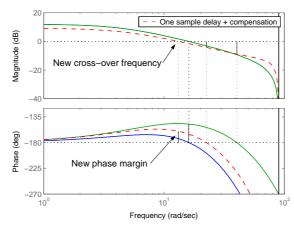

### **Control Effort**

The maximum allowable time delay is given by the phase margin, derived from the frequency analysis of the open loop output feedback

$$\Delta \leq \frac{\psi_m}{\omega_c}$$

$$|G(j\omega_c)| = 1$$

$$|G(j\omega_c)| = 1$$

$\psi_m = \pi + \angle G(j\omega_c)$

State feedback:

• Given  $\mathcal{X}(t) = Ax(t) + bu(t)$

being

$$a(s) = |sI - A| = \prod_{i=1}^{n} (s - a_i)$$

$$u(t) = -kx(t) + r(t)$$

$$A_n = -\sum_{i=1}^n a_i$$

The state feedback control *k* places the closed loop poles: p(s)

$$A_n = -\sum_{i=1}^n a_i$$

$$p(s) = |sI - A + bk| = \prod_{i=1}^n (s - p_i)$$

$$P_n = -\sum_{i=1}^n p_i$$

**Definition:** Define Control Effort (CE) as the shift of the poles, from the open to the closed loop position in the s-plane

$$CE = \sum_{i=1}^{n} (a_i - p_i) = -\sum_{i=1}^{n} (p_i - a_i) = k_n$$

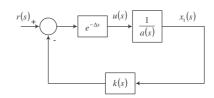

# **Control Effort vs. Time Delay**

• Now, assume a control action time delay  $\Delta$ , and  $P_n >> A_n$ , that is, the loop poles are shifted well on the left

• From the loop frequency transfer function of the system (without delay)

$$G(j\omega) = \frac{k_n (j\omega)^{n-1} + K + k_1}{(j\omega)^n + A_n (j\omega)^{n-1} + K + A_1}$$

$$\left| G(j\omega_c) \right| = 1, \rightarrow 1 \cong \left| \frac{k_n}{j\omega_c + A_n} \right|$$

• That is, an approximate expression for the maximum allowable time delay is given by

$$\rightarrow \omega_c \cong k_n = P_n - A_n$$

$$\Delta < \frac{\psi_m}{P_n - A_n} = \frac{\psi_m}{k_n}$$

©P Albertos 2006

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cours

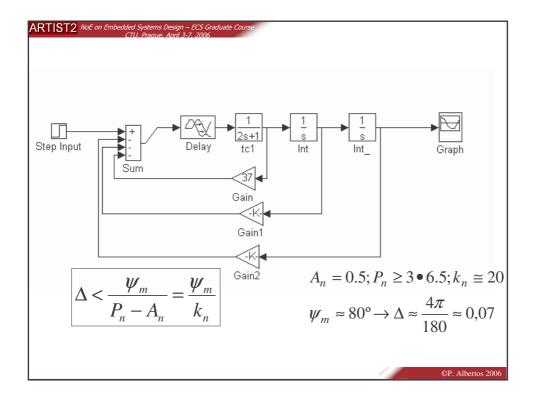

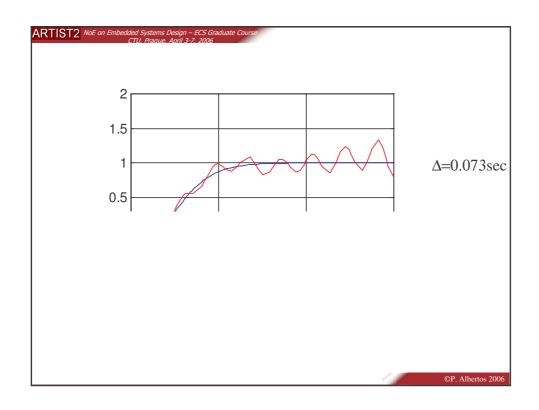

# **Example**

Given the process:

$$G(s) = \frac{1}{s^2(1+2s)}$$

Design a controller to achieve:

- over-damped step response

- 0.5 sec settling time

- Estimate the maximum allowable delay in the loop to keep stability

# **Performance degrading**

- The *Control Effort*, defined as the shift in damping from the open loop poles to the closed loop poles, provides a useful way to obtain the maximum allowable time delay, for both, continuous and discrete systems.

- The longer the sampling period T is, the more sensitive to the time delay the design is.

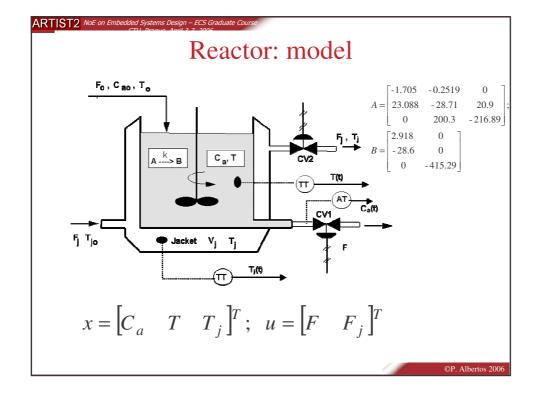

### Reactor: control

$${a_i} = {eig(A)} = {-2.5878, -7.73, -236.987} A_n = -247.3$$

**Control Goal**:  $p = \{-320, -340, -360\}$ .;  $P_n = -1020$

$$K = \begin{bmatrix} 858.5 & 68.5676 & 4.6683 \\ -40.463 & -4.2238 & -0.5505 \end{bmatrix}$$

Assume F active and  $F_i$  open

$$\{eig(A - b_{1.1}k)\} = \{-405.7, -336.1, -49.5\}; \rightarrow S_2 = -791.4$$

$$S_2 - P_n = 228.7$$

©P Albertos 2006

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cou

### Reactor: variables' relevance

The signal relevance depends on the control solution!!

| Variable  | $u_2$  | $u_1$  | $x_1$             | $x_2$   | $x_3$   |

|-----------|--------|--------|-------------------|---------|---------|

| o-l poles | -405.7 | 0.2    | <b>0</b> .71492.9 | -2513.3 | - 340.9 |

|           | -336.1 | -135.6 | -0.4585           | -340.5  | - 225.2 |

|           | -49.5  | -340.6 |                   | -127.2  | ±179.5i |

|           |        |        |                   |         |         |

| S=Sum of  | -719.4 | -475.9 | 1485.1            | -2981   | -719.4  |

| poles     |        |        |                   |         |         |

| Relevance | 228.7  | 544    | 2963.6            | -1961   | 228.7   |

| $= S-P_n$ |        |        |                   |         |         |

# Balance the performances

As a result of the selected controllers and scheduling: *compute Control Effort*

Schedule all the tasks and compute

Delays

Redesign the control taking into account delays Re-compute the *CE* and update the *delays* Check the schedulability

©P. Albertos 2006

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cou

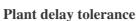

# Performance's balance

Computation delays depend on:

- Operating mode: Control Algorithm Complexity

- Priority

- CPU's load

Delay's effect depends on:

- Sampling period

- Control effort

Performance degrading depends on:

- Sampling period

- Delays

- Loops interaction

$J_D = \sum_{i=1}^{N} K_i \Delta_i$

# Example

**Initial Plants**

$$G_1(s) = \frac{100}{s+6}$$

$G_2(s) = \frac{100}{s+1}$

$$G_2(s) = \frac{100}{s+1}$$

Control Goal:

$$M(s) = \frac{100(s+7)}{s^2 + 13s + 142}$$

Required controllers

$$G_{R,1}(s) = \frac{1}{s+7}$$

$G_{R,2}(s) = \frac{5s+135}{100(s+7)}$

| Plant | $\omega_{c  (rad/sec)}$ | $\psi_{m \text{ (rad)}}$ | $\Delta_{max}$ |  |  |

|-------|-------------------------|--------------------------|----------------|--|--|

| $S_1$ | 7,6                     | 1,41                     | 0,185          |  |  |

| $S_2$ | 11                      | 1,22                     | 0,111          |  |  |

$$G_1(s) = \frac{100}{s + 6}$$

$$G_1(s) = \frac{100}{s+6}$$

$G_2(s) = \frac{100}{s+1}$

Control Goal:

$$M(s) = \frac{100(s+7)}{s^2 + 13s + 142}$$

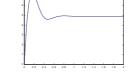

# Multitask system:

$G_{R,1}(s) = \frac{1}{s+7}$   $G_{R,2}(s) = \frac{5s+135}{100(s+7)}$

|    | Table 4. DM scheduling of the 4 tasks |        |        |        |          |      |         |            |         |  |

|----|---------------------------------------|--------|--------|--------|----------|------|---------|------------|---------|--|

|    | WCET                                  | Period | Min.   | Max.   | Average  | CAI  | Control | Degrading  | TOTAL   |  |

|    |                                       |        | Delay  | Delay  | Delay, ∆ | %    | Effort  | (rad)      | degrad. |  |

|    |                                       |        | (msec) | (msec) | (msec)   |      | K       | $K*\Delta$ |         |  |

| T1 | 22                                    | 70     | 22     | 22     | 22       | 0,0  | 0       | 0          |         |  |

| T2 | 15                                    | 100    | 15     | 37     | 26,0     | 22,0 | 7,6     | 0.198      |         |  |

| T3 | 17                                    | 110    | 17     | 54     | 35,5     | 33,6 | 11      | 0.391      |         |  |

| T4 | 19                                    | 110    | 36     | 95     | 65,5     | 53,6 | 11      | 0.720      | 1,309   |  |

#### DM scheduling with CAI reduction

|    | WCET | Period | Min.   | Max.   | Average  | CAI | Control | Degrading | TOTAL   |

|----|------|--------|--------|--------|----------|-----|---------|-----------|---------|

|    |      |        | Delay  | Delay  | Delay, Δ | %   | Effort  | (rad)     | degrad. |

|    |      |        | (msec) | (msec) | (msec)   |     | K       | K*∆       |         |

| T1 | 22   | 70     | 27     | 28     | 27,5     | 1,4 | 0       | 0         |         |

| T2 | 15   | 100    | 39     | 41     | 40,0     | 2,0 | 7,6     | 0,304     |         |

| Т3 | 17   | 110    | 53     | 56     | 54,5     | 2,7 | 11      | 0,600     |         |

| T4 | 19   | 110    | 91     | 95     | 93.0     | 3.6 | 11      | 1.023     | 1,927   |

#### Re-scheduling minimizing the control performance degrading

|    | WCET | Period | Min.   | Max.   | Average  | CAI | <b>Priority</b> | Degrading | TOTAL   |

|----|------|--------|--------|--------|----------|-----|-----------------|-----------|---------|

|    |      |        | Delay  | Delay  | Delay, Δ | %   |                 | (rad)     | degrad. |

|    |      |        | (msec) | (msec) | (msec)   |     |                 | K*∆       |         |

| T1 | 22   | 70     | 56     | 60     | 58       | 5,7 | 3               | 0         |         |

| T2 | 15   | 100    | 94     | 97     | 95,5     | 3,0 | 4               | 0,726     |         |

| T3 | 17   | 110    | 22     | 23     | 22,5     | 0,9 | 1               | 0,247     |         |

| T4 | 19   | 110    | 38     | 40     | 39       | 1,8 | 2               | 0,429     | 1,392   |

#### ARTIST2 NoE on Embedded Systems Design – ECS Graduate Course

# ECS: Control algorithm viewpoint

- Reduced order models

- Non-conventional sampling and updating patterns

- Missing data control

- Event-triggered control

- Hybrid control systems

- Decision and supervisory control

- Multimode control

- Sampling rate changes

- Fault-tolerant control

- Degraded and back-up (safe) control strategies

- Battery monitoring and control

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Coul

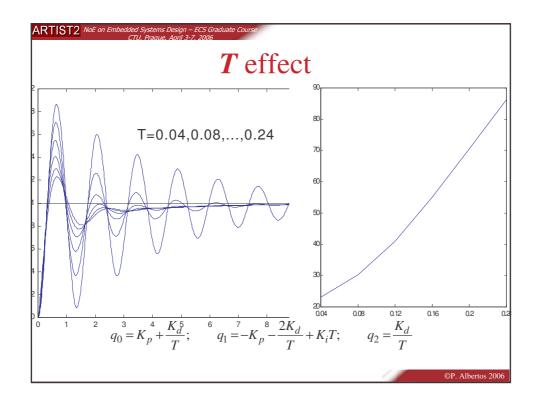

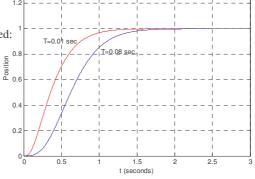

# PID: Sampling period effect

- Open loop control

- Discretized controller, independently of the plant

- Degrading as the sampling period increases

• EXAMPLE: Plant:  $G(s) = \frac{1.5}{(s+0.5)(s+1.5)}$

Parameters:  $K_P = 8$   $T_D = 0.2$   $T_I = 3.2$

Sampling periods: T=0.04, 0.08, ..., 0.24 sec

$q_0 = K_p + \frac{K_d}{T};$   $q_1 = -K_p - \frac{2K_d}{T} + K_i T;$   $q_2 = \frac{K_d}{T}$

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cours

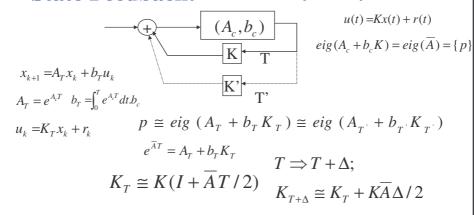

# Variable sampling period

• State Feedback:

$$\mathcal{X}(t) = A_c x(t) + b_c u(t)$$

©P. Albertos 2006

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cours

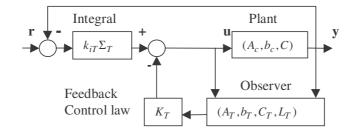

# Output Controller

- Integral error

- Output feedback

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cour

# Observer

$$\begin{aligned} \mathcal{X}(t) = & A_c x(t) + b_c u(t) \\ y(t) = & C x(t) \end{aligned} \qquad \hat{\mathcal{X}}(t) = & A_c \hat{x}(t) + b_c u(t) + L \big[ y(t) - C \hat{x}(t) \big] \\ \hat{\mathcal{X}} = & (A_c - LC) \tilde{x} = A_o \tilde{x} \end{aligned}$$

$$T = e^{A_0 T} = A_T - L_T C \implies L_T = L_0 T + L_1 T^2 / 2 \begin{cases} L_0 = L \\ L_1 = (LCA_c + A_o LC)C^\# \end{cases}$$

We must update the model  $(A_T, b_T)$  as well as the gain  $L_T$

$$T \Rightarrow T + \Delta;$$

$$A_{T+\Delta} = A_T + A_c (I + A_c T) \Delta$$

$$b_{T+\Delta} = b_T + b_c (I + A_c T) \Delta / 2$$

$$L_{T+\Delta} = L_T + (L + A^2 T C^{\#}) \Delta$$

©P Albertos 2006

#### CTU, Prague, April 3-7, 2006

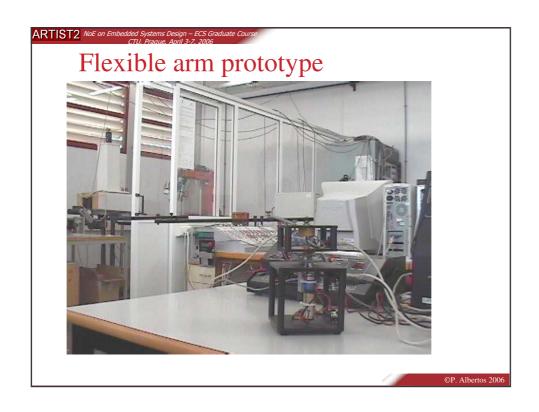

# Flexible arm prototype

# Mathematical model

The dynamical equations of this system are:

$$J \!\!\!\!/ \, q_2 \!\!\!\!/ - K_{_S} q_{_1} = \tau$$

$$D_{q_1} + D_{q_2} + K_s q_1 = 0$$

The torque is generated by the voltage applied to the d.c. motor:

$$V = IR_m + K_e d_2 \Rightarrow I = \frac{1}{R}V - \frac{K_e}{R} d_2$$

in this way

$$\tau = K_e I = \frac{K_e}{R} V - \frac{K_e^2}{R} \phi_2^{\text{R}}$$

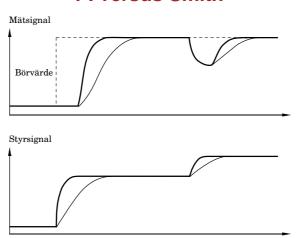

## State+integral feedback control

Controllers' gain,

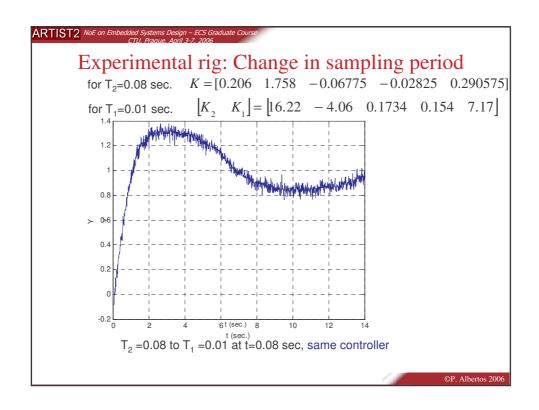

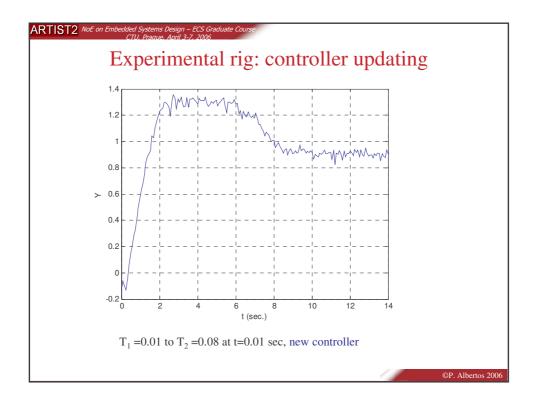

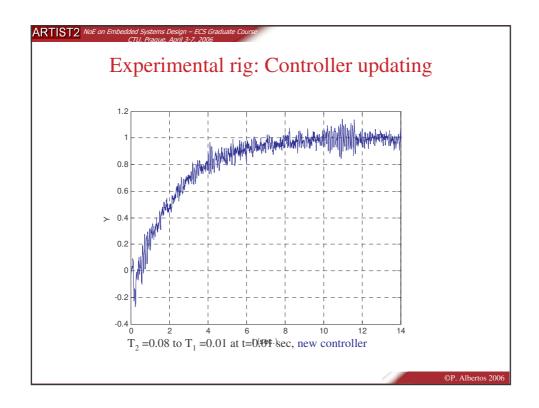

Sampling period effect  $[K_2 \ K_1] = [0.824 \ 7.032 \ -0.271 \ -0.113 \ 1.1623]$

for **T=0.08** sec

for **T=0.01** sec

$\begin{bmatrix} K_2 & K_1 \end{bmatrix} = \begin{bmatrix} 64.91 & -16.25 & 8.173 & 7.2 & 156.61 \end{bmatrix}$

The performance of the controlled system when each controller is applied:

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cours

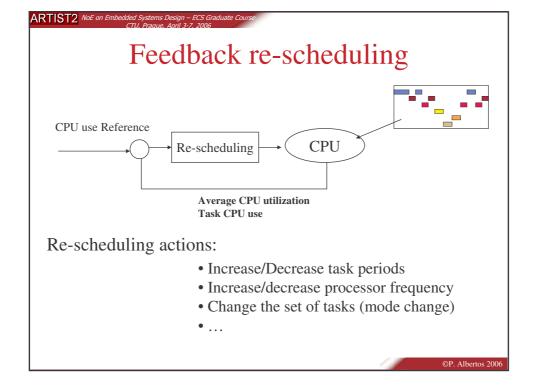

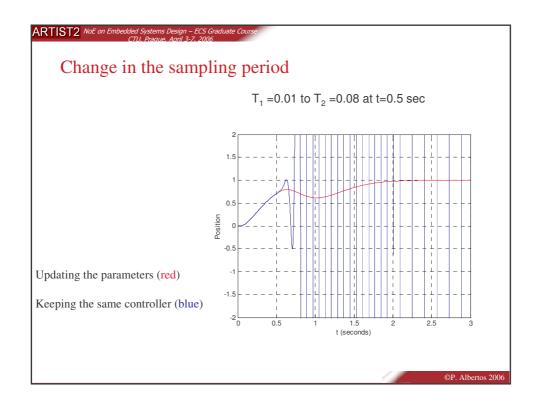

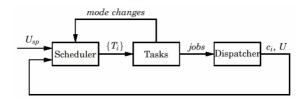

# Feedback re-scheduling

- According to the mode of operation change periods, re-schedule and check if feasible

- Apply transfer controllers

©P. Albertos 2006

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cours

# ECS: Control algorithm viewpoint

- Reduced order models

- Non-conventional sampling and updating patterns

- Missing data control

- Event-triggered control

- Hybrid control systems

- Decision and supervisory control

- Multimode control

- Sampling rate changes

- Fault-tolerant control

- Degraded and back-up (safe) control strategies

- Battery monitoring and control

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cours

# Conclusions

- ES is a growing area of interest

- Software issue

- Control presence

- ECS

- Implementation

- Computational

- Algorithmic

- ECS Design

Graduate Course on Embedded Control System.

Prague Czech Republic April 3-7 2006

# **ARTIST2**

# **Real-Time Issues**

## Alfons Crespo

Universidad Politécnica de Valencia Instituto de Automática e Informática Industrial http://www.gii.upv.es/personal/alfons acrespo@disca.upv.es

03/20/0

© Alfons Crespo 2006

ARTIST2

Graduate Course on Embedded Control System

Prague Czech Republic April 3-7 2006

#### Goals

The goal of this lecture is to provide an overview of the basic concepts of the real-time embedded systems.

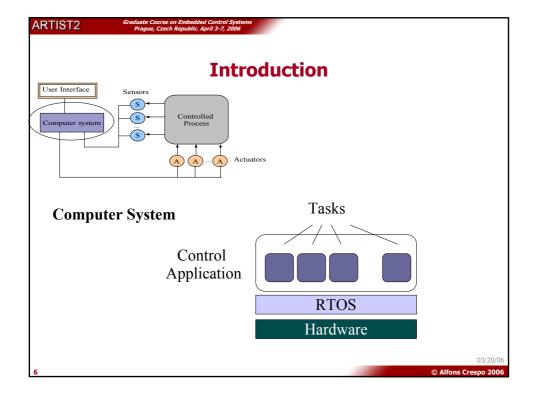

#### **Outline**

- Introduction

- Real-time task model

- Schedulability analysis

- Real-time operating system support

- Real-Time Languages

03/20/0

Alfons Cresno 2006

#### ARTIST2

Graduate Course on Embedded Control System Prague, Czech Republic. April 3-7, 2006

#### **Introduction**

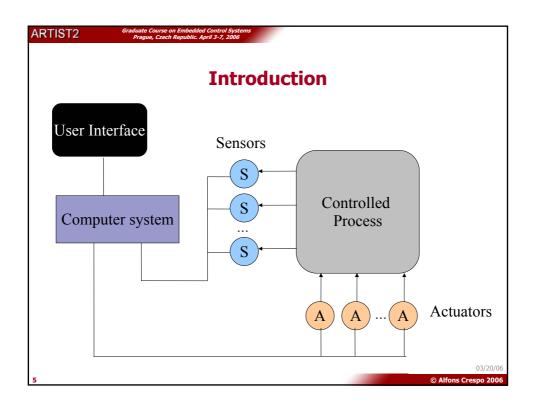

#### **Embedded Control System**

A embedded control system is composed by a **computer system** embedded in **a larger engineering system** and **performing control functions** in all or part of this environment

#### **Examples**

Aerospace systems, trains, cars, robotic systems, communication systems, ......

| ADTICTO | Graduate Course on Embedded C |

|---------|-------------------------------|

| ARTIST2 | Prague, Czech Republic, April |

#### **Characteristics**

#### **Functionality**

- Continuous control

- Discrete event control

- Data display

- Data logging

- Operator commands

- Communications

#### Implementation requirements

- Concurrency

- Timeliness/ dependability

- Reliability

- Special hardware platforms

- Limited resources

- Efficiency

There is a growing need for a larger size and complexity of embedded control systems

03/20/0

© Alfons Crespo 2006

ARTIST2 Graduate Course on Embedded Control Systems

Prague, Czech Republic, April 3-7, 2006

## **Simplification factors**

- Do not use display (specialized displays)

- No disk (no file systems)

- Monouser

- Limited security constraints

- Limited number of tasks

- User access limited

- Closed system

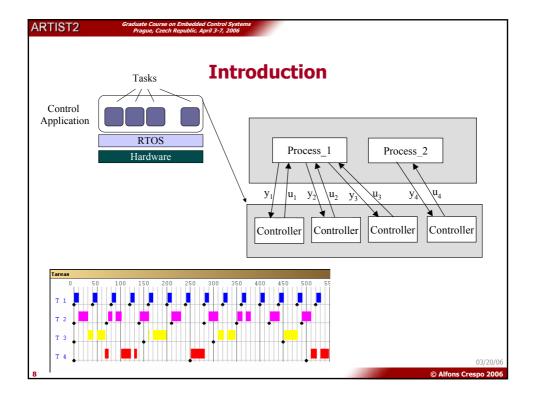

#### **Concurrency**

#### Activities in the real world are simultaneous

- physical variables change at the same time

- events occur asynchronously, and even at the same time

#### Control systems have to cope with this simultaneity

- e.g. multivariable control, asynchronous events

- ... but computers are sequential machines

- different activities must run on the same processor

- simultaneous execution is simulated by multiplexing the usage of the processor among different execution sequences

# Concurrency: multiplexed execution of several activities on a computer

- concurrent activities are called **processes**, threads, or tasks

03/20/0

11

© Alfons Crespo 2006

#### ARTIST2

Graduate Course on Embedded Control System Prague, Czech Republic. April 3-7, 2006

#### **Real-Time**

#### **Concurrent activities with temporal constraints:**

- The actions taken by the computer system have to be produced within a specified interval

- The algorithm (task) result has to be **logically** and **temporally** correct.

#### **Temporal constraints:**

- Sampling of analog variables (sensing) must be periodic

- Control actions must be issued in time (actuation)

- Reactions to events have to be executed within some deadline

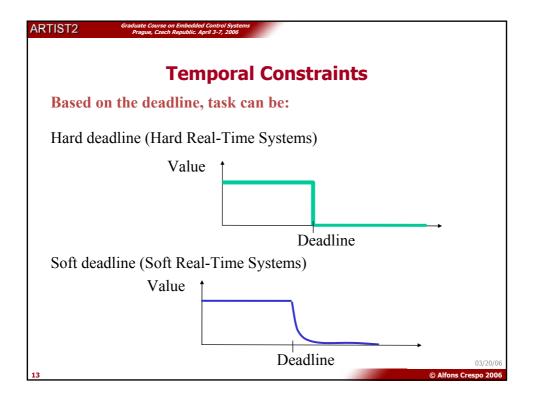

# **Temporal constraints**

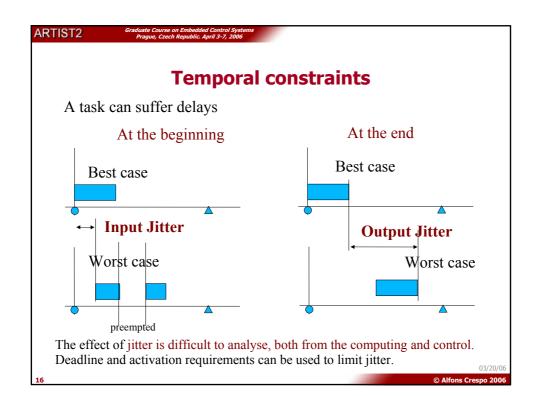

But ... task are executed in a **processor multiplexing** following a **scheduling policy**

So, a task (depending on the scheduling policy) can have several delays.

03/20/0

15

© Alfons Crespo 2006

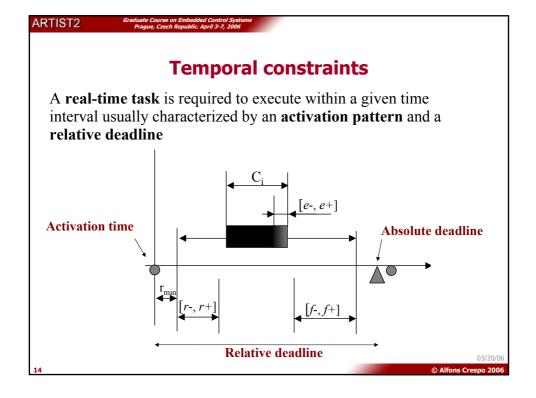

#### **Task Model**

Based on the activation patterns for control tasks

• Periodic: the task is activated at regular intervals with period T

$$Ti = (C_i, D_i, P_i, \phi_i)$$

Activation:

$$a_{\mathbf{k}} = \phi + k \cdot T$$

- **Aperiodic**: the task is activated when some event occurs. Event arrival can be modelled in different ways (e.g. Poisson distribution)

- **Sporadic**: aperiodic, with a minimum inter-arrival time T between activation events

$$a_{k} \ge a_{k-1} + T$$

03/20/0

Alfons Cresno 2006

ARTIST2 Graduate Course on Embedded Control Systems

Prague, Czech Republic, April 3-7, 2006

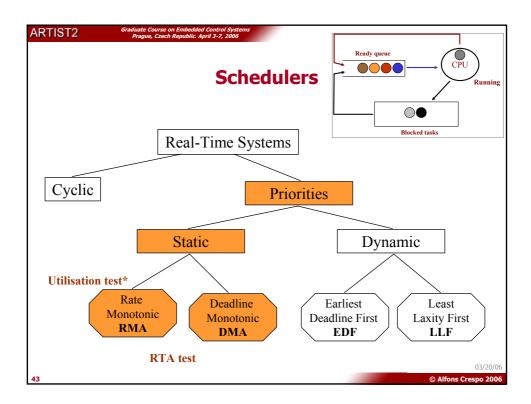

### **Scheduling**

The scheduling algorithm determines which is the next task to be executed.

## **Scheduling**

- ❖ It has a crucial role in ensuring temporal requirements enforcing of activation patterns

- releasing periodic tasks for execution at the proper times

- releasing aperiodic tasks when the activation event is detected

- ensuring minimum inter-arrival time for sporadic tasks

- Implementing appropriate processor sharing algorithms in order to guarantee deadlines

- the aim is not to maximize throughput or to improve average performance, but to guarantee deadlines

- $\bullet$  hard deadlines have to be guaranteed even in worst-case load conditions, i.e.  $Ri \leq Di$

03/20/0

© Alfons Crespo 2006

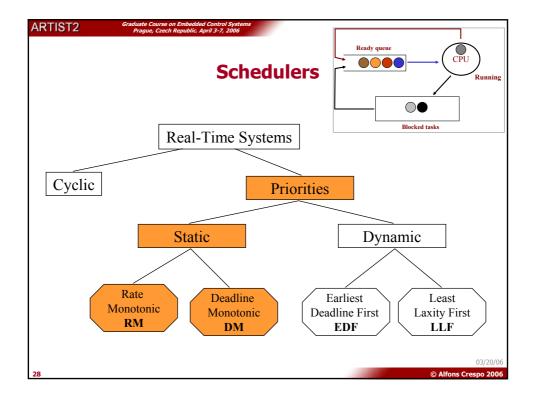

ARTIST2 Graduate Course on Embedded Control Syst Prague, Czech Republic. April 3-7, 2006 Ready queue **Schedulers** Blocked tasks Real-Time Systems Cyclic **Priorities** Static Dynamic Rate Deadline Earliest Least Monotonic Monotonic Deadline First Laxity First RM DM **EDF** LLF

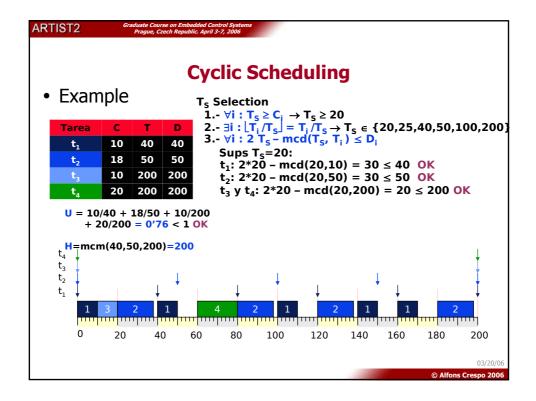

# **Cyclic Scheduling**

Each task is characterised by a tupla (Ci,Ti,Di)

- •Ci is the worst case execution time

- •Ti is the period

- •Di is the deadline

If all **tasks are periodic**, it is possible to design a **fixed execution plan** that is repeated each main cycle Tm

- Main cycle corresponds to the hyperperiod H = mcm(Ti), i=1..n

- Main cycle can be split in **secundary cicles** TS => TM = kTS

03/30/0

© Alfons Crespo 2006

```

ARTIST2 Graduate Course on Embedded Control Syste

Prague, Czech Republic. April 3-7, 2006

```

## **Cyclic Scheduling**

```

procedure Level_Control is

begin

Level := Get Level;

Compute(R Level, Level, ValOut);

Put Valve(ValOut);

end Level Control;

procedure pH_Control is

begin

pH := Get_pH;

Compute (R pH, pH, Val pH);

Put Valve(Val pH);

end pH Control;

procedure Temp Control is

begin

Temp := Get Temp;

Compute(R Temp, Temp, Val Temp);

Put_Valve(Val_Temp);

end Temp_Control;

```

© Alfons Crespo 200

ARTIST2 Graduate Course on Embedded Control Systems Prague, Czech Republic. April 3-7, 2006 **Cyclic Scheduling** Level Control: C1 = 10 ms; P1 = 20 msHyperPeriod = 40msTemp Control: C2 = 5 ms; P2 = 40 msSecondaryCicle = 20ms; pH Control: C3 = 15 ms; P3 = 40 ms**cycle := 0:** Next Activation := Clock; -- get the current time loop delay until Next Activation; **Next Activation := Next Activation + SecondaryCicle ;** case (cycle mod 2) is when 0 => Level Control; Temp Control; when 1 => Level Control; pH Control; end case; LC cycle := cycle + 1; end loop; TC рC 10 15 20 25 30 35 40 45 50 55 60 65 70 75

## Designing a cyclic plan

- Constraints on Secondary Cycle Ts

- 1.- TS any task has to be included

$$\forall i: T_S \geq C_i$$

- 2.- Should be a submultiple of the Main Cycle (**Tp**):

$$Tp = k \cdot Ts$$

3.- A whole T<sub>S</sub> has to be included between an activation and its deadline for any task.

$$\square\square \forall i : 2 T_S - mcd(T_S, T_i) \leq D_i$$

03/20/

© Alfons Crespo 2006

## **Cyclic Scheduling: Summary**

- Robust method, appropriate for simple systems

- temporal behaviour guaranteed by construction

- easy to implement and analyse for correctness

- Too rigid for complex systems

- static schedule difficult to build (NP-hard in the general case)

- changes in code require rebuilding the schedule

- difficult to accommodate sporadic tasks

#### Summary: a low-level method

– more flexible scheduling schemes are easier to implement and maintain

03/20/0

© Alfons Crespo 2006

## **Priority Scheduling**

Priority based is a **scheduling method for real-time** activities using threads or task.

Each **task has a priority** related to some assignement criteria (importance, urgence, ....)

- Priorities can be assigned off-line (**static**) or during the execution based on some parameter (**dynamic**)

- The scheduling policy is implemented in the kernel and selects the **highest priority task** (thread) among the ready tasks.

Schedulers can permit the **preemption or not preemption** of running tasks.

03/20/0

Alfons Cresno 2006

ARTIST2

Graduate Course on Embedded Control System

#### **Fixed Priority Scheduling**

Fixed Priority preemptive scheduling: Priorities are assigned at design time

#### Criteria:

- Designer decides the priority based on the importance of the task (semantic criteria)

- Based on the urgence (deadline):

- **❖ Rate Monotonic** (periods = deadline). Higher priority to more frequent tasks

- ❖ Deadline Monotonic: Higher priority to more urgent task (Shorter deadline)

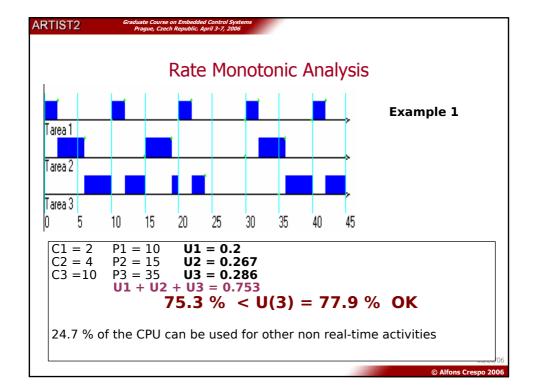

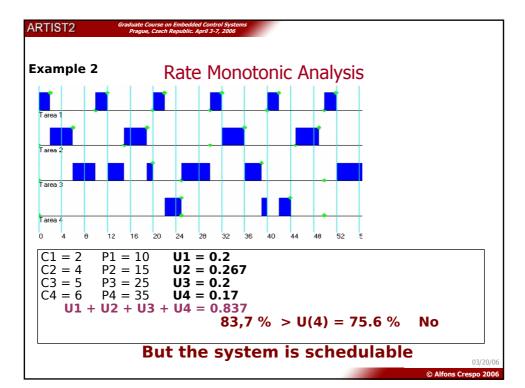

## **Rate Monotonic Analysis**

#### **Assumptions:**

- Periods = Deadlines

- Tasks are independent (no shared resources)

**Analysis:** Utilisation based feasibility test (Liu & Layland, 73):

A task

$$T_i = (C_i, P_i)$$

, uses the CPU  $U(1) = \frac{C_i}{P_i}$

For *n* tasks:

$$\frac{C_1}{P_1} + \frac{C_2}{P_2} + ... + \frac{C_n}{P_n} \le U(n) = n \cdot (2^{\frac{1}{n}} - 1)$$

Utilisation bound for n tasks

| 1 | 1,00 |

|---|------|

| 2 | 0,82 |

| 3 | 0,77 |

| 4 | 0,75 |

| 5 | 0,74 |

|   |      |

| 8 | 0,69 |

n U(n)

It is sufficient but not necessary condition

03/20/0

© Alfons Crespo 2006

31

ARTIST2 Graduate Course on Embedded Prague, Czech Republic. Ap

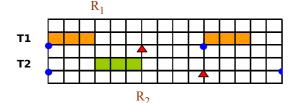

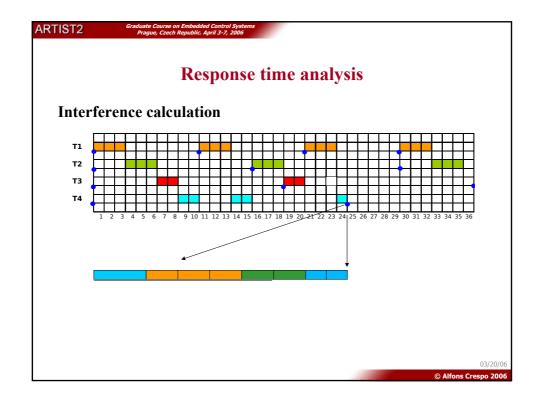

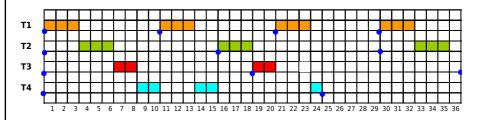

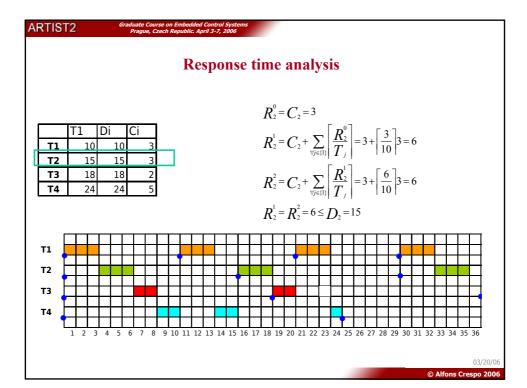

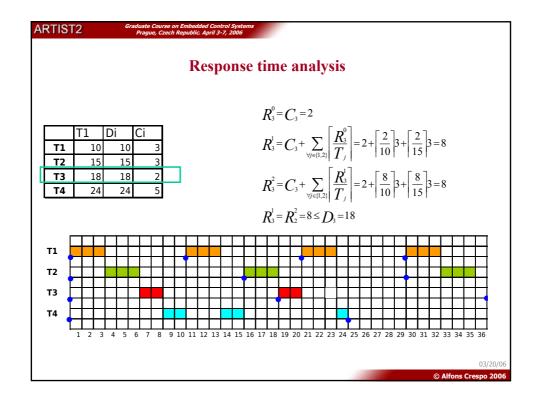

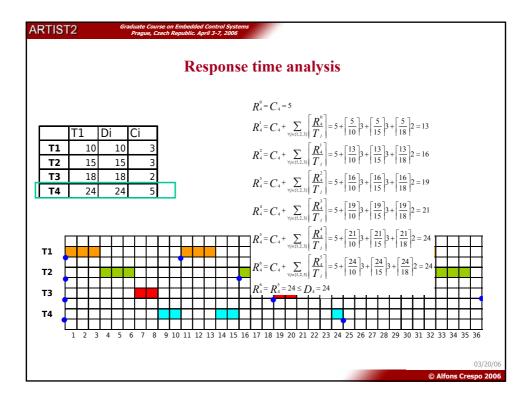

# Response time analysis

A set of n periodic tasks is schedulable under any priority assignment iff: All tasks finish its execution in the first period before the deadline (Critical instant)  $R_i \leq D_i$

The worst case response time (Ri) of a task Ti occurs when all taks with higher priority start at the same time than Ti.

$$R_i = C_i + I_i$$

$$I_i = \sum_{j \in \mathit{hp}(i)} \left\lceil \frac{W_i}{T_j} \right\rceil C_j$$

$$I_i^j = \left\lceil \frac{W_i}{T_j} \right\rceil C_j$$

$$I_2^1 = \left\lceil \frac{6}{10} \right\rceil \bullet 3 = 3$$

## Response time analysis

#### **Critical Instant**

The value of interference  $(\mathbf{I_i})$  depends on the relative phases of the task activation times

**Ii** is maximum when a task is activated at the same time as all the tasks with a higher priority

It suffices to compute interference for the first period after a critical instant – no need for a full hyperperiod

This reduces complexity of analysis to polynomial case

03/20/0

Alfons Cresno 2006

# Response time analysis

$$\text{\bf Ri can be determined by:} \quad R_i = C_i + \sum_{j \in \mathit{hp}\,(i)} \left\lceil \frac{R_i}{T_j} \right\rceil * C_j$$

$$R_i^0 = C_i$$

It can be solved by a linear iteration:

$$R_i^{n+1} = C_i + \sum_{j \in hp(i)} \left[\frac{R_i^n}{T_j}\right] C_j$$

Termination condition

$$R_i^{n+1} = R_i^n$$

The system is schedulable if for all task

$$R_i^{n+1} \leq D_i$$

03/20/06

© Alfons Cresno 2006

#### ARTIST2 Graduate Course on Embedded Control System Prague, Czech Republic. April 3-7, 2006

#### Response time analysis

|   |    | T1 | Di | Ci |   |

|---|----|----|----|----|---|

| П | T1 | 10 | 10 | 3  |   |

| 1 | T2 | 15 | 15 | 3  | Г |

|   | Т3 | 18 | 18 | 2  |   |

|   | T4 | 24 | 24 | 5  |   |

$$R_1^0 = C_1$$

$R_1^1 = C_1 + 0 = 3 \le D_1 = 10$

#### ARTIST2

Graduate Course on Embedded Control System

#### **Extending Response Time Analysis**

#### RTA can be extended to more complex task models

- tasks with any priority assignement

- deadlines shorter than periods

- sporadic tasks

- communication with shared variables

- activation jitter

... and also to distributed systems

– provided the communication link has a bounded transmission time

The computation models covered by RTA can be implemented on a number of operating systems and programming languages

This enables many kinds of real-time systems to be built and analysed for deadline guarantees

- mandatory in high-integrity systems

#### ARTIST2 Graduate Course on Embedded Control Systems Prague, Czech Republic. April 3-7, 2006

### **Sporadic tasks**

#### Sporadic events are characterized by a minimum inter-arrival time T

The worst case is when the task is activated as often as possible

• pseudo-periodic activation with period T

Sporadic tasks are converted (from the analysis point of view) in periodic task with period equal T and, usually, deadlines shorter than T

the pseudo-periodicity assumption: sporadic tasks behave as periodic tasks in the worst case

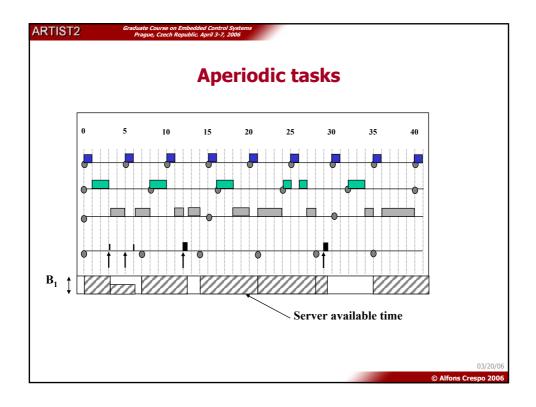

# **Aperiodic tasks**

Aperiodic events are characterized by different kinds of models, most of them stochastic

- e.g. Poisson process

Aperiodic tasks do not usually have any hard deadlines but are required to respond as fast as possible

Aperiodic tasks can be scheduled in a DMS framework using a variety of aperiodic servers

An aperiodic server is a periodic task serving aperiodic events with a limit of computation by period (budget)

$$S_i = (B_i, P_i)$$

- In general, the budget is replenished each period

- As a periodic task it can be integrated into RTA

03/20/0

© Alfons Crespo 2006

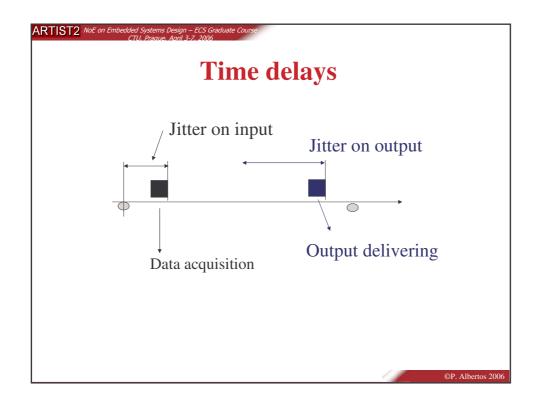

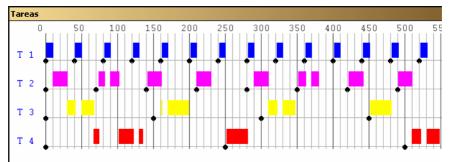

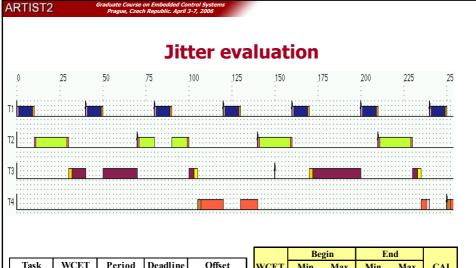

#### **Jitter evaluation**

- Output jitter can play an important role in the control performance

- Tasks are pseudo-periodic

- The distance between two consecutives input or outpus is variable

- Important aspect: determine the Input/Output Jitter.

03/20/0

Alfons Cresno 2006

#### ARTIST2

Graduate Course on Embedded Control System

#### **Jitter evaluation**

Worst case response time => Maximum finishing time of the task:

$$WC_i^{n+1} = C_i + \sum_{j \in hp(i)} \left[ \frac{WC_i^n}{T_j} \right] C_j$$

Best case response time => Minimum initial time of the task:

$$BC_i^{n+1} = C_i^{\min} + \sum_{j \in hp(i)} \left\lceil \frac{BC_i^n - T_j}{T_j} \right\rceil C_j^{\min}$$

Control Action Interval

$$CAI_{i} = \frac{WC_{i} - BC_{i}}{T_{i}}$$

| Task | WCET | Period | Deadline | Offset |

|------|------|--------|----------|--------|

| T1   | 10   | 40     | 40       | 0      |

| T2   | 20   | 70     | 70       | 0      |

| T3   | 35   | 150    | 150      | 0      |

| T4   | 30   | 250    | 250      | 0      |

|      | Begin |     | E   |     |     |

|------|-------|-----|-----|-----|-----|

| WCET | Min   | Max | Min | Max | CAI |

| T1   | 0     | 0   | 10  | 10  | 0%  |

| T2   | 0     | 10  | 20  | 30  | 14% |

| Т3   | 0     | 20  | 45  | 105 | 40% |

| T4   | 0     | 105 | 30  | 240 | 84% |

03/20/0

Alfons Cresno 2006

ARTIST2

Graduate Course on Embedded Control System

# **Jitter reduction**

A simple way to reduce the Jitter in a fixed priority scheme is to increase the priority of the task.

- \* Reducing the deadline of a task (DM assignement)

- Increasing the priority

Reduction of the jitter in a task produce an increase in others. But not all tasks are equal sensible to higher jitter.

Other alternatives are also possible:

- Task partitioning

- ❖ Bands of priorities for Input/Output/computation phases

- **\*** .....

Prague, Czech Republic. April 3-7, 2006

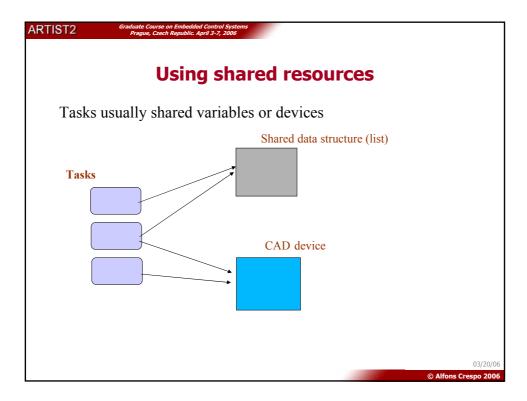

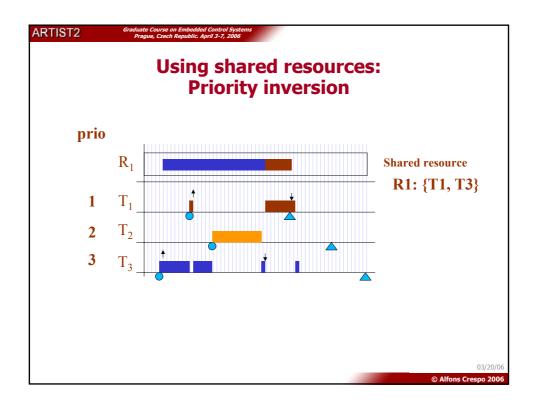

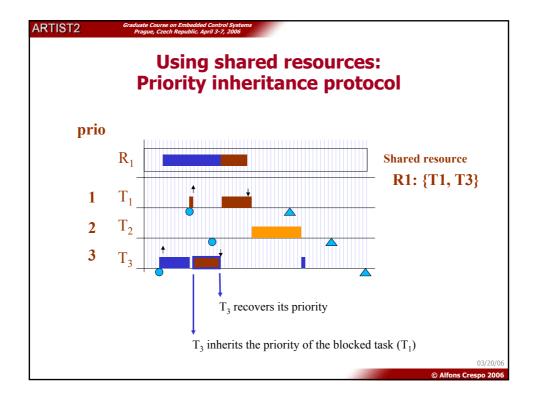

# **Using shared resources**

- Code segments in which shared data are accessed are called critical sections

- ❖ Shared data must be protected so that critical sections are executed in mutual exclusion

operating systems provides many mechanisms: semaphores, mutexes, Ada protected objects

- ❖ In real-time systems, mutual exclusion may give rise to priority inversion this effect is also called blocking

- an undesirable side effect of mutual exclusion

- it can even affect tasks not sharing any variables

- it can produce unbounded blocking

This may result in unbounded response times

Prague, Czech Republic. April 3-7, 2006

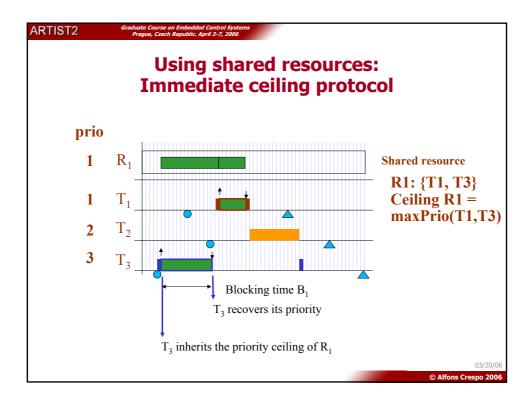

# **Immediate ceiling protocol**

- ❖ A high-priority task blocks at most once in each execution cycle

❖ It is independent of how many shared data items it uses

- The maximum duration of blocking for a task Ti equals the duration of the longest critical section executed by a lower-priority task using a data item with a ceiling priority greater or equal to the priority of Ti

- The are no deadlocks, in spite of possible circular wait situations

- ❖ The effect of (bounded) blocking can be added to the response time equation:

$$R_{i} = C_{i} + B_{i} + \sum_{j \in hp(i)} \left[ \frac{R_{i}}{T_{i}} \right] * C_{j}$$

# **Real-time Operating Systems**

- Provides infrastructure for running software on an embedded hardware platform

- Provides a hardware abstraction

- Provides access to the devices

- Provides support for multiple processes and threads

- Provides development tools

- Compiler / Linker

- Downloader

- Debugger

- Provides deterministic performance

- Guaranteed interrupt management Latency

- Guaranteed Context Switch

- Small and bounded scheduling overhead

- · Timer and clock access

## ARTIST2

Graduate Course on Embedded Control System Prague, Czech Republic. April 3-7, 2006

# **RTOS** requirements

- Real-time task scheduling

- Preemptive scheduling

- Interrupt response guarantee

- Static or dynamic priorities

- Synchronous and Asynchronous I/O

- Fast data acquisition

- Deterministic network communications

- Portability

- Efficient memory management

- Real-Time languages support

- Standard API (POSIX®)

# **Commercial RTOS**

# Interrupt handling Scheduling

- FIFO or Round-robin for equal-priority threads (EDF scheduling is not provided)

- Priority inversion control (PIP)

# **Memory management**

- Virtual memory (not pagination)

- Memory protection (some of them)

- LynxOS

- pSOS

- Most of them provide real-time extensions

- QNX

- VRTX

- VxWorks

- .....

## ARTIST2

Graduate Course on Embedded Control System Prague, Czech Republic. April 3-7, 2006

# **Open Source RTOS**

## **Real-Time Linux:**

RT-Linux

KURT RTEMS RED Linux ORK

RTAI MARTE OS (Ada)

Linux/RK (from Mach/RK)

## **Embedded Linux**

MiniRTL

Extension to RTLinux (OCERA)

ELKS project

HA-Linux (High Availability)

Lineo Embeddic VME Linux Project

# **Open Source RTOS**

|                     | Linux 2.4                                        | RTLinux/GPL            | RTAI                              | OCERA                                     |

|---------------------|--------------------------------------------------|------------------------|-----------------------------------|-------------------------------------------|

| Processors          | 1386, PPC, ARM, SH, m68k,<br>PARISK, Sparc, MIPS | 1386, PPC*, ARM*       | 1386, PPC, ARM,<br>m68k, M1PS     | 1386, PPC*, ARM*                          |

| Multi-processors    | Yes                                              | Yes                    | Yes                               | Yes                                       |

| Process             | Yes                                              | No                     | No                                | No                                        |

| Threads             | Yes                                              | Yes                    | Yes                               | Yes                                       |

| Scheduling policies | FIFO, RR                                         | FIFO, EDF,<br>SPORADIC | FIFO                              | FIFO, EDF,<br>SPORADIC, CBS,<br>IRIS, ADS |

| Priority inversion  | None                                             | Ceiling                | Inheritance                       | Ceiling                                   |

| Priority range      | 0-100                                            | 0-100000               | 0x3fffFfff-0                      | 0-100000                                  |

| Protected memory    | Yes                                              | No                     | No                                | Yes                                       |

| Dynamic memory      | Yes                                              | No                     | Yes                               | Yes                                       |

| Semaphores          | Yes                                              | Yes                    | Yes                               | Yes                                       |

| Mutex               | Yes                                              | Yes                    | Yes                               | Yes                                       |

| M essage queues     | No                                               | No                     | Yes                               | Yes                                       |

| Barriers            | No                                               | No                     | No                                | Yes                                       |

| rd/wr locks         | No                                               | No                     | No                                | No                                        |

| Signals             | Yes                                              | No                     | No                                | Yes                                       |

| Timers              | No                                               | No                     | No                                | Yes                                       |

| Execution Timers    | No                                               | No                     | No                                | Yes                                       |

| Time resolution     | Configurable (HRT)                               | Configurable           | Configurable                      | Configurable                              |

| User timers         | Yes                                              | No                     | No                                | Yes                                       |

| Network             | IP, UDP, TCP,                                    | No                     | IP, UDP                           | IP, UDP, TCP,                             |

| Filesystems         | Ext2/3, ReiserFS, DOS, RAM, Flash, XFS, QNX4,    | No                     | No                                | Yes                                       |

| API's               | POSI X, pSOS, VxWorks                            | POSI X 1003.1c, PSE    | Custom, POSIX<br>1003.1c (compat) | POSI X 1003.1c, PS                        |

## ARTIST2

Graduate Course on Embedded Control System Prague, Czech Republic. April 3-7, 2006

# **Real-Time Programming Languages**

- Sequential languages as **C/C++ languages** do not support directly real-time facilities

- Facilities are supported by OS API (POSIX or other API)

- Ada was specifically designed for embedded real-time systems

- Provides support for real-time and concurrency and protected objects

- **Java** provides support for threads and protected shared data. But it does not provide support for real-time

- RTSJ: A specification for Real-Time Java

# Ada

- ❖ Ada supports many real-time concepts at the programming language level

- concurrency

- protected shared data

- fixed priority scheduling & ICPP

- - device & interrupt drivers

- ❖ Ada 95 is the current standard, Ada 2005 to come soon

- Ravenscar profile for high-integrity systems

- additional scheduling methods

- Java-like interfaces

- execution-time clocks

- etc.

03/20/0

Alfons Crespo 2006

ARTIST2

Graduate Course on Embedded Control System Prague, Czech Republic. April 3-7, 2006

# **RTJava**

- ❖ Java extension for real-time systems

- developed by the Real-Time for Java Expert Group (version 1.0, 2001)

- Extensions of Java computation model in several areas

- scheduling

- memory management

- synchronization

- event handling

- physical memory access

- **❖** Implementations available

- - TimeSys, AICAS (Jamaica)

...but not so mature as Ada

# **Summary**

- \* Real-time systems have temporal requirements

- not just functionally correct, things must be done in time

- Scheduling is crucial in guaranteeing and analysing temporal behaviour

- timing properties depend on the way processor & other resources are shared

- ❖ Analysable task model based on fixed-priority scheduling

- deadline or rate-monotonic priorities

- controlled access to shared data

- extensible to offsets, jitter, distributed systems, etc.

- Other scheduling methods

- EDF (earliest-deadline first)» efficient but no so robust

- Static, time-driven scheduling » robust, but complex to implement

03/20/0

© Alfons Crespo 2006

# Embedded Control Systems: Control Kernel

# P. Albertos

Universidad Politécnica de Valencia \* Dept. of Systems Engineering and Control, E-46071 Valencia, Spain. Fax: +34 96 3879579 e-mail: pedro@aii.upv.es

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cour

# The kernel concept

# OS kernel:

- Basic services:

- Task and time management

- Interrupt handling

- Interface to the applications (API)

- Mode changes

- Fault tolerance

- Additional services

- File management

- Quality of service

- Tracing and debugging

```

Control task

...

loop

convert _sensor _analog_ digital (y);

compute _control _action (u);

compute _error (e)

compute _control _action (u)

send _ converted _ control_ action (u);

update_internal_variables(y,u, ...);

Next _Iteration:= Next _Iteration + Period;

delay until Next _Iteration;

end loop;

...

```

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cours

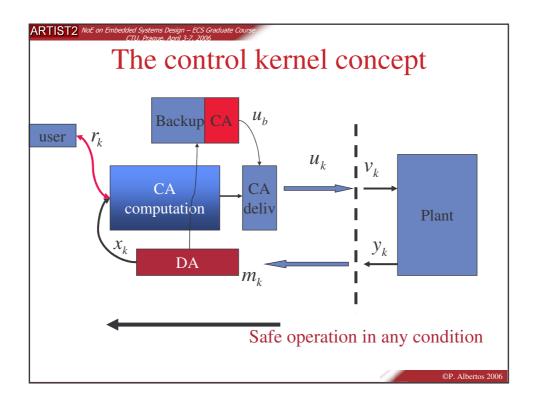

# The Control Kernel concept

- Ensures control action (CA) delivering

- Data acquisition of major signals

- Transfer to new control structure

- Additional CA computing facilities

- Communication facilities

- Coordination facilities

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cours

# Control Kernel (4)

- Communication facilities

- with the environment

- the operator

- other ECS

- Coordination facilities

©P. Albertos 2006

ARTIST2 NoE on Embedded Systems Design – ECS Graduate Cours

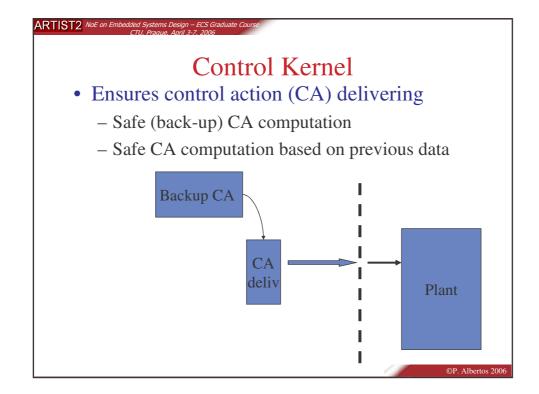

# **Control Kernel**

- Ensures control action (CA) delivering

- Safe (back-up) CA computation

- Safe CA computation based on previous data

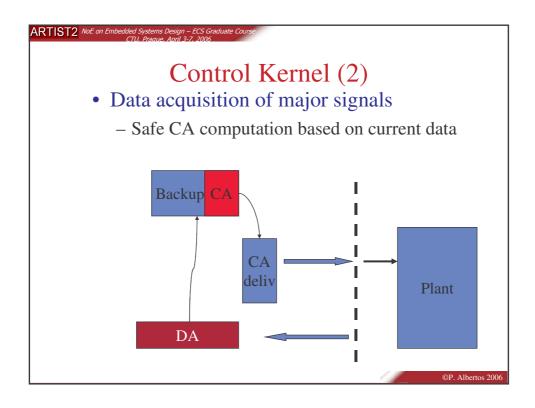

- Data acquisition of major signals

- Safe CA computation based on current data

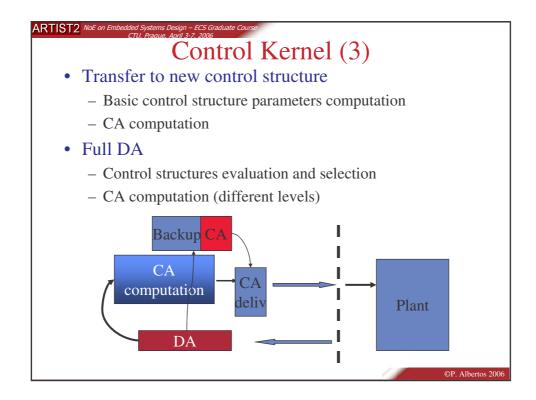

- Transfer to new control structure

- Basic control structure parameters computation

- CA computation

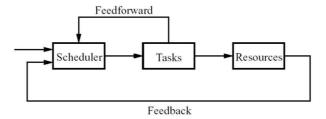

- Full DA