## **Automatic Code Generation**

Several tools allow automatic code generation from high-level control models:

- Simulink Real-Time Workshop (Mathworks)

- Scicos (Inria)

- Lustre/SCADE (Verimag/Esterel-Tecnologies)

- Targetlink (DSpace)

- ASCET (ETAS)

This presentation is mostly based on our experience of the Lustre/SCADE Simulink Gateway and Code Generator.

### Model-Based Development \_\_\_\_\_

These tools open the way to the Model-Based development method

- Design and validation on models (Simulink, Scicos)

- Automatic deployment on a given architecture guarentying faithfulness

This method avoids the manual coding phase which is error-prone. It places the computerised control field ahead with respect to other computing fields

# **Steps in Code Generation** \_\_\_\_

We first focus here on single thread code generation.

- Type inference

- Clock inference

- Code organisation

- Equation sorting

- Optimisation

# **Type Inference** \_\_\_\_

Simulink/Stateflow is a partially typed system:

The user needs not care about types

Yet the resulting code should be typed.

$\Rightarrow$  need for type inference

This is the same situation as in functional languages (OCaml, Haskell). We can apply here the techniques that have been studied there (Hindley-Milner):

- writing type equations

- soving them by unification algorithm

# Writing Type Equations \_\_\_\_\_

Starting points:

- Blocks have a signature imposing type relations on their inputs and outputs

- The user can impose types in some blocks

## Simulink Types \_

$SimT = \{type \ variables\} \cup SimNum \cup \{boolean\}$

$SimNum = \{numerical type variables\} \cup \\ \{double, single, \\ int8, uint8, \\ int16, unit16, \\ int32, uint32\}$

#### **Block Type Signatures** \_

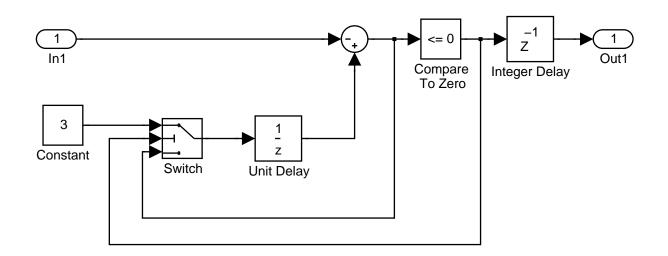

Constant<sub> $\alpha$ </sub> :  $\alpha, \alpha \in SimT$ Adder :  $\alpha \times \cdots \times \alpha \to \alpha, \alpha \in SimNum$ Gain :  $\alpha \to \alpha, \alpha \in SimNum$ Relation :  $\alpha \times \alpha \rightarrow boolean, \alpha \in SimT$ Switch :  $\alpha \times \beta \times \alpha \to \alpha, \alpha, \beta \in SimNum$ *Logical Operator* : *boolean*  $\times \cdots \times$  *boolean*  $\rightarrow$  *boolean* Discrete Transfer Function : double  $\rightarrow$  double *Zero-Order Hold, Unit Delay* :  $\alpha \rightarrow \alpha, \alpha \in SimT$ Data Type Converter  $\beta \rightarrow \alpha, \alpha, \beta \in SimT$ InPort, OutPort :  $\alpha \to \alpha, \alpha \in SimT$

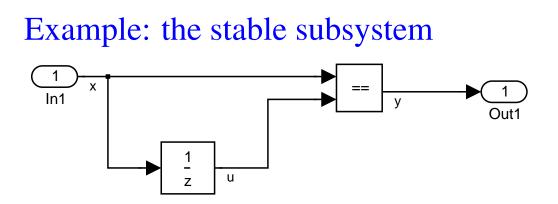

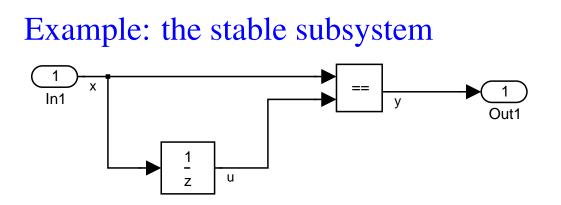

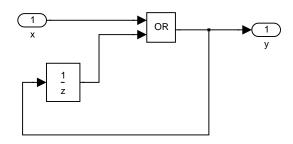

# Writing and Solving Type Equations \_

How to solve this system of equations?

$\begin{array}{rcl} \text{type equations:} \\ \frac{1}{z} & : & tu = tx \\ = = & : & \begin{cases} tx = tu \\ ty = boolean \end{cases} \end{array}$

# Writing and Solving Type Equations \_

$\begin{array}{rcl} \text{type equations:} \\ \frac{1}{z} & : & tu = tx \\ = = & : & \begin{cases} tx = tu \\ ty = boolean \end{cases} \end{array}$

How to solve this system of equations?

Let's eliminate the type variable tu

This amounts to unify tx and tx which unify trivially.

Thus we get

$stable: tx \rightarrow boolean$

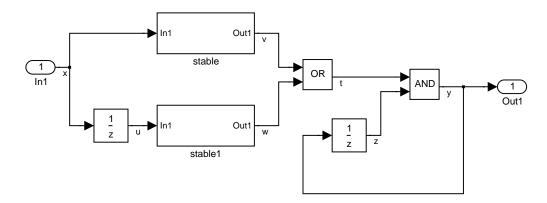

# Writing and Solving Type Equations

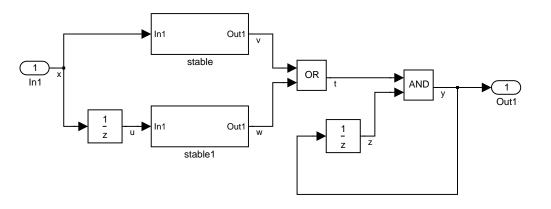

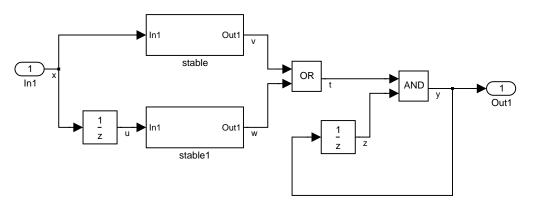

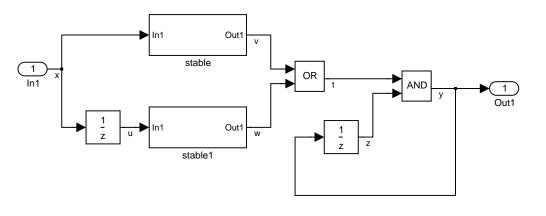

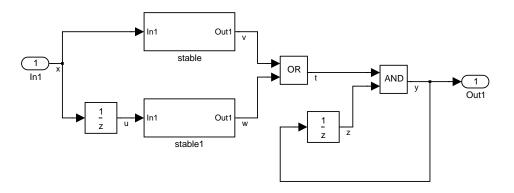

More involved: the monitor subsystem

type equations:

# Writing and Solving Type Equations

#### More involved: the monitor subsystem

#### type equations:

| $\frac{1}{z}$ | : | tu = tx                |

|---------------|---|------------------------|

| stable        | : | tv = boolean           |

| stable1       | : | tw = boolean           |

| OR            | : | tv = tw = tt = boolean |

| AND           | : | tt = tz = ty = boolean |

| $\frac{1}{z}$ | : | tz = ty                |

|               |   |                        |

# Writing and Solving Type Equations

More involved: the monitor subsystem

We get ty = boolean and thus:

type equations:

| $\frac{1}{z}$ | : | tu = tx                |

|---------------|---|------------------------|

| stable        | : | tv = boolean           |

| stable1       | : | tw = boolean           |

| OR            | : | tv = tw = tt = boolean |

| AND           | : | tt = tz = ty = boolean |

| $\frac{1}{z}$ | : | tz = ty                |

|               |   |                        |

$monitor: tx \rightarrow boolean$

# Other Type Analysis \_\_\_\_\_

- Complex Signals

- Signal dimensions

Follow the same lines

## **Clock Inference** \_\_\_\_\_

An important question: when should the implementation compute?

A new issue that doesn't exist in classical computing.

Yet the same typing techniques can apply:

- writing clock equations

- soving them by unification

## Simulink Clocks \_

- Periodic clocks defined by:

a rational positive period π ∈ Q<sup>+</sup>

and a rational positive phase θ < π</li>

- Triggers, akin to boolean signals

- Clock variables

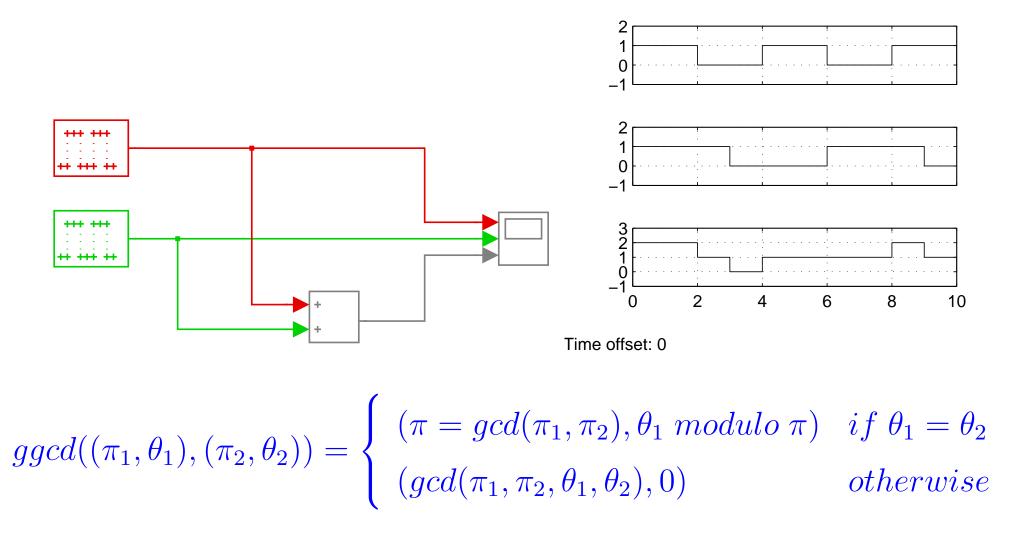

# The GCD Rule

When a block has several inputs with different sample times, the output sample time is given by the generalised gcd rule:

# The GCD Rule -

When a block has several inputs with different sample times, the output sample time is given by the generalised gcd rule:

$$ggcd((2,0), (3,0)) = (gcd(2,3), 0)$$

= (1,0)

## **Useful Simplifications** \_

• ggcd is associative commutative. So we can write:

ggcd(a, b, c) = ggcd(a, ggcd(b, c))

- ggcd(a, a, b) = ggcd(a, b)

- The solution of a = ggcd(a, b)

is a = b

#### **Simulink Clock Signatures**

Sources\_1 :  $\alpha$  $Sources_{(\pi,\theta)}$  :  $(\pi,\theta)$ Maths<sub>-1</sub> :  $\alpha_1 \times \alpha_2 \ldots \times \alpha_n \to ggcd(\alpha_1, \alpha_2, \ldots, \alpha_n)$  $Maths_{(\pi,\theta)}$  :  $\alpha_1 \times \alpha_2 \ldots \times \alpha_n \to (\pi,\theta)$  $Discrete_{-1} : \alpha \to \alpha$  $Discrete_{(\pi,\theta)} : \alpha \to (\pi,\theta)$ Sinks\_1 :  $\alpha \rightarrow \alpha$  $Sinks_{(\pi,\theta)} : \alpha \to (\pi,\theta)$

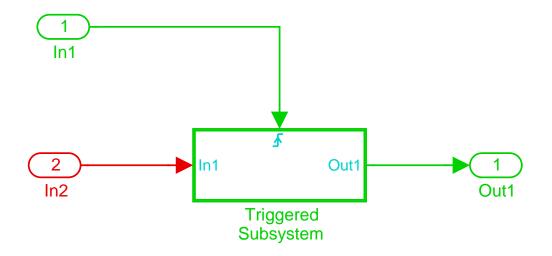

#### **The Triggered Subsystem Inference Rule** \_\_\_\_\_

$\begin{array}{rrrr} if & S & : & \alpha^m \to \alpha^n \\ \\ and & b & : & \beta \\ \\ then & S^{\hat{b}} & : & b^m \to \beta^n \end{array}$

where  $S^{\hat{b}}$  means: the subsystem S triggered by the signal b

This amounts to saying that a triggered subsystem should have a single clock and that once triggered by a signal, it executes only when the trigger is active and then its outputs are hold when the trigger is inactive.

#### **The Triggered Subsystem Inference Rule** \_

$\begin{array}{lll} if & S & : & \alpha^m \to \alpha^n \\ and & b & : & \beta \\ \\ then & S^{\hat{b}} & : & b^m \to \beta^n \end{array}$

#### where $S^{\hat{b}}$ means: the subsystem S triggered by the signal b

This amounts to saying that a triggered subsystem should have a single clock and that once triggered by a signal, it executes only when the trigger is active and then its outputs are hold when the trigger is inactive.

## **Clocking the single thread case** \_\_\_\_

Clock inference provides us with a basic clock

- either the fastest periodic clock

- or a clock variable, if there is no periodic clock in the design

In any case, every other clock of the system is slower and can be considered as a trigger.

In case of periodic clocks, these triggers are implicite and we must make them explicit by means of clock dividers and phasers

## **Clocking the single thread case** \_\_\_\_

Clock inference provides us with a basic clock

- either the fastest periodic clock

- or a clock variable, if there is no periodic clock in the design

In any case, every other clock of the system is slower and can be considered as a trigger.

In case of periodic clocks, these triggers are implicit and we must make them explicit by means of clock dividers and phasers

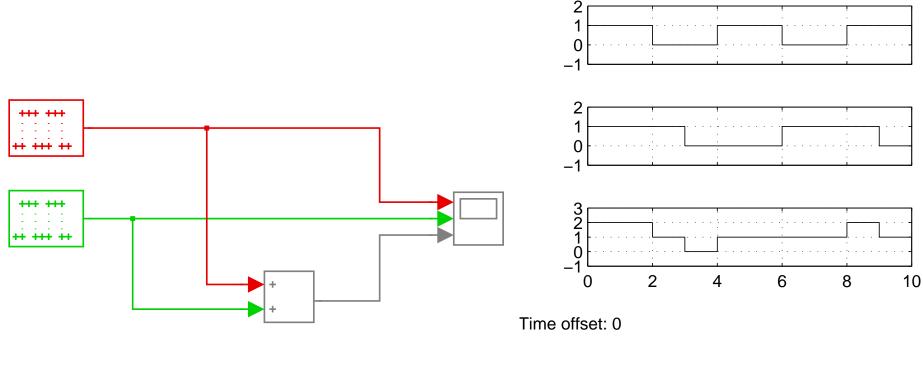

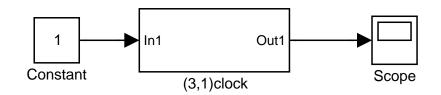

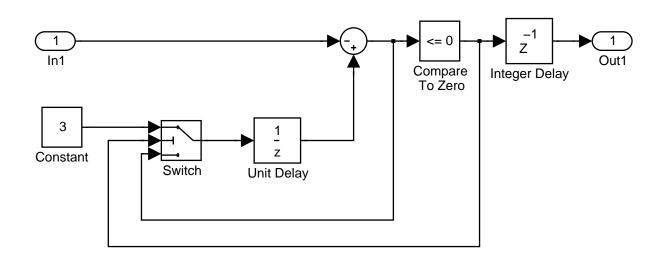

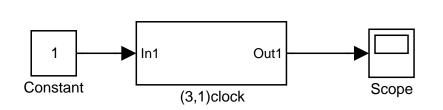

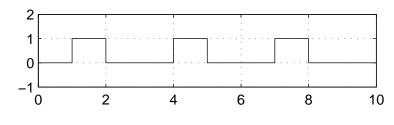

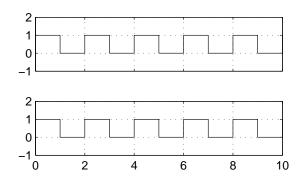

## Example: A (3,1) clock \_\_\_\_\_

# Example: A (3,1) clock \_

Time offset: 0

## **From Subsystems to Difference Equations** \_\_\_\_\_

A single-clock subsystem is a system of difference equations

$$U(0),$$

$$U(n+1) = F(U(n), X(n))$$

$$Y(n) = G(U(n), X(n))$$

where

- U, vector of state variables

- X, vector of inputs

- *Y*, vector of outputs

- *F*, state transition function,

- *G*, output function,

### **From Difference Equations to Programs** \_\_\_\_\_

The idea is to build on object-oriented programming ( $C^{++}$ , Java)

| Simulink            | Object-Oriented  |

|---------------------|------------------|

| system of equations | class            |

| state variables     | class attributes |

| initialisation      | object creation  |

| functions           | class methods    |

### **From Difference Equations to Programs** \_

U(0),

Y(n) = G(U(n), X(n))U(n+1) = F(U(n), X(n))

```

class subsyst{

private :

state u ;

public :

subsyst(state u_init) {

u = u_init;

}

output step(input x) {

state up;

output y = q(u, x);

up = f(u, x);

u = up;

return y;

```

A local version of state variables is used so as to not depend on the order of computations.

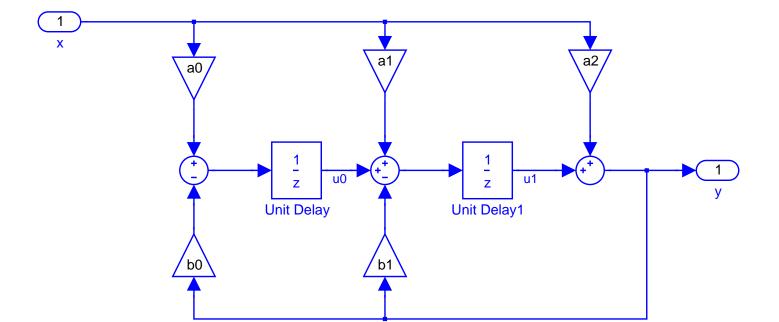

# Example \_

$$U_0(z) = z^{-1}(a_0 X(z) - b_0 Y(z))$$

$$U_1(z) = z^{-1}(a_1 X(z) - b_1 Y(z) + U_0(z))$$

$$Y(z) = a_2 X(z) + U_1(z)$$

#### **From Simulink to Difference Equations** \_

$U_{0}(z) = z^{-1}(a_{0}X(z) - b_{0}Y(z))$  $U_{1}(z) = z^{-1}(a_{1}X(z) - b_{1}Y(z) + U_{0}(z))$  $U_{0}(n+1) = a_{0}X(n) - b_{0}Y(n)$  $U_{1}(n+1) = a_{1}X(n) - b_{1}Y(n) + U_{0}(n)$  $Y(z) = a_2 X(z) + U_1(z)$   $Y(n) = a_2 X(n) + U_1(n)$

#### **From Difference Equations to Programs**

$Y(n) = a_2 X(n) + U_1(n)$   $U_0(n+1) = a_0 X(n) - b_0 Y(n)$  $U_1(n+1) = a_1 X(n) - b_1 Y(n) + U_0(n)$

```

class second_order {

private :

double a0, a1, a2, b0, b1;

double u0, u1 ;

public :

second_order(double u0, u1)

{....}

double step(double x) {

...

return y;

}

```

### **Building the step function**

$$U_0(n+1) = a_0 X(n) - b_0 Y(n)$$

$$U_1(n+1) = a_1 X(n) - b_1 Y(n) + U_0(n)$$

$$Y(n) = a_2 X(n) + U_1(n)$$

double step(double x) {

double y, up0, up1;

y = a2\*x + u1 ;

up0 = a0\*x - b0\*y ;

up1 = a1\*x - b1\*y + u0;

u0 = up0;

u1 = up1;

return y;

}

# Optimisations \_\_\_\_\_

Many optimisations are possible, due to the equational semantics of block-diagrams

- elimination of unused buffers

- eliminationg buffers by reordering computations

- mofify the original system by  $z^{-1}$  comutation

## **Unused Buffers**

```

double step(double x) {

double y, up0, up1;

y = a2 * x + u1;

up0 = a0 * x - b0 * y;

up1 = a1 * x - b1 * y + u0;

u0 = up0;

u1 = up1;

return y;

}

```

ul is not used since upl is computed

double step(double x) {

double y, up0;

y = a2\*x + u1 ;

up0 = a0\*x - b0\*y ;

u1 = a1\*x - b1\*y + u0;

u0 = up0;

return y;

}

# **Reordering Computations** \_

double step(double x) {

double y, up0;

y = a2\*x + u1;

up0 = a0\*x - b0\*y;

u1 = a1\*x - b1\*y + u0;

u0 = up0;

return y;

}

double step(double x) {

double step(double x) {

double y;

y = a2\*x + u1;

u1 = a1\*x - b1\*y + u0;

u0 = a0\*x - b1\*y + u0;

u0 = a0\*x - b0\*y;

return y;

}

ul depends on ul but not the converse. We can compute ul first.

## **Commutating Delays** \_

This is due to the property:

if f a static function (not encompassing z operators), then

$$zf(x,y) = f(zx,zy)$$

Note that *f* can be non-linear, boolean,... Known as "Leiserson & Saxe retiming" Used in hardware generation, pipelining,... Is this obvious ???

# Optimisations \_\_\_\_\_

Many possibilities

But the problem of buffer optimisation is a "hard problem"

Heuristics are required and obtaining "good code" is not obvious

Yet preferable to human coding

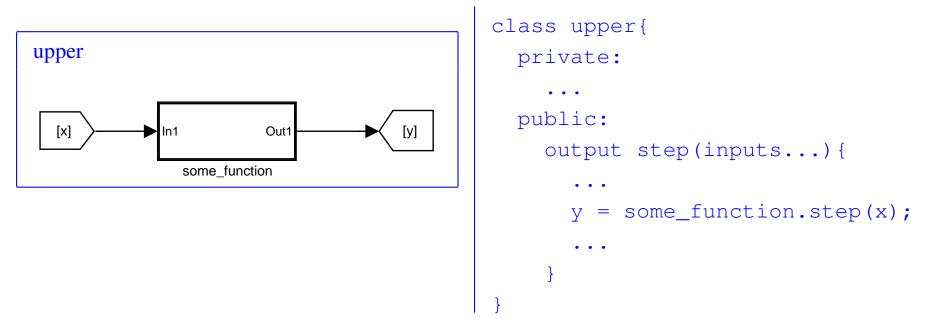

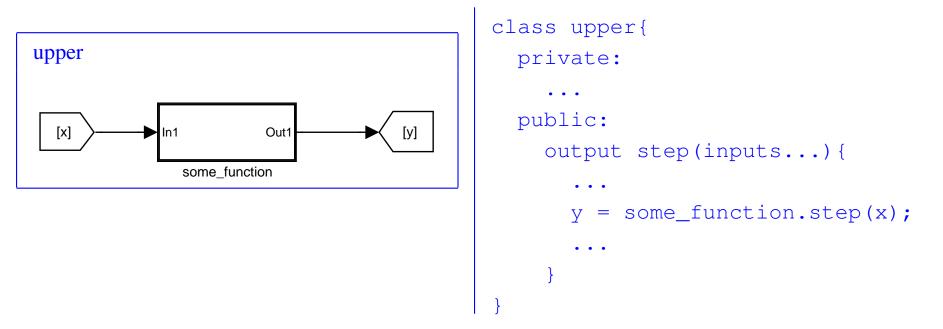

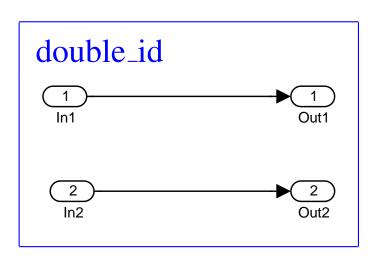

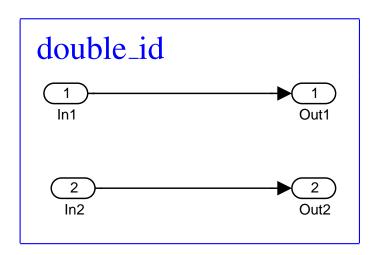

## Subsystems

Code generation is modular

## Subsystems

Code generation is modular

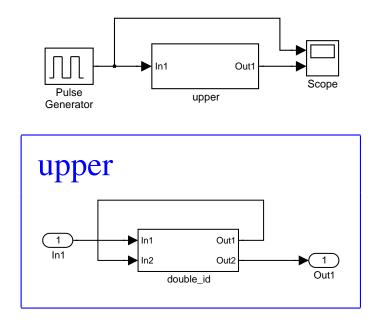

But for false causality loops!

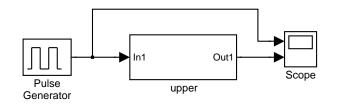

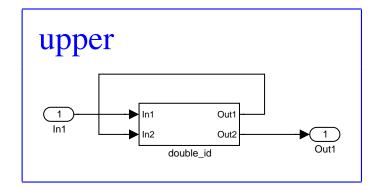

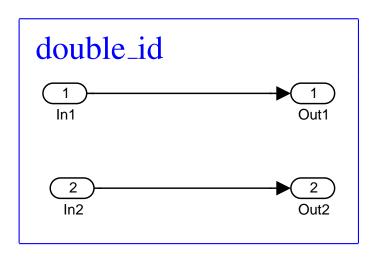

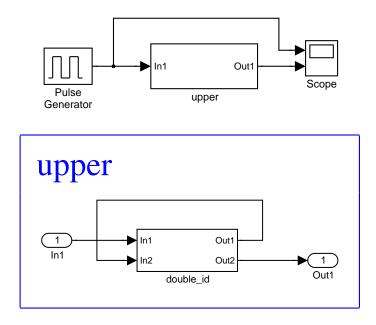

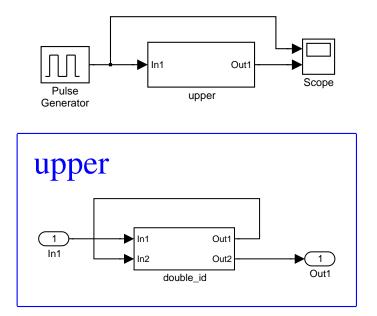

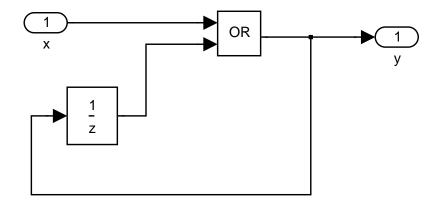

## **False Causality Loops** \_

Is this a correct model ? What is the result ?

## **False Causality Loops**

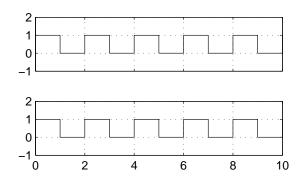

Time offset: 0

There is no causality loop But modular code generation is not possible

## **False Causality Loops**

Time offset: 0

There is no causality loop But modular code generation is not possible However code can be generated by inlining

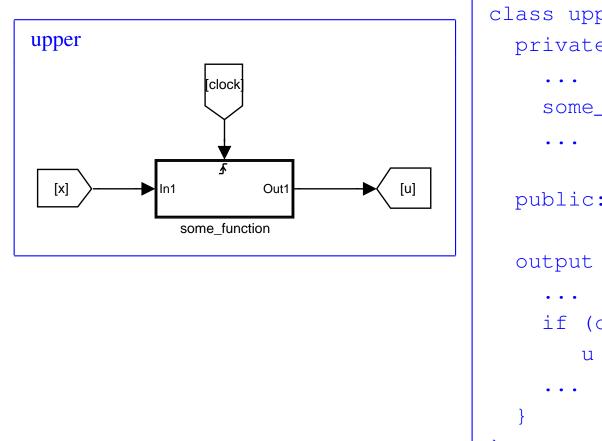

## **False Causality Loops**

#### Inlining

```

class upper{

```

public:

```

upper(){}

```

```

a_type step(a_type In1) {

```

```

a_type double_id_In1 = In1;

```

```

a_type double_id_Out1 = double_id_In1;

```

```

a_type double_id_In2 = double_id_Out1;

```

```

a_type double_id_Out2 = double_id_In2;

```

```

a_type Out1 = double_id_Out2;

```

```

return Out1;

```

## **Inlining vs Modularity** \_\_\_\_\_

Inlining allow generating code for more models

Yet modular code generation is often preferred:

• Better readability

• Easier testing

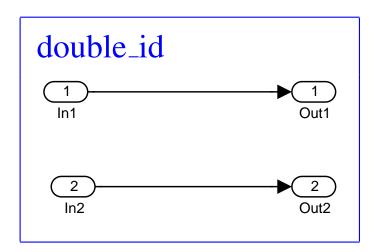

# **Triggered Subsystems**

class upper{ private: some\_type u=0; public: output step(inputs...) { if (clock) u = some\_function.step(x);

The outputs of triggered subsystems are *state variables* that have to be initialised properly.

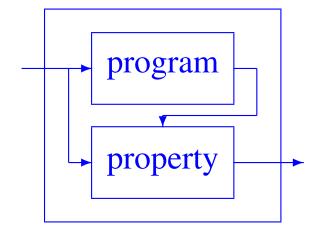

## **Code Generation for Verification** \_

Verification of Simulink/Stateflow through SCADE

Uses the translation to Lustre

• Through the Prover Plugin:

Translation to TECLA the internal language of the Prover Engine Then proof by induction using the Prover SAT - solver.

#### • using Lustre tools

for instance, enumerative model-checking through autmata code generation.

## Automaton Code Generation

#### A boolean Lustre program:

- U(n+1) = F(U(n), X(n)): State

- Y(n) = G(U(n), X(n)): Output

- U(0) : initial state

Enumerate all the reachable states and for each reachable state and possible input value, the corresponding output value.

# **Application to code generation**

Build the "verification program":

If the program is purely boolean and satisfies the property, the code generation into automaton should never output the value "false"

# Example

#### Does this program:

#### satisfies this property

#### **Translation to Lustre**

node once(x: bool) returns (y: bool); let y = x or (false -> pre y); tel

#### **Translation to Lustre**

## Verification \_\_\_\_

We build the verification node

```

node verif(x: bool) returns (prop : bool);

var y: bool;

```

```

let prop = monitor(y);

y = once (x);

```

tel

and we generate the automaton

## Result

```

switch(ctx->current_state) {

case 0:

ctx \rightarrow V2 = true;

verif_0_prop(ctx->client_data, ctx->_V2);

if(ctx->_V1){

ctx->current_state = 1; break;

} else {

ctx->current state = 2; break;

}

case 1:

ctx \rightarrow V2 = true;

verif_0_prop(ctx->client_data, ctx->_V2);

ctx->current_state = 3; break;

case 2:

ctx \rightarrow V2 = true;

verif_0_prop(ctx->client_data, ctx->_V2);

if(ctx->_V1){

ctx->current_state = 1; break;

} else {

ctx->current_state = 2; break;

}

case 3:

ctx \rightarrow V2 = true;

verif_0_prop(ctx->client_data, ctx->_V2);

ctx->current_state = 3; break;

```

plan .

## **Conclusions on Single-Thread Code Generation** \_\_\_\_

It allows generating code for any discrete-time model that can be simulated.

Allows many optimisations

The need for Real-Time Operating System is minimised

Provides in general robust and efficient code