IST-004527 ARTIST2 Network of Excellence on Embedded Systems Design

Activity Progress Report for Year 3

JPRA-NoE Integration / JPASE Dissemination and Industrial Liaison ARTIST2 Workshop on Integrated Modular Avionics, PARADES, Rome, November 12-13, 2007

Cluster Real-Time Components

Activity Leader: Albert Benveniste (INRIA) http://www.irisa.fr/distribcom/benveniste/

Today, the exponentially increasing diversity of airborne systems results in an ever increasing number of computers and controllers for system management, monitoring, and control. The development of specific ad-hoc solutions causes increases in costs, which in turn impacts purchase prices and operational costs. To overcome this, standardization principles and reuse of function units are now considered, via Integrated Modular Avionics. Integrated Modular Avionics (IMA) has set the principles of standardized components and interfaces of hardware and software in aircraft. These principles have been applied for the first time in the development of the Airbus A380. Further developing IMA raises a number of issues that require fundamental research efforts, in tight coordination with engineering needs.

ARTIST2, the European Network of Excellence on embedded systems has organized, as part of its activity on "scientific challenges in specific industrial sectors", a two-day workshop dedicated to Systems, Software, and Architecture, aspects of IMA.

The workshop analyzed:

- the issues and difficulties encountered by aircraft manufacturers and their suppliers,

- the specific research problems that result from the above issues, and,

- the recent advances in research that may contribute to overcoming the above difficulties.

| Jean-Bernard Itier, Airbus: the AIRBUS approach to open IMA; Technology, Method and Future needs          |    |

|-----------------------------------------------------------------------------------------------------------|----|

| IMA and its background                                                                                    | 6  |

| What is A380 IMA?                                                                                         | 9  |

| AFDX 11                                                                                                   |    |

| Impact of IMA                                                                                             | 13 |

| ARINC 643 OS and API                                                                                      | 14 |

| Paritioning                                                                                               | 15 |

| IMA induces new roles                                                                                     | 17 |

| Integration                                                                                               | 17 |

| The future of IMA                                                                                         | 17 |

| Discussion                                                                                                | 19 |

| Thierry Cornilleau, Dassault-Aviation: Lessons learned by Dassault-Aviation from r civil IMA applications | -  |

| MDPU –IMA in military aircrafts                                                                           | 19 |

| EASY – IMA in Falcon business jets                                                                        | 20 |

| Key points                                                                                                | 20 |

| Industrial work share                                                                                     | 20 |

| Specifications                                                                                            | 21 |

| Application development and integration                                                                   | 21 |

| Next challenges                                                                                           | 21 |

| Conclusion                                                                                                | 21 |

| Discussion                                                                                                | 22 |

| Peter Feiler, SAE AADL Committee: IMA: The Good, The Bad, and The Ugly                                    | 22 |

| The good                                                                                                  | 23 |

| The bad                                                                                                   | 24 |

| Partition assumptions                                                                                     | 25 |

| The ugly                                                                                                  | 27 |

| Impact of latency jitter                                                                                  | 27 |

| Conclusion                                                                                                | 29 |

| Discussion                                                                                                | 29 |

| Paul Caspi, Verimag: Some issues about IMA in safety critical applications                                |    |

| Where does this viewpoint come from?                                                                      | 30 |

| IST-004527 AF   | RTIST2 NoE                                                      | Year 3                  | 7 N 2                               |

|-----------------|-----------------------------------------------------------------|-------------------------|-------------------------------------|

|                 | <rtc></rtc>                                                     | <ima workshop=""></ima> | Information Society<br>Technologies |

| Activity:       | <dissemination and="" industrial="" liaison=""></dissemination> |                         | Technologies                        |

| Why simple f    | federated architectures were so successfu                       | ll?                     | 30                                  |

| Two acciden     | tss that could have been avoided by simpl                       | le federated architectu | ires 31                             |

| ARIANE V        | /                                                               |                         |                                     |

| Priority inv    | version in the Mars Pathfinder                                  |                         |                                     |

| What kind of    | guarantee should we require for IMA?                            |                         | 31                                  |

| Discussion      |                                                                 |                         | 31                                  |

| •               | SRI: Compositional Assurance for IMA<br>nn Rushby]              |                         |                                     |

|                 | Airbus Germany: Embedded System De                              | •                       |                                     |

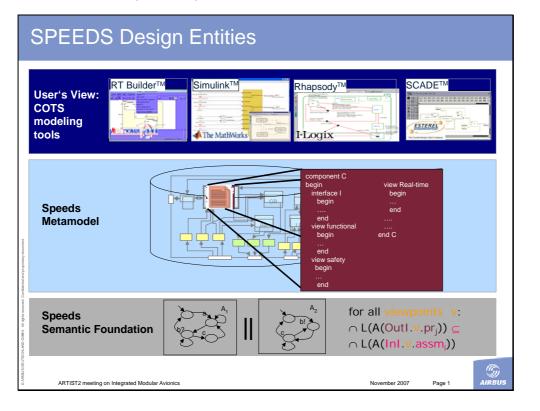

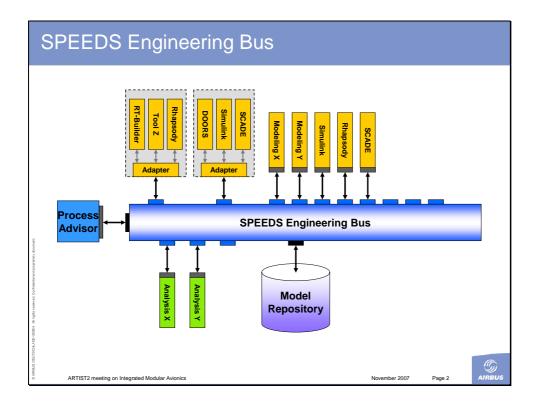

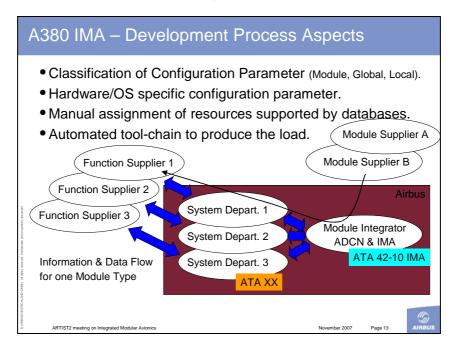

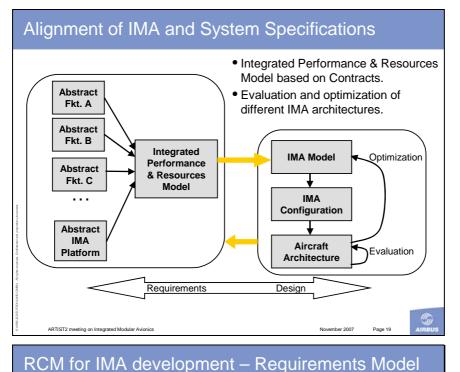

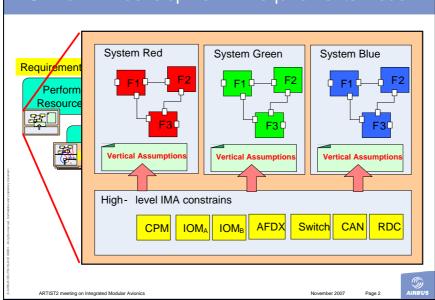

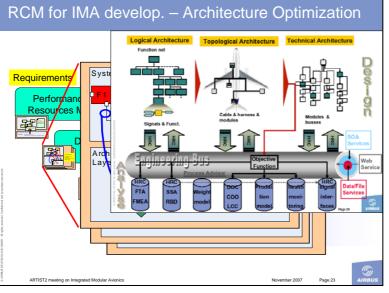

| The SPEEDS      | S project                                                       |                         | 44                                  |

| Distributed n   | etworked computing platform                                     |                         | 45                                  |

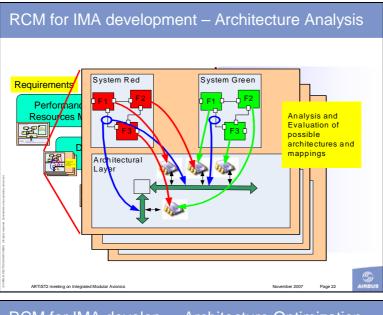

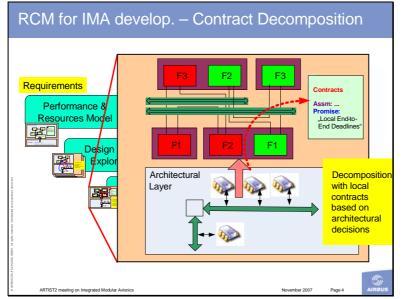

| Using SPEE      | DS for IMA development                                          |                         | 46                                  |

| Discussion      |                                                                 |                         | 48                                  |

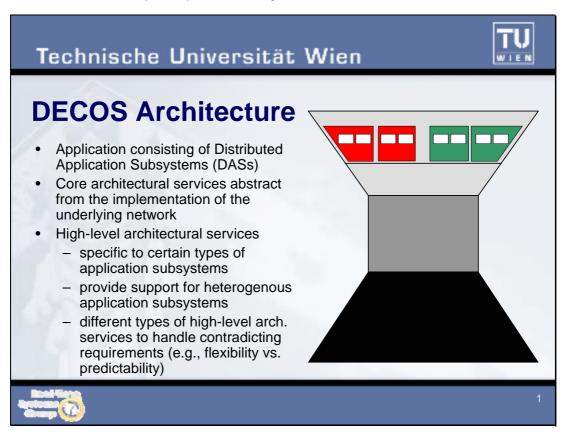

|                 | naisser, TU Vienna: Supporting Heterog                          |                         |                                     |

| Federated an    | nd integrated architectures                                     |                         | 48                                  |

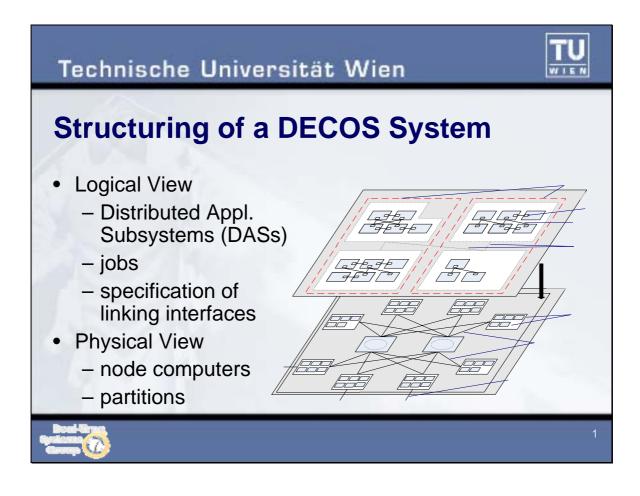

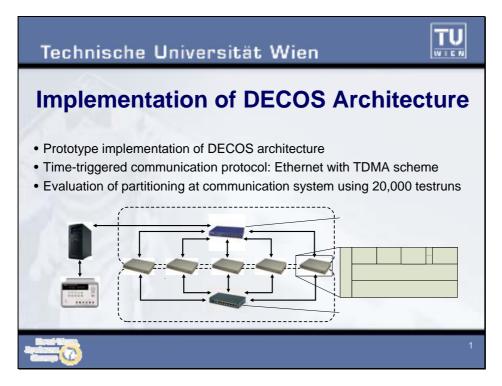

| DECOS arch      | nitecture                                                       |                         | 49                                  |

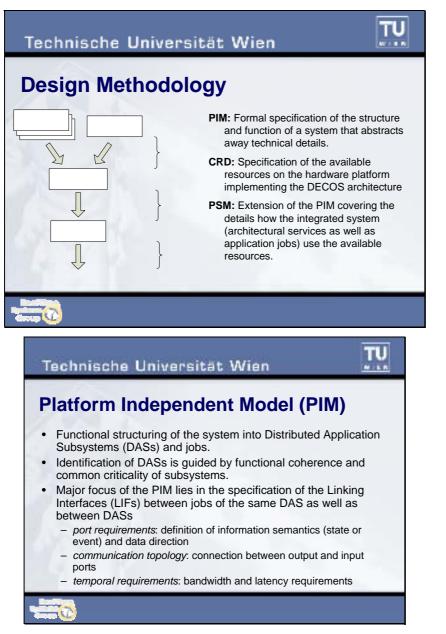

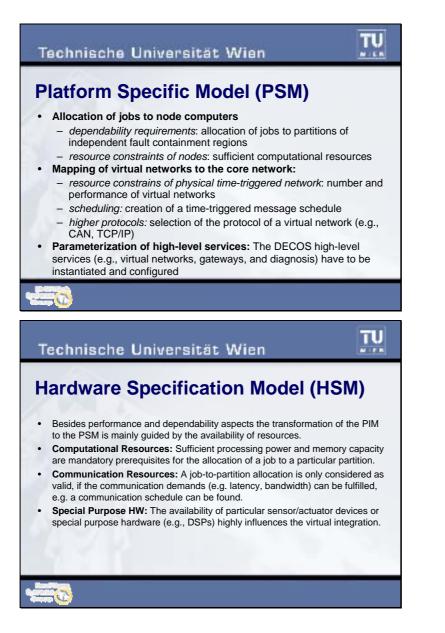

| Model based     | development process                                             |                         | 51                                  |

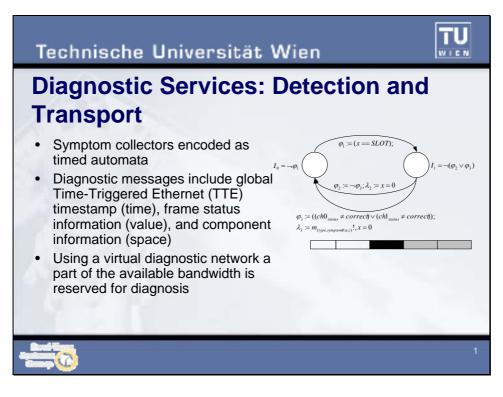

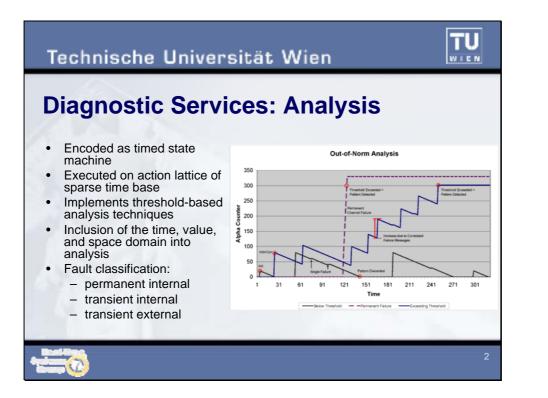

| Architeectura   | al services                                                     |                         | 52                                  |

| Implementat     | ion and sresults                                                |                         | 53                                  |

| Discussion      |                                                                 |                         | 55                                  |

| Kevin Driscoll  | Honeywell: Honeywell requirements for IM                        | 14                      | 55                                  |

|                 | s Integrated architecture                                       |                         | 55                                  |

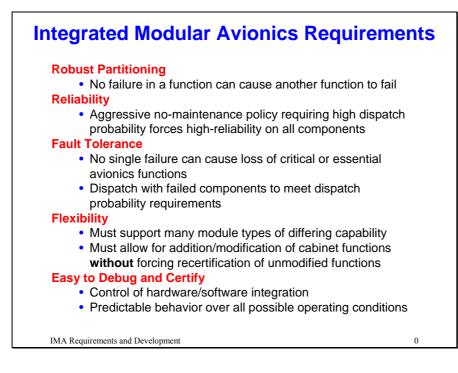

| IMA requiren    | ·                                                               |                         | 57                                  |

| •               | oning requirements                                              |                         |                                     |

| -               | of IMA requirements                                             |                         |                                     |

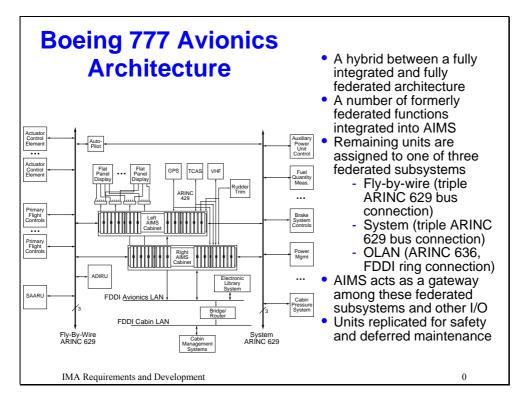

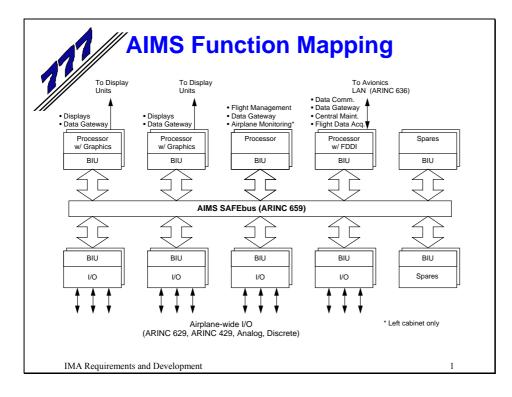

| 2               | avionics architecture: a 1 <sup>st</sup> step in IMA            |                         | 59                                  |

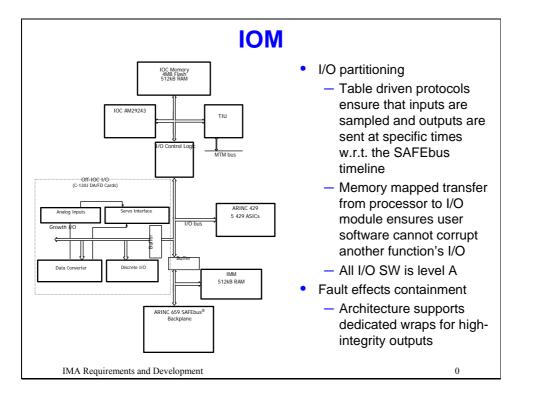

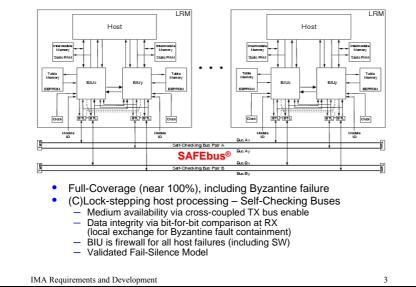

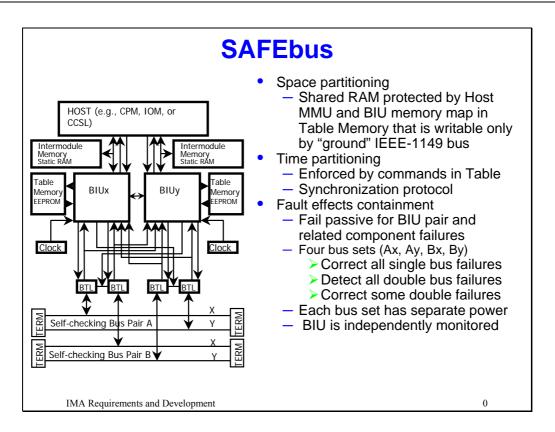

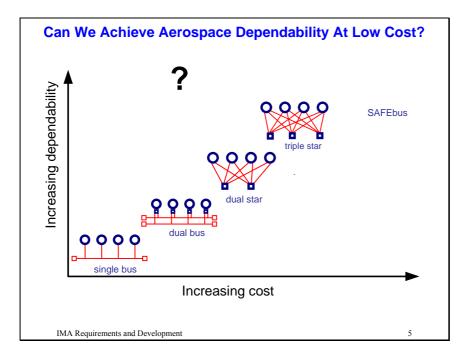

| -               | nd bus: SAFEbus                                                 |                         | 61                                  |

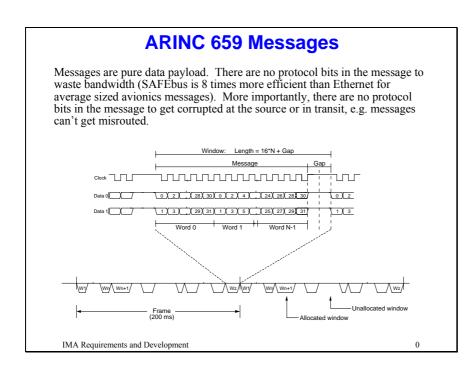

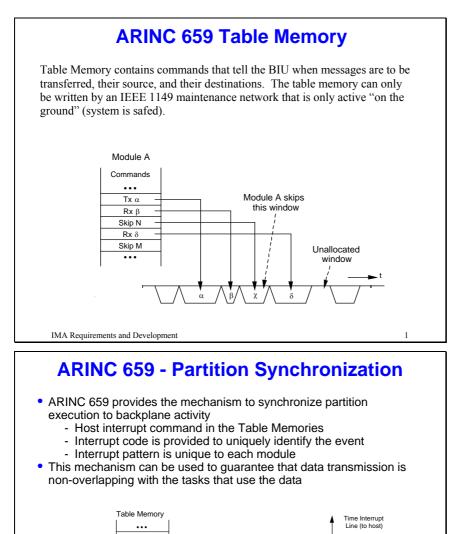

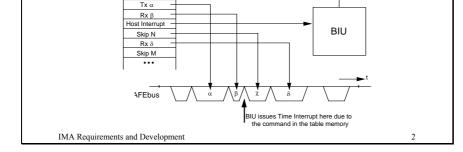

|                 | 9                                                               |                         |                                     |

|                 | roject                                                          |                         |                                     |

| ,<br>Discussion | -                                                               |                         | 67                                  |

|                 |                                                                 |                         |                                     |

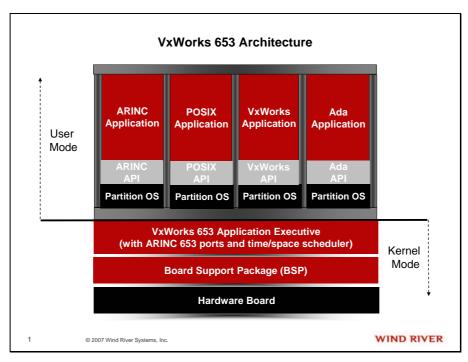

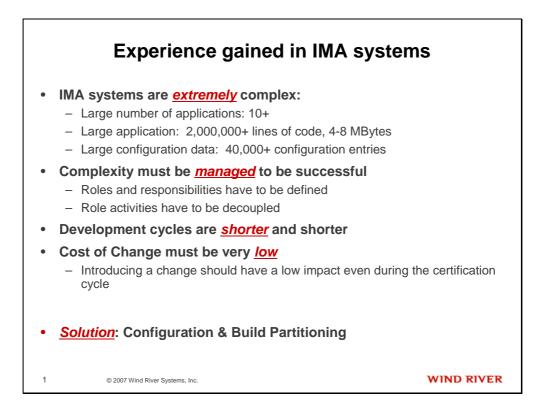

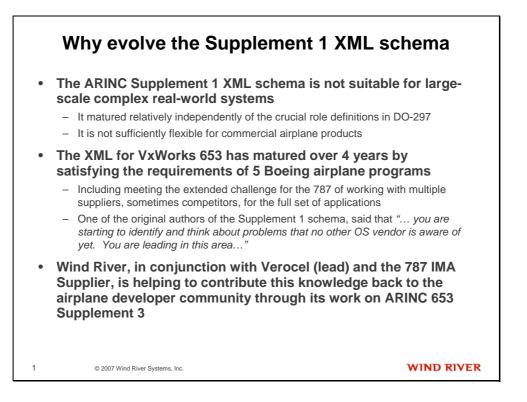

|                 | /ind River: The evolving ARINC 653 stand                        | ard and its application | to IMA67                            |

| ARINC 653 s     | specification                                                   |                         | 67                                  |

| DTCA DO 2027 / EUDOCAE ED 404 - Ouidenes and cartification considerations                                                                              | ~~~   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

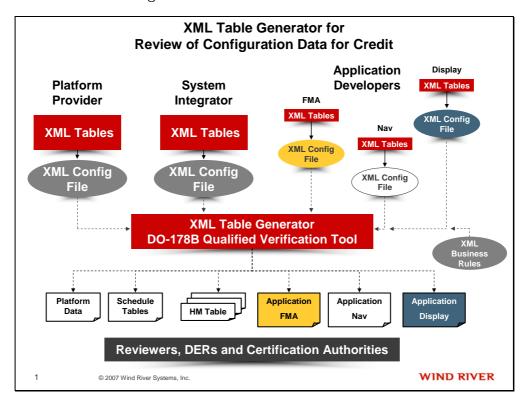

| RTCA DO 297 / EUROCAE ED 124 – Guidance and certification considerations                                                                               | 69    |

| XML based configuration                                                                                                                                | 71    |

| Discussion                                                                                                                                             | 72    |

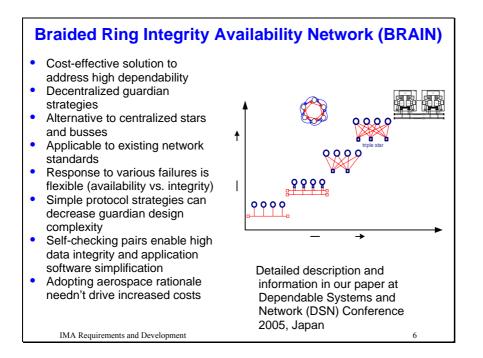

| Chris J. Walter, WW Technology Group: Dependable solutions for IMA                                                                                     | 73    |

| Lessons learned                                                                                                                                        | 73    |

| Strategy                                                                                                                                               | 74    |

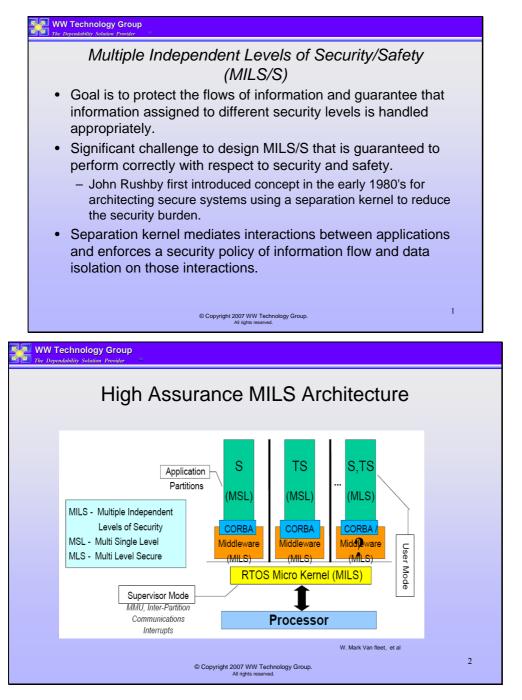

| MILS: Multiple Independent Levels of Security/Safety                                                                                                   | 75    |

| Design for certification                                                                                                                               | 76    |

| Discussion                                                                                                                                             | 76    |

| Panel Session on expectations from research for IMA                                                                                                    | 76    |

| Benefits of moving to IMA                                                                                                                              | 76    |

| Enabling changes in the organization of the sector                                                                                                     | 76    |

| Avoid the explosion of computing and networking resources                                                                                              |       |

| Allow more flexibility while splitting into sub-systems                                                                                                |       |

| Risks in moving to IMA                                                                                                                                 | 77    |

| Can we have IMA while keeping advantages of federated architectures in terms of saf                                                                    |       |

| 77                                                                                                                                                     |       |

| Risk coming from non predictability of supporting architecture                                                                                         | 78    |

| The automotive/avionics market is not going to drive the chip manufacturing market                                                                     |       |

| Complexity of processors                                                                                                                               | 79    |

| Complexity of problems                                                                                                                                 | 79    |

| Validating OS? What does it mean to validate OS w.r.t. properties offered for partitions                                                               | s? 79 |

| Partitioning risks                                                                                                                                     | 79    |

| Risks of putting all your eggs in one basket                                                                                                           | 80    |

| Do we have a sufficient toolset to support IMA?                                                                                                        | 80    |

| What about power management in IMA?                                                                                                                    | 80    |

| Increase in the risk of common mode design as a result of reducing the number of par                                                                   | ts 80 |

| What about IMA in handling legacy code or designs?                                                                                                     | 81    |

| Should safety of IMA entirely rely on infrastructure?                                                                                                  | 81    |

| Radiation tolerance                                                                                                                                    | 81    |

| Gap between higher level design (programming guidelines) and lower level architectur<br>aspects?                                                       |       |

| How architects and SW engineers do communicate with control engineers about the features of their architectures and requirements for the architecture? | 81    |

| Application reuse is a major issue                                                                                                                     | 81    |

| Research issues                                                                                                                                        | 81    |

| Mitigating with the complexity of processors and architectures                                                   | .81  |

|------------------------------------------------------------------------------------------------------------------|------|

| Dependability and related risks arising from IMA                                                                 | . 82 |

| Validating OS? What does it mean to validate OS w.r.t. requirements for IMA?                                     | . 82 |

| Do we have a sufficient toolset to support IMA?                                                                  | .83  |

| What about power management in IMA?                                                                              | .83  |

| How architects and SW engineers do communicate with control engineers about the features of their architectures? | .84  |

| Applicatiion prediction and reusability                                                                          | .84  |

# Jean-Bernard Itier, Airbus: <u>the AIRBUS approach to open</u> <u>IMA; Technology, Methods, Process and Future needs</u>

JB Itier is Strategic technical Project Manager for Information Management for Avionics Platform and responsible for all R&T platforms subjects participating to IMA.

# IMA and its background

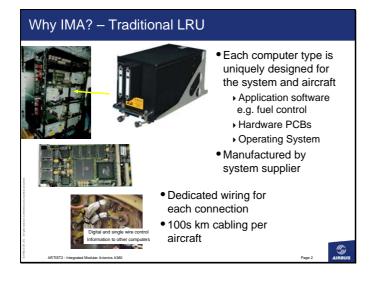

Since A300 there is an increasing number for software controller systems, for performance, safety, improved maintenance, passenger comfort. This will increase.

Consequences so far:

- every system = 1 or more computer / controllers

- every aircraft = new computers

- every computer = lots of specific equipment

If you look at the communications on past aircraft it is in most cases point to point even where digital data buses were used they were in the main based on ARINC 429 a standard where every sender of information has its own bus and in most cases because of data needs several buses

In the past we have one or more computers per aircraft system,

typically uniquely designed and manufactured for that system on that aircraft e.g. for fuel management I.e. you could not hold a fuel computer that could be used on an A320 and A330.

Since A300 the trend was to increase on board SW & HW. However this situation cannot continuous & it was necessary to stabilize volume, weigh & costs for on board electronics and to reduce it in the next generation of A/C.

The response: IMA

- IMA

- o concept

- o no specific technology or components

- Integration

- o multiple applications on same computer

- o data communications with multiplexed network

Several approaches were proposed by the different suppliers:

<RTC>

Cluster:

Activity:

What is IMA? Cabinet of modules • Functionality split between modules: • Power Supply Modules, Gateways, Processing, IO • Inter module communications backplane • ARINC 653 Operating System Originally ARINC 629 Single supplier .... for everything • Boeing 777 9 ARTIST2 - Ir ics A380 What is IMA? • Card File • Semi open architecture - third party hardware • Processing, IO and gateway cards Proprietary DEOS Operating System • Proprietary backplane • Business and Regional Jets • Embraer, Raytheon, Dornier 9

<Dissemination and Industrial Liaison>

Independent modules as LRU, provides processing, IO and PSU in one package

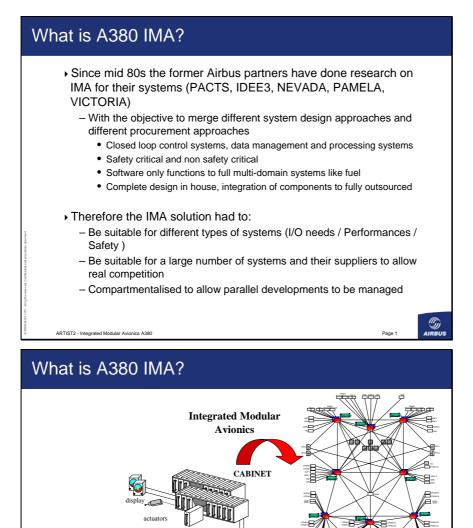

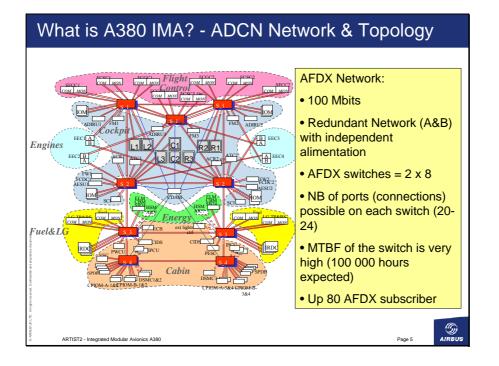

# What is A380 IMA?

« Federated architectures

LRU « black

ARTIST2 - Ir

nsors

s A380

A629

**CONCEPTS & TECHNOLOGIES EVOLUTIONS**

Multi-transmitter bus network

MODULE

AFDX NETWORK

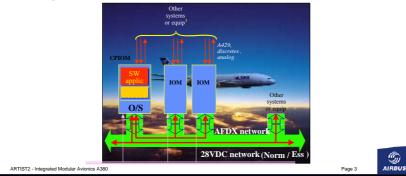

# What is A380 IMA? - Airbus Concept

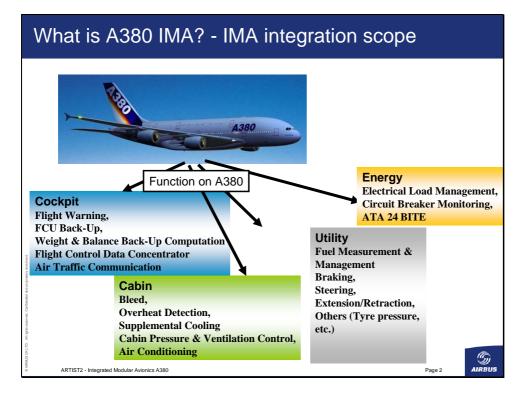

- IMA shared resources are:

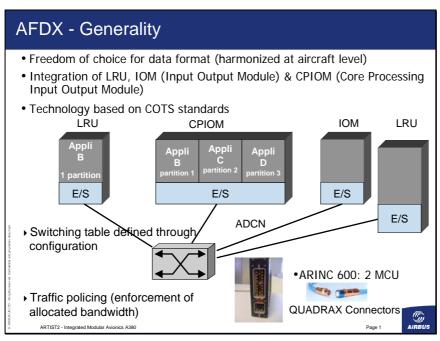

- the avionics communications network: the solution selected is AFDX (Avionics Full Duplex Ethernet), fully compatible with Ethernet network of Open World and based on common switch modules

- Modules, i.e. Core Processing & Input / Output Modules or CPIOM, Input/ Output Modules or IOM, ....) for hosting of several applications and signal acquisition/transmission

# What is A380 IMA? Airbus Concept

- The AIRBUS IMA concept is based on "shared Modules". A modulefocused approached has been preferred compared with the previous concept of "Cabinet". Its key features are:

- ARINC 600 IMA Module packaging connected to AFDX network

- Robust partitioning in computing resource & communications

- Determinism of application execution & data exchanges

- Standardised Application Programming Interface (API) to avoid obsolescence impacts on applications

- · Conventional equipment's mixable

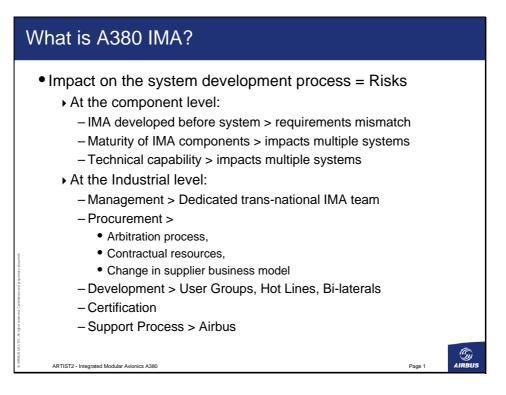

- Resource sharing has a direct impact on the way to design and implement systems since it creates new dependencies between them, both from a technical and a process point of view.

- This concept has been selected as the baseline for systems design on Cockpit, Utility, Energy and Cabin domains and extended globally on all the domains.

| ARTIST2 - Integrated Modular Avionics A380 |

|--------------------------------------------|

|--------------------------------------------|

| All |

|-----|

Page

CPIOM + IOM + network + switches, AFDX (Avionics Full Duplex Ethernet), fully compatible with Ethernet; CPIOM allow for uniform handling of all applications; no power supply modules, part of networks or CPIOM  $\rightarrow$  scalability.

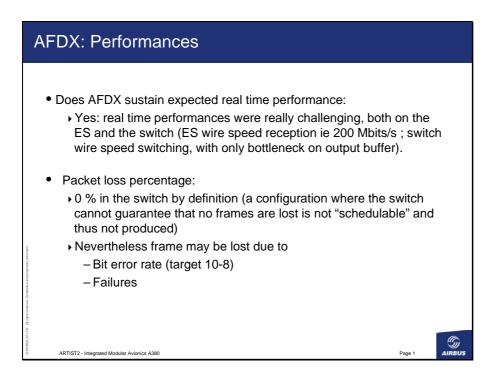

### AFDX

Year 3

AFDX technology – Addressing : MAC, IP, UDP S E/S 2 Avionics communications are based on multicast: • one transmitter • one or several receivers Asynchrony individual clocks • NO reconfiguration capability in the AFDX network Alt = 10 000 ft UDP SRC / UDP DEST IP SRC / IP DEST MAC SRC / MAC DEST G) ARTIST2 - Integrated Modular Avionics A380

The aim is to enforce determinism; no reconfiguration capability in ADFX network; multicast; asynchrony of individual clocks for the different sub-system. Systems are essentially asynchronous at entire aircraft level.

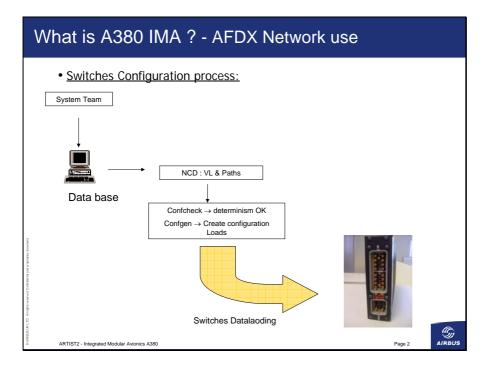

Switch configuration process: the important point is that this configuration is performed at design time; flexibility supports multiple configurations for the aircraft.

Year 3

<IMA Workshop>

# Impact of IMA

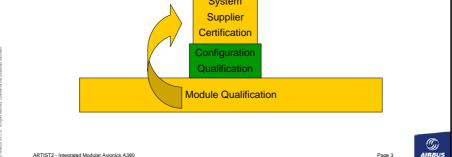

Altogether big change in the supplier business model; some suppliers provide only software; the way to pay them is different. New qualification approach was necessary to maximize IMA concept benefit & reuse HW qualification (Incremental qualification approach). A review of the many solutions proposed by the suppliers is performed before choosing the subsystems and components. Joint launch team to define the avionics solution.

Some systems are not in, mainly for performance issues; also it was the 1<sup>st</sup> time and the number of systems based on this technology had to be minimized.

Modules have been developed at:

- Airbus (EYY)

- Thales

- Diehl

### ARINC 643 OS and API

Suppliers had to re-develop their applications in this way. Push independence between HW and SW; application SW independent from HW:

- No direct access to I/O

- Internal process control services

- Health Monitoring services

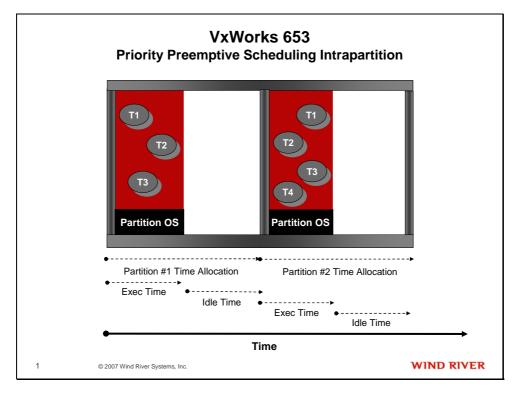

Multi-threading is used but (probably) not preemption. Partitions support segmentation; multi-threading is used within the partition. Scheduling between partitions is static.

This allows fighting obsolescence of HW components. Sometimes these components will be upgraded. SW will be kept even if HW is upgraded.

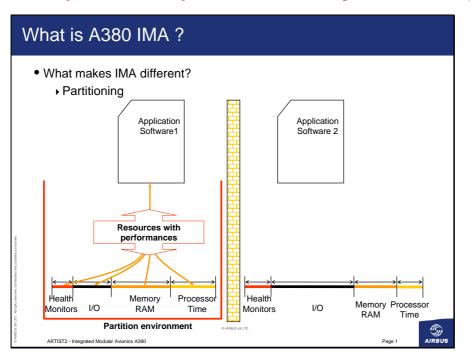

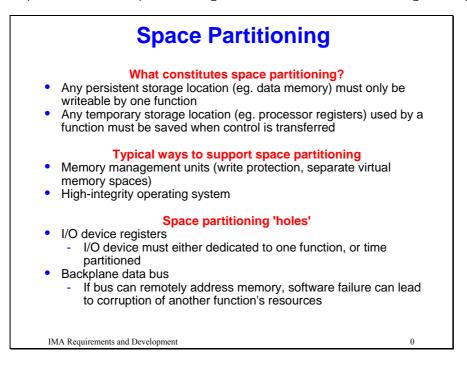

## Paritioning

Functions can be allocated to one or more partitions.

Each system must be able to be validated in isolation on the module. Faults must be contained. The performance of each system must be *unaffected* by any other

*Q: is "unaffected" really possible? Do you mean that it continue working, but may affect indirectly other functions through the controlled plant.*

Regarding timing: time slots are allocated to partitions. Memory is protected via MMU to ensure that it remains safe.

Segregation of I/O; the different modules read the current value of exchanged data at their own pace. All exchanges are through the network using the virtual links.

What partition enables is shown below; incremental qualification is important and is enabled by partitioning.

ARTIST2 - Integrated Modular Avionics A380

Year 3

<IMA Workshop>

Page 2

# What is A380 IMA ? Partitioning enables: System independence - Systems of different DAL(A,B,C) level can be developed at their DAL level - Systems can be integrated and tested to separately Incremental Qualification - Modifications to one application have no effect on other applications · Qualification activities following a modification are limited • Configuration Parameters Partitioning and Configuration IMA must be configurable - Resources - Time, Memory and I/O - Implemented with Configuration Tables - loadable Two groups of tables: - Tables managed by Airbus - have a global effect - Tables managed by the Function Supplier - only have a local partition 9 ARTIST2 - Integrated Modular Avionics A380 Page 1 What is A380 IMA? Qualification of the module within a usage domain represented by the set of configuration parameter ranges Usage Domain - Represents guarantees on · Functionality • Performance - e.g. service call times - For the range of configurations the module can be used in 9

Year 3

# What is A380 IMA ? - IMA Modules Qualification Qualification and system certification are major parts of IMA The objective of the qualification approach is to give System

- Suppliers "credit" to be used as part of their system certification Based on credit

- The function / system supplier takes "credit" from the qualification activities of Module Manager and Module Supplier

- Does not have to prove functionality, performance and behaviour of the module. System

Q: How to maintain determinism while not using inter-partition communication (which is guaranteed deterministic)? A: in fact different subsystems are designed from the beginning to tolerate asynchronous communications, thus nondeterminism in communications is no additional harm.

Room of improvement to reduce the cost of testing

#### IMA induces new roles

IMA manager, played by Airbus; includes providing configuration tables (with their qualification), controls the use of modules resources, performs confidence testing and gualification of module configuration.

### Integration

Integration tests are performed on HBOSS (Host Based OS Simulation) and then on TBOSS (Target Based OS Simulation).

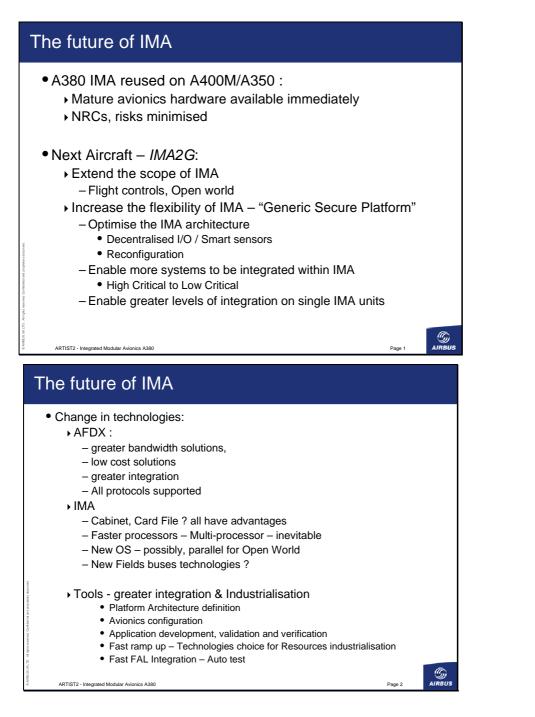

# The future of IMA

See figure below; it is considered very beneficial since allows reusing mature avionics: risks minimised.

There is a need to extend the scope of this technology, so a new generation is planed, including flight control, also functions related to open world (non safety critical, e.g., infotainment). We wish to enable more systems to be integrated within IMA (from highly critical to low critical), up to the entire system on board.

Security protection for the open part of A380 may possibly be extended to other more core systems, using same techniques. Move to decentralised architecture and smart sensors. Allow for more flexible reconfiguration, e.g., for maintenance purposes.

Enable grater level of integration on single IMA units: more applications on a single module.

Year 3

<IMA Workshop>

Needed changes of technologies, see figure above:

- AFDX: grater bandwidth, all protocols supported (including video, voice...); will be kept because of performance and wide use.

- IMA: new OS?

- New field buses technologies, including TTA. For what is TTA best suited? Studies ongoing on Flexray (today CAN is the baseline).

- Toolset: greater integration and industrialisation of the entire toolset; full system virtual validation. Need for a platform offering full auto tests.

## Discussion

Q: is it possible that the supplier has larger responsibility in how to achieve qualification of subsystems? A: the toolset should help supporting this.

Q: in what way current field bus technology is not adequate? A: For some systems like flight control, CAN is not adequate and we would like something else. Now, one additional technology is more costs. Not decided yet on this point.

Q: question on tools; how do you have a global model of your system? A: Depends on system designer, not a single method is used. Some use Simulink... Q: How do you verify AFDX interaction? AFDX is not deterministic. A: it is deterministic and verified by design using "Confcheck". This Tool verifies that the performances requested by all the Virtual link of the networks will be satisfied.

Note that the different modules are synchronous. Just their clocks are not synchronised and therefore the resulting communication is not synchronous, regardless of the particular communication mode used. In addition, Ethernet communication is used, which uses asynchronous protocol. The system is deterministic only if the speeds is fast enough. Information on this is found in ARINC documents.

Q: is this not the reason for looking for TT architectures and buses? A: if enough time available, no need for a deterministic system managed by 1 clock to achieve this.

Q: this may not survive if you increase the usage pressure, there is some clock drift, and you increase the load, you may get problems. A: if enough time is available, no need for a deterministic system managed by 1 clock to achieve this.

Q: future of reconfiguration capabilities, are you interested in this research direction? A: may be interesting but considered risky; will progress cautiously in this direction. Will depend on complexity and real A/C Benefit.

Q: what about changes in SW maintenance? A: not the right person to answer. Having a clean platform with standardised API and configuration means are important elements.

# Thierry Cornilleau, Dassault-Aviation: <u>Lessons learned by</u> <u>Dassault-Aviation from military and civil IMA applications</u>

Design division of Dassault Aviation

## MDPU –IMA in military aircrafts

Modular data processing unit, IMA in military aircraft. Started in 1998. For use in Rafale and Mirage 2000/9. Was developed with Thales. Aims at reducing cost, allow for third party developments. MDPU provides HW and SW resources that are generic.

MDPU reuses ASAAC concepts. This started in the US in 1980's, for Apache helicopter. Phase II of ASAAC started 1998. MDPU is based on available techno in 1999, e.g., SCI was selected for communications.

MDPU restricted to non critical functions or critical interruptible functions, not flight control.

Year 3

MDPU generic HW architecture: it is a cabinet with modules inside and power supply, based on SCI backplane topology for communications. Air cooling is used. For the SW architecture, POSIX is used as an OS. There is an API to be interfaced with applications. There are also system applications such as configuration and synchronization (a global clock is used). Aim is to decouple application from HW architecture.

Inside an MDPU module, there is also a generic architecture with SCI backplane and an interface to the avionics global bus. This has a cost but allows incremental upgrades of this architecture. Module packaging is performed in a way that makes them easily replaceable by pilots or technicians not experts of these machines.

MDPU benefits:

- reduced weight, volume, power consumption, due to the sharing by several application of a same MDPU

- 2<sup>nd</sup> level of maintenance removed, thanks to LRM concept (Line replaceable module)

- room for upgrades

- open architecture and standardised interfaces, allows coping with obsolescence

- same resources can be used for different variants of aircrafts

## EASY – IMA in Falcon business jets

Based on an avionics from Honeywell Primus Epic. Architecture built with Modular Avionics Units (MAU). Cabinet with up to 20 modules in it and power supply. Covered: auto-pilot, flight management, and more. The processors in modules include Pentium.

OS is common to several modules, uses a Honeywell OS close to ARINC 653. Core functions on top of the OS: fault history, file system, configuration, inter-module communications, and built-in test. Communication is through the backplane to ensure deterministic latency.

Communications rely on a dedicated cPCI backplane for intra-cabinet, on a redundant serial bus between MAUs, and on Ethernet for maintenance purpose.

Technology selected in 2000, first certification in 2004.

## Key points

These key points give hints about how to handle more easily an IMA. They are not really new for a system designer but they remain true in an IMA context.

#### Industrial work share

Industrial work share evolved. Moving from federated architecture (where black-boxes were assembled) to modular architecture where diverse subsystems and components are integrated:

platform supplier

- function supplier

- application suppliers

- system integrator

All this requires clarification of roles and interfaces.

#### Specifications

A top-down approach is used, with explicit non-functional specs. Observability requirements are formulated regarding the interfaces; interfaces must be clearly exposed. There is a provision for reconfiguration capabilities at run time ("mode changes"). Define a clear policy to handle this at certification time. Early validation is important.

COTS are reused from non-aircraft markets. Mostly used in previously experimented usage domains. Otherwise develop own solution.

#### Application development and integration

HW/SW decoupling is important. Offer a platform with deterministic behavior. Ensure that applications behave the same regardless from their localization.

Spatial and temporal partitioning is used. Platform is integrated first, before integrating the applications.

Try to predict early the needed size for the HW platform.

### Next challenges

Increase of 3<sup>rd</sup> party development:

- Open interfaces & standards

- Work based on tool supported contracts; plug & play

- Data security concepts inside IMA: MILS (Multiple Independent Levels of Security)

- Application reuse, particularly when a new supplier is brought into the process

- Enhance complexity control: configuration capabilities (cold and warm reconfigurations of an IMA subject to certification). Early verification & validation, virtual design space exploration, predictable sizing.

- Support incremental certification.

- Assessment of new technologies:

- o multi-core

- o IT technologies in embedded world,

- asynchronous networks for deterministic applications (TT buses are costly)

- commonalities between the different transport industries (automotive, train, aerospace); avoid reinventing the wheel

### Conclusion

Successful concept used in civil and military projects. Open architectures allow manufacturers to subcontracts suppliers while keeping control of the system.

## Discussion

Q: have you tools to specify blueprints? A: tables for configuration are mostly made by hand. AADL is a 1<sup>st</sup> progress.

Q: are you going to use CORBA or other type of contract. A: interested in component concept, with notion of service required and offered.

Q: How to face dynamically reconfigurable systems? A: for the moment, lots of tests at integration; but reconfiguration is interesting since you use fewer resources. There is in-flight reconfiguration after fault.

Q: we have lots of experience in CORBA component models using CCM. A: If applied, CCM will only be used with static configuration.

Q: what are the standards of interest? A: ARINC 653 is the basis. It is well designed. This gives the plug but not necessarily the play.

Q: using contracts in standards: how? A: this is an idea and need to work on this. AADL would be the good basis to standardize contracts, both functional and nonfunctional.

Q: how to make computing time estimations? A: well, we expect technologies from the university to get as soon as possible in design process WCET and CPU loads.

*Q:* (Absint) there are solutions for WCET estimations with cache. You don't have to wait for solutions from the university... (Note: This works only if the application binary is available, but very often estimations are required more early in the development process)

Q: how do you manage coordination between partitions and I/O. A: For high performance, we have asynchronous mechanisms. For determinism, on civil IMA, all communications go systematically through the bus.

*Q: is the number of modules going to further increase, or reduce?* **A: modules are** *more powerful but you want more applications, but sharing applications among modules reduces the number of modules used. No idea of how the overall load will increase – depends on the aircraft.*

# Peter Feiler, SAE AADL Committee: IMA: The Good, The Bad, and The Ugly

SW engineering institute at CMU in Pittsburgh. Technical leader for AADL standard.

# The good

| Partitioned                                                                                                                                                                                 | system architecture (ARINC 653)                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                             | ponentized system                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                             | ation to common compute platform                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0                                                                                                                                                                                           | gration of embedded software systems                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                             | chitecture (ARINC 429, 629)                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                             | ally synchronous                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                             | ally asynchronous Locally Synchronous (GALS)                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| The Go                                                                                                                                                                                      | od                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| The Goo                                                                                                                                                                                     | od                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                             | od<br>ystem architecture                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Partitioned s <ul> <li>Flexit</li> </ul>                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Partitioned s<br>• Flexit<br>legac                                                                                                                                                          | ystem architecture<br>pility through configurability of componentized system & migration of                                                                                                                                                                                                                                                                                                                                                                        |

| Partitioned s<br>• Flexit<br>legac<br>• Redu                                                                                                                                                | ystem architecture<br>pility through configurability of componentized system & migration of<br>y components                                                                                                                                                                                                                                                                                                                                                        |

| Partitioned s<br>• Flexit<br>legac<br>• Redu<br>Space & time                                                                                                                                | ystem architecture<br>pility through configurability of componentized system & migration of<br>y components<br>ced cost through shared compute platform & increased utilization                                                                                                                                                                                                                                                                                    |

| Partitioned s<br>• Flexit<br>legac<br>• Redu<br>Space & time<br>• Impac                                                                                                                     | ystem architecture<br>pility through configurability of componentized system & migration of<br>y components<br>ced cost through shared compute platform & increased utilization<br>e partitioning                                                                                                                                                                                                                                                                  |

| Partitioned s<br>Flexit<br>legac<br>Redu<br>Space & time<br>Impac<br>Partit<br>Prote                                                                                                        | ystem architecture<br>pility through configurability of componentized system & migration of<br>y components<br>ced cost through shared compute platform & increased utilization<br>e partitioning<br>ct of run-away threads contained to single partition                                                                                                                                                                                                          |

| Partitioned s<br>• Flexit<br>legac<br>• Redu<br>Space & time<br>• Impac<br>• Partit<br>• Prote<br>subsy                                                                                     | ystem architecture<br>pility through configurability of componentized system & migration of<br>y components<br>ced cost through shared compute platform & increased utilization<br><b>a partitioning</b><br>ct of run-away threads contained to single partition<br>ion-specific scheduling policies facilitate integration of subsystems<br>cted address spaces provide fault isolation barrier for safety-critical                                               |

| Partitioned s<br>• Flexit<br>legac<br>• Redu<br>Space & time<br>• Impac<br>• Partit<br>• Partit<br>• Prote<br>subsy<br>nter-partition                                                       | ystem architecture<br>pility through configurability of componentized system & migration of<br>y components<br>ced cost through shared compute platform & increased utilization<br>e partitioning<br>ct of run-away threads contained to single partition<br>ion-specific scheduling policies facilitate integration of subsystems<br>cted address spaces provide fault isolation barrier for safety-critical<br>ystems                                            |

| <ul> <li>Flexit<br/>legac</li> <li>Redu</li> <li>Space &amp; time</li> <li>Impac</li> <li>Partit</li> <li>Prote<br/>subsy</li> <li>Inter-partition</li> <li>Direc</li> <li>Phase</li> </ul> | ystem architecture<br>pility through configurability of componentized system & migration of<br>y components<br>ced cost through shared compute platform & increased utilization<br><b>a partitioning</b><br>ct of run-away threads contained to single partition<br>ion-specific scheduling policies facilitate integration of subsystems<br>cted address spaces provide fault isolation barrier for safety-critical<br>vstems<br><b>a communication semantics</b> |

Spae&time partitioning is important; impact of run-away threads contained to a single partition. Partition themselves are statically scheduled; but inside partitions you can use dynamic scheduling or other policy, with preemption.

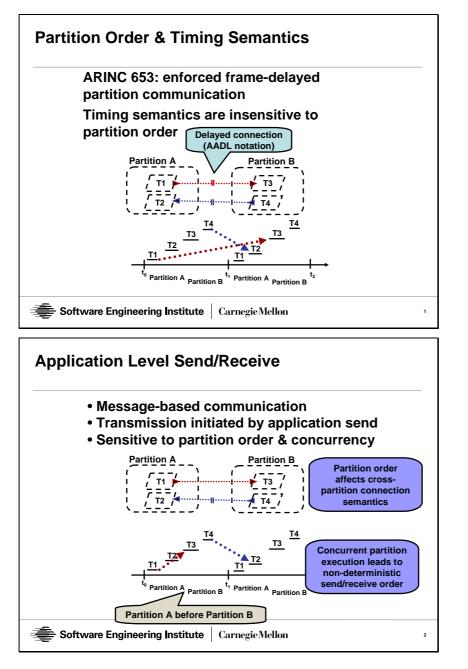

Inter-partition communication guarantees determinism despite concurrency.

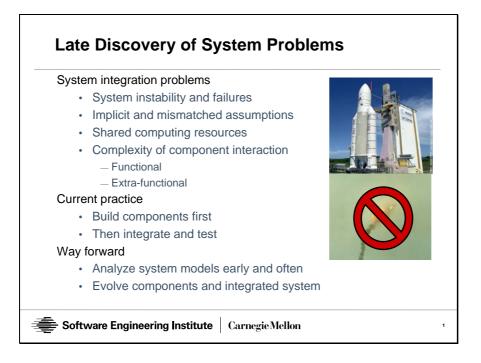

# The bad

Despite fault tolerance built into systems problems are discovered during integration and operation. Examples are System instability and failures, implicit and mismatched assumptions, complexity of component interaction (functional and non-functional).

Way forward: evolve components and integrate them, not just integrate existing components.

## Partition assumptions

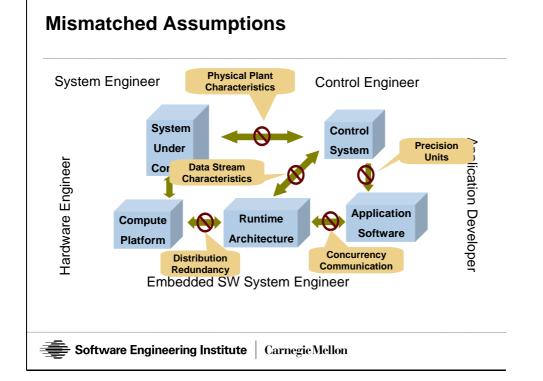

These problems are due to a shift in focus on system integration from a system engineering perspective to a second focus on embedded software system integration.

In this context additional engineering roles interact with each other. These interactions are based on assumptions that are mismatched and not validated. For example control engineers make assumptions about the physical plant in their control algorithm parameters. The translation of these algorithms into code leads to choices such as use of 16 bit arithmetic, which places bounds on domain values represented by the variables, which may be violated by the physical system (Ariane 5).

Similarly, assumptions about sequential execution of separate tasks may result in unexpected behavior when tasks are executed concurrently, e.g., preemptive scheduling of tasks with shared variable communication. Similarly, their mapping onto the computing platform may result in violation of redundancy assumptions. Finally, assumptions about data streams being processed by control algorithms, such as latency jitter, age, and missing stream elements, may not be upheld by the software runtime system and cause controller instability.

| artitions cannot affect other partitions in terms of resource use                                                                                                                                                                                                                                                                                                                         |         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Unmanaged resource sharing across partitions                                                                                                                                                                                                                                                                                                                                              |         |

| <ul> <li>Partitions on different processors utilize shared hardware</li> </ul>                                                                                                                                                                                                                                                                                                            |         |

| Unmanaged partition initiated tasks                                                                                                                                                                                                                                                                                                                                                       |         |

| <ul> <li>DMA transfer continues on partition switch</li> </ul>                                                                                                                                                                                                                                                                                                                            |         |

| <ul> <li>Same memory accessed by DMA &amp; instruction fetch</li> </ul>                                                                                                                                                                                                                                                                                                                   |         |

| Partition cannot affect OS services                                                                                                                                                                                                                                                                                                                                                       |         |

| <ul> <li>Unmanaged DMS transfer may slow cache swap during part<br/>switch</li> </ul>                                                                                                                                                                                                                                                                                                     | tition  |

|                                                                                                                                                                                                                                                                                                                                                                                           |         |

| Software Engineering Institute CarnegieMellon                                                                                                                                                                                                                                                                                                                                             |         |

| Software Engineering Institute CarnegieMellon                                                                                                                                                                                                                                                                                                                                             |         |

|                                                                                                                                                                                                                                                                                                                                                                                           |         |

| artition Assumptions                                                                                                                                                                                                                                                                                                                                                                      |         |

| Partition Assumptions<br>cheduling analysis is partition insensitive                                                                                                                                                                                                                                                                                                                      |         |

| cheduling analysis is partition insensitive <ul> <li>Task set on processor of prorated speed</li> <li>Pre-period deadline may not be met due to late window slot</li> </ul>                                                                                                                                                                                                               |         |

| Partition Assumptions<br>cheduling analysis is partition insensitive<br>• Task set on processor of prorated speed<br>• Pre-period deadline may not be met due to late window slot<br>allocation                                                                                                                                                                                           |         |

| <ul> <li>Partition Assumptions</li> <li>cheduling analysis is partition insensitive <ul> <li>Task set on processor of prorated speed</li> <li>Pre-period deadline may not be met due to late window slot allocation</li> </ul> </li> <li>ault tolerance through redundancy</li> </ul>                                                                                                     |         |

| Partition Assumptions<br>cheduling analysis is partition insensitive<br>• Task set on processor of prorated speed<br>• Pre-period deadline may not be met due to late window slot<br>allocation<br>ault tolerance through redundancy<br>• Partition virtualizes processors                                                                                                                |         |

| <ul> <li>Partition Assumptions</li> <li>cheduling analysis is partition insensitive <ul> <li>Task set on processor of prorated speed</li> <li>Pre-period deadline may not be met due to late window slot allocation</li> </ul> </li> <li>ault tolerance through redundancy <ul> <li>Partition virtualizes processors</li> <li>Partition binding must be considered</li> </ul> </li> </ul> | receive |

Partition assumptions:

Partitions are intended to provide predictability through spade & time partitioning. However, assumptions about the use of partitions to guarantee no side effects of multiple partitions sharing processors and other compute platform resources are not always valid. The above slides give some examples encountered in actual systems.

Such assumptions must be documented as they are not avoidable. Make this explicit and include the problem in the analysis, do not hide it.

There is a second class of system wide problems that center around data stream processing – as found in control systems – and assumptions about their

characteristics. These are the ugly aspects of partitioned architectures as they propagate mismatched assumptions, i.e., faults, throughout the system.

Year 3

# The ugly

## Impact of latency jitter

Latency and jitter can affect the stability of the entire system. Variations of actual write & read times due to preemption and concurrency. Introduce SW noise in the control system.

Latency is a topic where both SW and control engineers meet and must understand each other, see figures below. Physical plants introduce latency. Lots of artifacts cause additional jitter, even loss/duplication of data.

Year 3

| Latency Co                                                                 | ntributors               |                                               |

|----------------------------------------------------------------------------|--------------------------|-----------------------------------------------|

| Operational<br>Environment <ul> <li>Processin</li> <li>Sampling</li> </ul> | latency<br>ignal latency | Control Engineer                              |

|                                                                            | ased Latency             | arnegieMellon <sup>1</sup> Variation & Jitter |

| Preemptive threa                                                           | d scheduling & legad     | cy shared variables                           |

| Concurrency due                                                            | to multiple & multi-c    | ore processors                                |

| Resource conten                                                            | tion                     |                                               |

| Protocol specific                                                          | communication delay      | у                                             |

| Globally asynchr                                                           | onous systems            |                                               |

| Rate group optim                                                           | nization within partitio | ท                                             |

| Migration of parti                                                         | tions                    |                                               |

| Application redur                                                          | ndancy & partition bin   | nding                                         |

| Preemptive sche                                                            | duling of partitions     |                                               |

| Data-driven proc                                                           | essing & cross-partiti   | ion communication                             |

| Software Eng                                                               | ineering Institute Ca    | arnegie Mellon 2                              |

From the perspective of a control engineer there are three major contributors to latency. Furthermore, there is a distinction between latency and age of data. Control algorithms are tuned based on end-to-end latency analysis from a control engineer's perspective.

When implemented as a embedded software system, a number of contributors to latency, latency jitter, and age are purely due to the fact that we have a software-based implementation and are often not fully taken into account in the analysis. This results in the perception that control systems receive data from sensors that are noisier and unless taken into account in a robust control system design will lead to instability behavior due to the dynamics of the executing software.

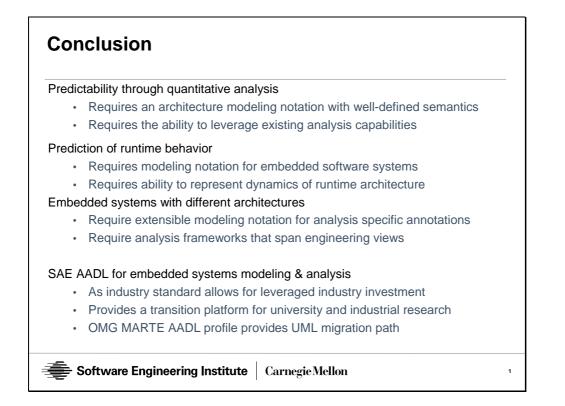

# Conclusion

In this presentation, we focused on performance issues. Other non-functional properties such as security and safety-criticality can also be impacted by the choices being made in the runtime architecture of embedded software systems.

SAE AADL has been designed as an architecture modeling language specifically for embedded systems, and as such provides execution semantics for tasks and communication that allows for analysis of non-functional properties. In particular, it has provided an abstraction of flows with mid-frame and phase-delayed communication semantics as well as sampled and message-based processing. This abstraction allows models to capture the perspective of control engineers and communicate it to embedded software system engineers.

For the UML community OMG MARTE with the AADL profile is an important ongoing development that allows developers to leverage their existing UML tool investments and integrate embedded software system engineering with system engineering through SysML.

## Discussion

Calls for solid design techniques based on architecture models of not just the conceptual system or a platform independent architecture, but also the compute platform and physical environment at the appropriate level of abstraction. Industry has recognized the shortcomings of UML as a notation to model the runtime architecture of embedded software system. The challenge is to model the "what" and abstract away from the "how". This provides an analytic framework for understanding the intent of the embedded application, and through separation of concerns address the appropriate implementation

choices, which in the long run can be addressed through a generation approach from a platform specific model. SAE AADL and OMG MARTE are addressing this need.

Year 3

Q: what experience with AADL in industrial domain.

A: A number of pilot project have been carried out by companies in the avionics, aerospace, and medical domain. The success is not so much in the modeling itself but in the analysis of system architectures. The Mars Rover is a nice example, where priority inversion was detected through analysis and corrected remotely through appropriate runtime support for this system condition.

# Paul Caspi, Verimag: Some issues about IMA in safety critical applications

Was involved in consulting activities in embedded control systems and certification activities: Hermes space-shuttle, RER-A emergency braking, driver-less Lyon subway, Certifer certification agency. Was faced with the IMA question in many of these cases.

## Where does this viewpoint come from?

Computer technology is poorly reliable:

- cars recalled for computing bugs

- Ariane V •

- electricity and telephone crashes

Two questions:

- Is it wise to use this technology in safety critical systems?

- Why, despite of everything, this technology appears as no so bad after all?

## Why simple federated architectures were so successful?

Some partial answers:

- these industries have developed very solid methods •

- very robust computing architecture HW/SW

- o each computer has a periodic behavior triggered by a quasi periodic clock which triggers a single loop software; no dynamic memory, no unbounded loop;

- o WCET relatively easy; jitter minimized

- o little use of OS (a single interrupt taking place when the computer is idle); these programs use to work on bare machines, with no OS at all

- computers periodically sample the physical world but also the other computers

- o non blocking *communication by sampling*

- o can be found in lots of safety-critical systems

- o later modified by so-called Time-Triggered Architecture

- Segregation between critical and less critical tasks

- o allows extending FMEA/FTA methods from HW to computers and SW

- o criticality inherited backward from outputs to tasks

# Two accidentss that could have been avoided by simple federated architectures

#### ARIANE V

Overflow causes failure

A conjunction of several development flaws, including (there are others):

- segregation: the task responsible for flaw was non critical; but was packed in the same computer as critical ones

- since the function was not critical, exceptions needed not be caught

#### Priority inversion in the Mars Pathfinder

Priority inversion is known to take place when multi-tasking (threading) is used in conjunction with synchronization (semaphores).

However, multi-tasking is mandatory in several cases:

- multi-periodic systems

- mix time- and event-triggered systems

Synchronization was considered needed for communication between tasks. *Wrong! Other solutions exist!*

Multi-tasking raises scheduling problems: efficient policies and tests exist for periodic and event-triggered systems

Multi-tasking raises communication problems:

- preemption can corrupt data

- critical sections can be a solution

- scheduling tests can take this into account

### What kind of guarantee should we require for IMA?

- an important certification principle is: *non regression*; keep same safety as before

- IMA has thus to give evidence that

- o no side effect can result from violating the segregation principle

- o no side effect can result from violating the single thread principle

- o more... [not easy to draw a complete list of risks]

Thus the use of a new technology like IMA should be thoroughly justified and its introduction should be progressive and careful.

### Discussion

Q: Airbus has applied IMA on flight warning. The ARIANE case is rather an issue of reuse of SW. Try to avoid by design the issues that were mentioned. When developing modules at level A, we enforce segregation by design. Main issue in the future will be SW reuse. This might become a source problem. When performing reuse, keep within the same domain, reusing in this way the domain

assumptions. A: agree that there are other reasons for ARIANE V case than those mentioned. But still was a good illustration of violating segregation. No semaphore, no critical sections were used for communication in A340, by chance (or by consciousness!!).

Year 3

Q: the ARIANE case is 11 years ago... The important fact is that that in the mean time there has been lots of growth in SW development techniques. Need for incremental validation techniques. Otherwise the integration time grows exponentially; not very reassuring; a good path to bad situations.

Q: do you mean that level B,C should also go through severe gualification procedures? A: when I am aware of side effect, then I know how criticality propagates and can qualify what is B,C properly. In the case we discussed, it should have been inherited as an A. Of course this is not a good technique since then everything would become level A. Instead, show that non-critical pieces of SW cannot harm critical ones.

# John Rushby, SRI: Compositional Assurance for IMA [presented by Albert Benveniste, in absence of John Rushby]

Selected slides enclosed

# **Just-In-Time Certification**

John Rushby

Computer Science Laboratory SRI International Menlo Park, California, USA

John Rushby, SRI

Just-In-Time Certification: 1

## Certification

- Provides assurance that deploying a given system does not pose an unacceptable risk of adverse consequences

- Certification methods should be effective (i.e., they work) and credible (i.e., they work for the reason we think they do)

- Current methods have been effective, but are they credible?

- Current methods of assurance explicitly depend on

- Standards and regulations

- Rigorous examination of the whole, finished system

And implicitly on

- Conservative practices

- Safety culture

- All of these are changing

## Overview

- Scientific certification

- Compositional certification

- Just-in-time certification

John Rushby, SRI

Just-In-Time Certification: 3

# **A** Recent Incident

- Fuel emergency on Airbus A340-642, G-VATL, on 8 February 2005 (AAIB SPECIAL Bulletin S1/2005)

- Toward the end of a flight from Hong Kong to London: two engines shut down, crew discovered they were critically low on fuel, declared an emergency, landed at Amsterdam

- Two Fuel Control Monitoring Computers (FCMCs) on this type of airplane; they cross-compare and the "healthiest" one drives the outputs to the data bus

- Both FCMCs had fault indications, and one of them was unable to drive the data bus

- Unfortunately, this one was judged the healthiest and was given control of the bus even though it could not exercise it

- Further backup systems were not invoked because the FCMCs indicated they were not both failed

# Implicit and Explicit Factors

- See also ATSB incident report for in-flight upset of Boeing 777, 9M-MRG (Malaysian Airlines, near Perth Australia)

- Maybe effectiveness of current certification methods depends on implicit factors such as safety culture, conservatism

- Current business models are leading to a loss of these

Outsourcing, COTS, complacency, innovation

- Surely, a credible certification regime should be effective on the basis of its explicit practices

- All assurance is based on **arguments** that purport to justify certain **claims**, based on documented **evidence**

- There are two approaches to assurance: standards-based, and goal-based

John Rushby, SRI

Just-In-Time Certification: 5

## The Standards-Based Approach to Software Certification

- E.g., airborne s/w (DO-178B), security (Common Criteria)

- Applicant follows a prescribed method (or processes)

- Delivers prescribed outputs

- \* e.g., documented requirements, designs, analyses, tests and outcomes, traceability among these

- Standard usually defines only the evidence to be produced

- The claims and arguments are implicit

- Hence, hard to tell whether given evidence meets the intent

- Works well in fields that are stable or change slowly

- $\circ~$  Can institutionalize lessons learned, best practice

- $\star\,$  e.g. evolution of DO-178 from A to B to C

- But less suitable with novel problems, solutions, methods

## The Goal-Based Approach to Software Certification

- E.g., air traffic management (CAP670 SW01), UK aircraft

- Applicant develops an assurance case

- Whose outline form may be specified by standards or regulation (e.g., MOD DefStan 00-56)

- Makes an explicit set of goals or claims

- Provides supporting evidence for the claims

- And arguments that link the evidence to the claims

- \* Make clear the underlying assumptions and judgments

- $\star\,$  Should allow different viewpoints and levels of detail

- The case is evaluated by independent assessors

- Explicit claims, evidence, argument

John Rushby, SRI

Just-In-Time Certification: 7

# Multiple Forms of Evidence

- More evidence is required at higher Levels/EALs/SILs

- What's the argument that these deliver increased assurance?

- Generally an implicit appeal to diversity

- And belief that diverse methods fail independently

- Not true in *n*-version software, should be viewed with suspicion here too

- Need to know the arguments supported by each item of evidence, and how they compose