# The Worst-Case Execution Time Problem — Overview of Methods and Survey of Tools

Reinhard Wilhelm, Jakob Engblom, Andreas Ermedahl, Niklas Holsti, Stephan Thesing, David Whalley, Guillem Bernat, Christian Ferdinand, Reinhold Heckmann, Tulika Mitra, Frank Mueller, Isabelle Puaut, Peter Puschner, Jan Staschulat, Per Stenström

The determination of upper bounds on execution times, commonly called Worst-Case Execution Times (WCETs), is a necessary step in the development and validation process for hard real-time systems. This problem is hard if the underlying processor architecture has components such as caches, pipelines, branch prediction, and other speculative components. This article describes different approaches to this problem and surveys several commercially available tools and research prototypes.

Categories and Subject Descriptors: J.7 [COMPUTERS IN OTHER SYSTEMS]: ; C.3 [SPECIAL-PURPOSE AND APPLICATION-BASED SYSTEMS]: REAL-TIME AND EMBEDDED SYSTEMS

General Terms: Verification, Reliability

Additional Key Words and Phrases: Hard real time, worst-case execution times

Tool descriptions were provided by Guillem Bernat, Christian Ferdinand, Andreas Ermedahl, Reinhold Heckmann, Niklas Holsti, Tulika Mitra, Frank Mueller, Isabelle Puaut, Peter Puschner, Jan Staschulat, Per Stenström and David Whalley. Bernat is with Rapita Systems Ltd., IT Center, York Science Park, Heslington, York YO10 5DG, United Kingdom. Ferdinand and Heckmann are with AbsInt Angewandte Informatik, Science Park 1, D-66123 Saarbrücken. Mitra is with Department of Computer Science, School of Computing, 3 Science Drive 2, National University of Singapore, Singapore 117543. Mueller is with Department of Computer Science, North Carolina State University, Raleigh, NC 27695-8206. Puaut is with IRISA, Campus univ. de Beaulieu, F-35042 Rennes Cédex. Puschner is with Inst. für Technische Informatik, TU Wien, A-1040 Wien. Staschulat is with Inst. for Computer and Communication Network Engineering, Technical University Braunschweig, Hans-Sommer-Str. 66, D-38106 Braunschweig. Stenström is with Department of Computer Engineering, Chalmers University of Technology, S-412 96 Göteborg.

Permission to make digital/hard copy of all or part of this material without fee for personal or classroom use provided that the copies are not made or distributed for profit or commercial advantage, the ACM copyright/server notice, the title of the publication, and its date appear, and notice is given that copying is by permission of the ACM, Inc. To copy otherwise, to republish, to post on servers, or to redistribute to lists requires prior specific permission and/or a fee. © 20YY ACM 0164-0925/20YY/0500-00001 \$5.00

Work reported herein was supported by the European Accompanying Measure ARTIST, Advanced Real Time Systems, and the European Network of Excellence, ARTIST2.

Wilhelm and Thesing are with Fachrichtung Informatik, Saarland University, D-66041 Saarbrücken, Germany. Engblom is with Virtutech AB, Norrtullsgatan 15, SE-113 27 Stockholm. Ermedahl is with Department of Computer Science and Electronics, Mälardalen University, PO Box 883, SE 72123 Västerås, Sweden. Holsti is with Tidorum Ltd, Tiirasaarentie 32, FI-00200 Helsinki, Finland. Whalley is with Computer Science Department, Florida State University, Tallahassee, FL 32306-4530, USA. These authors are responsible for the article and have written the introduction to the problem area and the overview of the techniques. They have also edited the tool descriptions to make them more homogeneous.

# 1. INTRODUCTION

Hard real-time systems need to satisfy stringent timing constraints, which are derived from the systems they control. In general, upper bounds on the execution times are needed to show the satisfaction of these constraints. Unfortunately, it is not possible in general to obtain upper bounds on execution times for programs. Otherwise, one could solve the halting problem. However, real-time systems only use a restricted form of programming, which guarantees that programs always terminate; recursion is not allowed or explicitly bounded as are the iteration counts of loops. A reliable guarantee based on the worst-case execution time of a task could easily be given if the worst-case input for the task were known. Unfortunately, in general the worst-case input is not known and hard to derive.

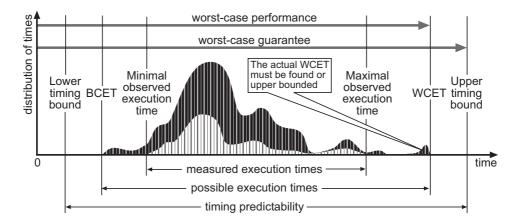

We assume that a real-time system consists of a number of tasks, which realize the required functionality. Figure 1 depicts several relevant properties of a real-time task. A task typically shows a certain variation of execution times depending on the input data or different behavior of the environment. The set of all execution times is shown as the upper curve. The shortest execution time is called the *best*case execution time (BCET), the longest time is called the *worst-case execution* time (WCET). In most cases the state space is too large to exhaustively explore all possible executions and thereby determine the exact worst-case and best-case execution times.

Today, in most parts of industry the common method to estimate executiontime bounds is to measure the *end-to-end* execution time of the task for a subset of the possible executions—test cases. This determines the *minimal observed* and *maximal observed execution times*. These will in general overestimate the BCET and underestimate the WCET and so are not safe for hard real-time systems. This method is often called *dynamic timing analysis*.

Newer measurement-based approaches make more detailed measurements of the execution time of different *parts* of the task and combine them to give better estimates of the BCET and WCET for the whole task. Still, these methods are rarely guaranteed to give bounds on the execution time.

Bounds on the execution time of a task can be computed only by methods that consider all possible execution times, that is, all possible executions of the task. These methods use abstraction of the task to make timing analysis of the task feasible. Abstraction loses information, so the computed WCET bound usually overestimates the exact WCET and vice versa for the BCET. The WCET bound represents the *worst-case guarantee* the method or tool can give. How much is lost depends both on the methods used for timing analysis and on overall system properties, such as the hardware architecture and characteristics of the software. These system properties can be subsumed under the notion of *timing predictability*.

The two main criteria for evaluating a method or tool for timing analysis are thus *safety*—does it produce bounds or estimates?— and *precision*—are the bounds or estimates close to the exact values?

Performance prediction is also required for application domains that do not have hard real-time characteristics. There, systems may have deadlines, but are not required to absolutely observe them. Different methods may be applied and different criteria may be used to measure the quality of methods and tools.

Fig. 1. Basic notions concerning timing analysis of systems. The lower curve represents a subset of measured executions. Its minimum and maximum are the *minimal observed execution times* and *maximal observed execution times*, resp. The darker curve, an envelope of the former, represents the times of all executions. Its minimum and maximum are the *best-case* and *worst-case execution times*, resp., abbreviated BCET and WCET.

The literature on timing analysis has created a confusion by not always making a distinction between worst-case execution times and estimates for them. We will avoid this misnomer in this survey.

We will use the term *timing analysis* for the process of deriving execution-time bounds or estimates. A tool that derives bounds or estimates for the execution times of application tasks is called a *timing-analysis tool*. We will concentrate on the determination of upper bounds or estimates of the WCET unless otherwise stated. All tools described in Section 6 with the exception of SymTA/P offer timing analysis of tasks in uninterrupted execution. Here, a *task* may be a unit of scheduling by an operating system, a subroutine, or some other software unit. This unit is mostly available as a fully-linked executable. Some tools, however, assume the availability of source code and of a compiler supporting a subsequent timing analysis.

#### Organization of the article

Section 2 introduces the problem and its subproblems and describes methods being used to solve it. Sections 3 and 4 present two categories of approaches, static and measurement-based. Section 6 consists of detailed tool descriptions. Section 7 resumes the state of the art and the deployment and use in industry. Section 8 lists limitations of the described tools. Section 9 gives a condensed overview of the tools in a tabulated form. Section 10 explains, how timing analysis is or should be integrated in the development process. Section 11 concludes the paper by presenting open problems and the perspectives of the domain mainly determined by architectural trends.

# 2. OVERVIEW OF TIMING-ANALYSIS TECHNIQUES

This section describes the problems that make timing analysis both difficult and interesting as a research topic, presents a decomposition of the problem into subtasks, and categorizes some of the techniques used to determine bounds on execution times. A given timing-analysis method or tool may not address or solve all these subtasks and different methods and tools may solve the same subtask in different ways.

#### 2.1 Problems and Requirements

Timing analysis attempts to determine bounds on the execution times of a task when executed on a particular hardware. The time for a particular execution depends on the path through the task taken by control and the time spent in the statements or instructions on **this path** on **this hardware**. Accordingly, the determination of execution-time bounds has to consider the potential control-flow paths and the execution times for this set of paths. A modular approach to the timing-analysis problem splits the overall task into a sequence of subtasks. Some of them deal with properties of the control flow, others with the execution time of instructions or sequences of instructions on the given hardware.

2.1.1 Data-Dependent Control Flow. The task to be analyzed attains its WCET on one (or sometimes several) of its possible execution paths. If the input and the initial state leading to the execution of this worst-case path were known, the problem would be easy to solve. The task would then be started in this initial state with this input, and the execution time would be measured. In general, however, this worst-case input and initial state are **not** known and hard or impossible to determine. A data structure, the task's control-flow graph, CFG, describes a superset of the set of all execution paths. The task's call graph usually is integrated into the CFG.

A first problem that has to be solved is the construction of the control-flow graph and call graph of the task from a source or a machine-code version of the task. They must contain all of the instructions of the task (function closure) under analysis. Problems are created by dynamic jumps and dynamic calls with computed target address. Dynamic jumps are mainly due to switch/case structures and are a problem only when analyzing machine code, because even assembly code usually labels all switch/case branches. Dynamic calls also occur in source code in the form of calls through function pointers and calls to virtual functions. A component of a timing-analysis tool which reconstructs the CFG from a machine program is often called a *Frontend*.

Different paths through the CFG are taken depending directly or indirectly on input data. Some paths in the superset described by the CFG will never be taken, for instance those that have contradictory consecutive conditions. Eliminating such paths may increase the precision of timing analysis. The more the analysis knows about the data flow through the task, the more it knows about the outcome of and the relationship between conditions, the more paths it may recognize as infeasible.

A phase called *Control-Flow Analysis* (CFA) determines information about the possible flow of control through the task to increase the precision of the subsequent analyzes. Control flow analysis may attempt to exclude infeasible paths, determine

execution frequencies of paths or the relation between execution frequencies of different paths or subpaths etc. Control-Flow Analysis has previously been called High-level Analysis.

Tasks spend most of their execution time in loops and in (recursive) functions. Therefore, it is an essential task of CFA to determine bounds on the iterations of loops and on the depth of recursion of functions. A necessary ingredient for this are the values of variables, registers, or memory cells occurring in conditions tested for termination of loops or recursion.

It is worth noting that complex processors may actually execute an instruction stream in a different order than the one determined by control-flow analysis. This is due to pipelining (prefetching and delayed branching), branch prediction, and speculative or out-of-order execution.

2.1.2 Context Dependence of Execution Times. Early approaches to the timinganalysis problem assumed context independence of the timing behavior; the execution times for individual instructions were independent from the execution history and could be found in the manual of the processor. From this context independence was derived a structure-based approach [Shaw 1989]: if a task first executes a code snippet A and then a snippet B, the worst-case bound for A; B was determined as that for A,  $ub_A$ , added to that determined for B,  $ub_B$ , formally  $ub_{A;B} = ub_A + ub_B$ . This context independence, however, is no longer true for modern processors with caches and pipelines. The execution time of individual instructions may vary by several orders of magnitude depending on the state of the processor in which they are executed. Thus, the execution time of B can heavily depend on the execution state that the execution of A produced. Any tool should exploit the knowledge that A was executed before B to determine a precise upper bound for B in the context A. Determining the upper bound  $ub_{A;B}$  for A; B by  $ub_{A;B} = ub_A + ub_B$  ignores this information and will in general not obtain precise results.

A phase called *Processor-Behavior Analysis* gathers information on the processor behavior for the given task, in particular the behavior of the components that influence the execution times, such as memory, caches, pipelines, and branch prediction. It determines upper bounds on the execution times of instructions or basic blocks. Processor-Behavior Analysis has previously been called Low-level Analysis.

2.1.3 *Timing Anomalies.* The complexity of the processor-behavior analysis subtask and the set of applicable methods critically depend on the complexity of the processor architecture [Heckmann et al. 2003]. Most powerful microprocessors suffer from timing anomalies [Lundqvist and Stenström 1999c]. Timing anomalies are contra-intuitive influences of the (local) execution time of one instruction on the (global) execution time of the whole task. This concept is quite complex. So, we will try to explain it in some detail.

We assume that the system under consideration, executing hardware and executed software, are too complex to allow exhaustive execution or simulation. In addition, not all input data are known, so that parts of the execution state are missing in the analysis. Unknown parts of the state lead to non-deterministic behavior, if decisions depend on these unknown parts. For timing analysis, this means that the execution of an instruction or an instruction sequence considered in an initial

ACM Transactions on Programming Languages and Systems, Vol. V, No. N, Month 20YY.

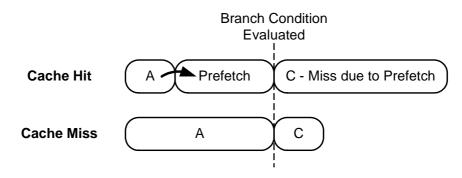

abstract state may produce different times based on different assumptions about the missing state components. For example, missing information about whether the next instruction will be in the cache may lead to one execution starting with a cache load contributing the cache-miss penalty to the execution time, while another execution will start with an instruction fetch from the cache. Intuition would suggest that the latter execution would always lead to the shorter execution time of the whole task. On processors with timing anomalies, however, this need not be true. The latter execution may in fact lead to a longer task execution time. This was observed on the Motorola ColdFire 5307 processor [Heckmann et al. 2003]. The reason is the following. This processor speculates on the outcome of conditional branches, that is, it prefetches instructions in one of the directions of the conditional branch. When the condition is finally evaluated it may turn out that the processor speculated in the wrong direction. All the effects produced so far have to be undone. In addition, fetching the wrong instructions has partly ruined the cache contents. Taken together, the costs of the mis-prediction exceed the costs of a cache miss. Hence, the local worst case, the I-cache miss, leads to the globally shorter execution time since it prevents a more expensive branch mis-prediction. This exemplifies one of the reasons for timing anomalies, speculation-caused anomalies. One such anomaly is shown in Figure  $2.^1$

Fig. 2. A timing anomaly caused by speculation.

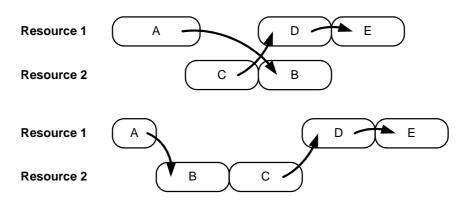

Another type of timing anomalies are instances of well-known scheduling anomalies, first discovered and published by Graham [Graham 1966]. These occur when a sequence of instructions, partly depending on each other, can be scheduled differently on the hardware resources, such as pipeline units. Depending on the selected schedule the execution of the instructions or pipeline phases takes different times. Figure 3 shows an example of a scheduling-caused timing anomaly.

Timing anomalies violate an intuitive, but incorrect assumption, namely that always taking the local worst-case transition when there is a choice produces the global worst-case execution time. This means that the analysis cannot greedily limit its search for upper bounds by choosing the worst cases for each instruction. The existence of timing anomalies in a processor thus has a strong influence on the applicability of methods for timing analysis for that processor [Heckmann et al. 2003].

<sup>&</sup>lt;sup>1</sup>Figures 2 and 3 are taken from [Reineke et al. 2006].

ACM Transactions on Programming Languages and Systems, Vol. V, No. N, Month 20YY.

Fig. 3. A scheduling-caused timing anomaly.

- —The assumption that only local worst cases have to be considered to safely determine upper bounds on global execution times is unsafe.

- -The assumption that one could identify a worst initial execution state, to safely start measurement or analysis of a piece of code in, is unsafe.

The consequences for timing analysis of systems to be executed on processors with timing anomalies are as follows:

- —The analysis may be forced to follow execution through several successor states, whenever it encounters an abstract state with a non-deterministic choice between successor states. This may lead to a quite large state space to consider.

- —The analysis has to be able to express the absence of state information instead of assuming some worst initial state. Absent information in abstract states stands for all potential concrete instances of these missing state components, thus do not wrongly exclude any possible execution.

#### 2.2 Classification of Approaches

We present two different classes of methods.

Static methods. These methods do not rely on executing code on real hardware or on a simulator. They rather take the task code itself, maybe together with some annotations, analyze the set of possible control flow paths through the task, combine control flow with some (abstract) model of the hardware architecture, and obtain upper bounds for this combination. One such static approach is described in detail in [Wilhelm 2005].

*Measurement-based methods.* These methods execute the task or task parts on the given hardware or a simulator for some set of inputs. They then take the measured times and derive the maximal and minimal observed execution times, see Figure 1, or their distribution or combine the measured times of code snippets to results for the whole task.

Static methods emphasize *safety* by producing bounds on the execution time, guaranteeing that the execution time will not exceed these bounds. The bounds allow safe schedulability analysis of hard real-time systems.

Measurements can be used in different ways. End-to-end measurements of a subset of all possible executions produce estimates, not bounds. They may be useful for applications that do not require guarantees, typically non-hard real-time systems. They may give the developer a feeling about the execution time in common cases and the likelihood of the occurrence of the worst case. Measurement can also be applied to code snippets after which the results are combined to estimates for the whole program in similar ways as used in static methods. Guarantees that safe bounds are obtained can currently only be given for rather simple architectures due to the reasons given in Section 2.1.

### 2.3 Methods for Subtasks of Timing Analysis

We briefly describe some methods that are being used to solve the above mentioned subtasks of timing analysis. These methods are imported from other fields of computer science such as compiler construction, computer architecture, performance estimation, and optimization.

These methods can be categorized according to several properties: whether they are *automatic* or *manual*, whether they are *generic*, i.e., stand for a whole class of methods, or are *specific instances* of such a generic method, and whether they are applied at *analysis time* or at *tool-construction time*.

2.3.1 Static Program Analysis. Static program analysis is a generic method to determine properties of the dynamic behavior of a given task without actually executing the task [Cousot and Cousot 1977; Nielson et al. 1999]. These properties are often undecidable. Therefore, sound approximations are used; they have to be correct, but may not necessarily be complete. An example from our domain is instruction-cache analysis, which attempts to determine for each point in the task which instructions will be in the cache every time execution reaches this program point. For straight-line programs and known initial cache contents this is easy and can be done by a standard simulator. However, it is in general undecidable for tasks whose control flow depends on input data. A sound analysis will compute a subset of the instructions that will definitely be in the instruction cache every time execution reaches the program point. More instructions may actually be in the cache, but the analysis may not be able to find this out. Several instances of static program analysis are being used for timing analysis.

2.3.2 Simulation. Simulation is a standard technique to estimate the execution time for tasks on hardware architectures. A key advantage of this approach is that it is possible to derive rather accurate estimations of the execution time for a task for a given set of input data and assuming sufficient detail of the timing model of the architectural simulator. [Desikan et al. 2001] compares timing measurements with runs on different simulators and gives indication of the errors obtained for an Alpha architecture. The Simplescalar [Austin et al. 2002] simulator among others is used. Simplescalar is also used by some WCET groups. The results show large differences in timing compared to the measured values. The measurement method used might be questioned, but at least it shows that the Simplescalar simulator should not be trusted as a clock-cycle accurate simulator for all types of architectures.

Unfortunately, standard cycle-accurate simulators cannot be used off-hand in static methods for timing analysis, since static methods should not simulate exe-

cution for particular input data, but rather for all input data. Thus, input data is assumed to be unknown. Unknown input data leads to unknown parts in the execution state of the processor and non-deterministic decisions at control-flow branches. Simulators modified to cope with these problems are being used in several of the tools described later.

2.3.3 Abstract Processor Models. Processor-behavior analysis needs a model of the architecture. This need not be a concrete model implementing all of the functionality of the target hardware. A simplified model that is conservative with respect to the timing behavior is sufficient. Such an abstract processor model either is a part of the engine for processor-behavior analysis or is input to the construction of such an engine. In any case, the construction of an abstract processor model is done at tool-construction time.

One inherent limitation of all the approaches that are based on some model of the hardware architecture is that they rely on the timing accuracy of the model. In general, computer vendors do not disclose enough information about the microarchitecture so that one can develop and safely validate the accuracy of a timing model. Without such validation, any WCET tool based on an abstract model of the hardware cannot be trusted without further assurance. Additional means for model validation have to be taken. This could be done by measurements. Measured execution times are compared against predicted bounds. Another method is trace validation checking whether externally observable traces are projections of traces as predicted by the model. Not all events predicted by the model are externally observable. However, both methods are similar to testing; they can discover the presence of errors, but not prove their absence. Stronger guarantees can be given by equivalence checking between different abstraction levels. An ongoing research activity is the formal derivation of abstract processor models from concrete models.

2.3.4 Integer Linear Programming (ILP). Linear programming [Chvatal 1983] is a generic methodology to code the requirements of a system in the form of a system of linear constraints. Additionally given is a goal function that has to be maximized or minimized to obtain an optimal assignment of values to the system's variables. One speaks of Integer Linear Programming if these values are required to be integers. While linear programs can be solved in polynomial time, requiring the solution to be integer makes the problem NP-hard. This indicates that the use of ILP should be restricted to small problem instances or to subproblems of timing analysis generating only small problem instances.

In the timing-analysis domain, ILP is used in the IPET approach to bounds calculation, see Section 3.4. The control flow of tasks is translated into integer linear programs, essentially by coding Kirchhoff's rule about the conservation of flow. Extra information about the control flow can often be coded as additional constraints. The goal function expresses the execution time of the program under analysis. Its maximal value is then an upper bound for all execution times.

An escape from the exponential complexity that is often taken in other application domains is to use heuristics. These heuristics will in general only arrive at suboptimal solutions. A suboptimal solution in timing analysis represents an unsafe estimate for the WCET. Thus the escape of resorting to heuristics is barred.

ILP has been used for a completely different purpose, namely to model (very simple) processors [Li et al. 1995b; Li et al. 1995a]. However, the complexity of solving the resulting integer linear programs did not allow this approach to scale [Wilhelm 2004].

2.3.5 Annotation. The annotation of tasks with information available from the developer is a generic technique to support subsequently applied automatic validation techniques. The developer using a WCET tool may have to supply some information that the tool needs in separate files or by annotating the task. This information describes

- -the memory layout and any needed characteristics of memory areas,

- -ranges for the input values of the task,

- —information about the control flow of the task if not determined automatically, e.g. loop bounds, shapes of nested loops, if iterations of inner loops depend on iteration variables of outer loops, frequencies of paths or branches taken,

- -deviations from the standard function-calling conventions, and

- -directives as to the desired precision of the result, which often depends on the invested effort for differentiating contexts.

2.3.6 *Frontend.* Most WCET tools analyze software at the executable level, since only at this level is all necessary information available. The first phase in timing analysis is thus the decoding of the executable and the reconstruction of its control flow. This can be quite involved depending on the instruction set of the processor and the code-generation patterns of the compiler. Some timing analysis tools are integrated with a compiler which emits the necessary CFG and call graph for the analysis.

2.3.7 Visualization of Results. The results of timing analysis are presented in human-readable form, best in the form of an informative visualization. This usually shows the call and control-flow graphs annotated with computed timing information and possibly also information about the processor states.

The following two sections present the two categories of approaches, static and measurement-based approaches. Section 6 describes the available tools from these two categories in more detail.

# 3. STATIC METHODS

This class of methods does not rely on executing code on real hardware or on a simulator, but rather takes the task code itself, combines it with some (abstract) model of the system, and obtains upper bounds from this combination.

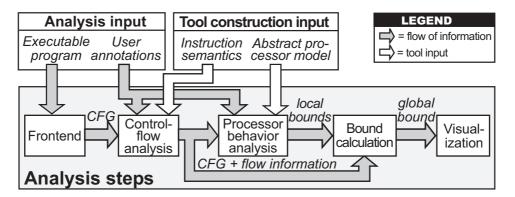

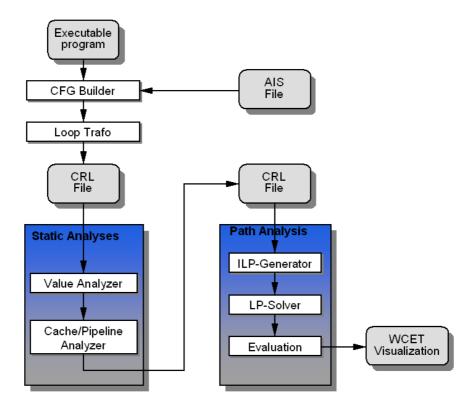

Figure 4 shows the core components of a static timing-analysis tool and the flow of information.

#### 3.1 Value Analysis

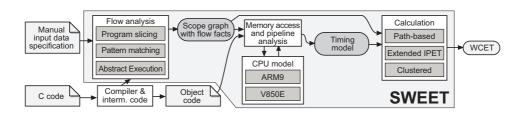

This is a static program analysis. Any method for data-cache behavior analysis needs to know effective memory addresses of data, in order to determine where a memory access goes. Effective addresses are only available at run time. However, a *value analysis*, as implemented in aiT, see Section 6.1, Bound-T, see Section 6.2, and in SWEET, see Section 6.7, is able to determine many effective addresses in

Fig. 4. Core components of a timing-analysis tool. The flow of information is shown by arrows filled in grey. The arrows filled white represent tool-construction input.

disciplined code statically [Thesing et al. 2003]. It does so by computing ranges for the values in the processor registers and local variables at every program point. This analysis is also useful to determine loop bounds and to detect infeasible paths.

#### 3.2 Control-Flow Analysis

The purpose of control-flow analysis is to gather information about possible execution paths. The set of paths is always finite, since termination must be guaranteed. The exact set of paths can in general not be determined. Any superset of this set will be a safe approximation. The smaller this superset is the better. The execution time of any safely eliminated path can be ignored in computing the upper bound and thus will not contribute to it.

The input of flow analysis consists of a task representation, e.g. the call graph and the control-flow graph of the task and possibly additional information such as ranges for the input data and iteration bounds of some loops. The latter are either determined by a preceding value analysis or provided by the user. The result of the flow analysis can be seen as constraints on the dynamic behavior of the task. This includes information on which functions may be called, on dependencies between conditionals, and on the (in)feasibility of paths, etc.

There are a number of approaches to automatic flow analysis. Some of the methods are general, while others are specialized for certain types of code constructs. The methods also differ in the type of codes they analyze, i.e., source-, intermediate-(inside the compiler) or machine code.

Control-flow analysis is generally easier on source code than on machine code, but it is difficult to map the results to the machine-code program because compilation, in particular code optimization and linking may change the control-flow structure.

Gustafsson et al. [Gustafsson et al. 2003] uses a combination of flow-analysis methods. For simple loops, pattern matching is used. The pattern matching uses the results of a value analysis. For more complex loop constructs, an abstract interpretation-based method is used [Gustafsson 2000; Gustafsson et al. 2005]. The analysis is performed on the intermediate code level. Pattern-matching methods are based on the fact that for most loops the supported compilers use the same or similar groups of machine instructions to initialize, update and test loop counters.

ACM Transactions on Programming Languages and Systems, Vol. V, No. N, Month 20YY.

Pattern-matching finds occurrences of such instruction groups in the code and analyzes the values of the instruction operands to find the counter range, for example in terms of the initial value, the increment or decrement and the final value of the counter. The drawback of this method is that it can be defeated by compiler optimizations, or by evolution of the compiler itself, if this changes the emitted instruction patterns so much that the matching fails.

Bound-T, see Section 6.2, finds loop bounds by modelling the computation, instruction by instruction, using affine equations and inequalities (Presburger Arithmetic). Bound-T then examines the model to find variables that act as loop counters. If Bound-T also finds bounds on the initial and final values of the variable, a simple computation gives a bound on the number of loop iterations.

Whalley et al. [Healy et al. 1998; Healy and Whalley 1999] use data flow analysis and special algorithms to calculate bounds for single and nested loops in conjunction with a compiler. [Stappert and Altenbernd 2000] uses symbolic execution on the source code level to derive flow information. aiT's loop-bound analysis, see Section 6.1, is based on a combination of an interval-based abstract interpretation and pattern-matching [Thesing 2004] working on the machine code.

The result of control-flow analysis is an annotated syntax tree for the structurebased approaches, see Section 3.4, and a set of flow facts about the transitions of the control-flow graph, otherwise. These flow facts are translated into a system of constraints for the methods using implicit path enumeration, see Section 3.4.

### 3.3 Processor-Behavior Analysis

As stated in Section 2.1.2, a typical processor contains several components that make the execution time context-dependent, such as memory, caches, pipelines and branch prediction. The execution time of an individual instruction, even a memory access depends on the execution history. To find precise execution-time bounds for a given task, it is necessary to analyze what the occupancy state of these processor components for all paths leading to the task's instructions is. Processor-behavior analysis determines invariants about these occupancy states for the given task. In principle, no tool is complete that does not take the processor periphery into account, i.e., the full memory hierarchy, the bus, and peripheral units. In so far, an even better term would be *hardware-subsystem behavior analysis*. The analysis is done on a linked executable, since only this contains all the necessary information. It is based on an abstract model of the processor, the memory subsystem, the buses, and the peripherals, which is conservative with respect to the timing behavior of the concrete hardware, i.e., it never predicts an execution time less than that which can be observed on the concrete processor.

The complexity of deriving an abstract processor model strongly depends on the class of processor used.

—For simpler 8bit and 16bit processors the timing model construction is rather simple, but still time consuming, and rather simple analyses are required. Complicating factors for the processor behavior analysis include instructions with varying execution time due to argument values and varying data reference time due to different memory area access times.

-For somewhat more advanced 16bit and 32bit processors, like the NEC V850E,

possessing a simple (scalar) pipeline and maybe a cache, one can analyze different hardware features separately, since there are no timing anomalies, and still achieve good results. Complicating factors are similar as for the simpler 8- and 16-bit processors, but also include varying access times due to cache hits and misses and varying pipeline overlap between instructions.

—More advanced processors, which possess many performance enhancing features that can influence each other, will exhibit timing anomalies. For these, timingmodel construction is very complex. Also the analyses to be used are less modular and more complex [Heckmann et al. 2003].

In general, the execution-time bounds derived for an instruction depend on the states of the processor at this instruction. Information about the processor states is derived by analyzing potential execution histories leading to this instruction. Different states in which the instruction can be executed may lead to widely varying execution times with disastrous effects on precision. For instance, if a loop iterates 100 times, but the worst case of the body,  $e_{body}$ , only really occurs during one of these iterations and the others are considerably faster (say twice as fast), the overapproximation is  $99 * 0.5 * e_{body}$ . Precision can be gained by regarding execution in classes of execution histories separately, which correspond to *flow contexts*. These flow contexts essentially express by which paths through loops and calls control can arrive at the instruction. Wherever information about the processor's execution state is missing a conservative assumption has to be made or all possibilities have to be explored.

Most approaches use Data Flow Analysis, a static program-analysis technique based on the theory of Abstract Interpretation [Cousot and Cousot 1977]. These methods are used to compute invariants, one per flow context, about the processor's execution states at each program point. If there is one invariant for each program point, then it holds for all execution paths leading to this program point. Different ways to reach a basic block may lead to different invariants at the block's program points. Thus, several invariants could be computed. Each holds for a set of execution paths, and the sets together form a partition of the set of all execution paths leading to this program point. Each set of such paths corresponds to what sometimes is called a *calling context*, *context* for short. The invariants express static knowledge about the contents of caches, the occupancy of functional units and processor queues, and of states of branch-prediction units. Knowledge about cache contents is then used to classify memory accesses as definite cache hits (or definite cache misses). Knowledge about the occupancy of pipeline queues and functional units is used to exclude pipeline stalls. Assume that one uses the following method: First accept Murphy's Law, that everything that can go wrong, actually goes wrong, assuming worst cases all over. Then both types of "good news" of the type described above can often be used to reduce the upper bounds for the execution times. Unfortunately, this approach is not safe for many processor architectures with timing anomalies, see Section 2.1.3.

#### 3.4 Estimate Calculation

The purpose is to determine an estimate for the WCET. In dynamic approaches the WCET estimate can underestimate the WCET, since only a subset of all executions

ACM Transactions on Programming Languages and Systems, Vol. V, No. N, Month 20YY.

is used to compute it. Combining measurements of code snippets to end-to-end execution times can also overestimate the WCET, if pessimistic estimates for the snippets are combined. In static approaches this phase computes an upper bound of all execution times of the whole task based on the flow and timing information derived in the previous phases. It is then usually called *Bound Calculation*. There are three main classes of methods combining analytically determined or measured times to end-to-end estimates proposed in literature: *structure-based*, *path-based*, and techniques using *implicit path enumeration* (IPET).

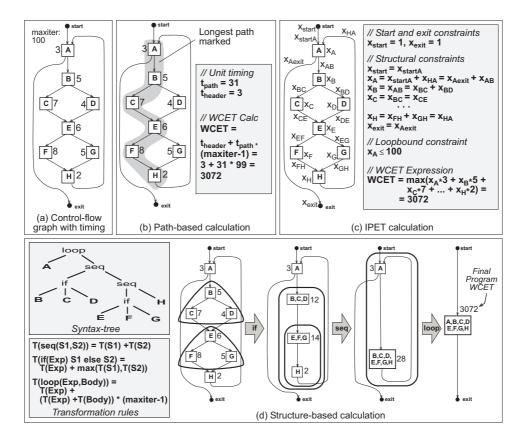

Fig. 5 taken from [Ermedahl 2003] shows the different methods. Fig. 5(a) shows an example control-flow graph with timing on the nodes and a loop-bound flow fact.

In structure-based bound calculation as used in Heptane, cf. [Colin and Puaut 2000] and Section 6.6, an upper bound is calculated in a bottom-up traversal of the syntax tree of the task combining bounds computed for constituents of statements according to combination rules for that type of statement [Colin and Bernat 2002; Colin and Puaut 2000; Lim et al. 1995]. Fig. 5(d) illustrates how a structure-based method would proceed according to the task syntax tree and given combination rules. Collections of nodes are collapsed into single nodes, simultaneously deriving a timing for the new node. As stated in Section 2.1.2, precision can only be obtained if the same code snippet is considered in a number of different *flow contexts*, since the execution times in different flow contexts can vary widely. Taking flow contexts into account requires transformations of the syntax tree to reflect the different contexts. Most of the profitable transformations, e.g. loop unrolling, are easily expressed on the syntax tree [Colin and Bernat 2002].

Some problems of the structure-based approach are that not every control flow can be expressed through the syntax tree, that the approach assumes a very straightforward correspondence between the structures of the source and the target program not easily admitting code optimizations, and that it is in general not possible to add additional flow information as can be done in the IPET case.

In path-based bound calculation, the upper bound for a task is determined by computing bounds for different paths in the task, searching for the overall path with the longest execution time [Healy et al. 1999; Stappert and Altenbernd 2000; Stappert et al. 2001]. The defining feature is that possible execution paths are represented *explicitly*. The path-based approach is natural within a single loop iteration, but has problems with flow information extending across loop-nesting levels. The number of paths is exponential in the number of branch points, possibly requiring heuristic search methods.

Fig. 5(b) illustrates how a path-based calculation method would proceed over the graph in Fig. 5(a). The loop in the graph is first identified and the longest path within the loop is found. The time for the longest path is combined with flow information about the loop bound to extract an upper bound for the whole task.

In IPET, program flow and basic-block execution time bounds are combined into sets of arithmetic constraints. The idea was originally proposed in [Li and Malik 1995] and adapted to more complex flows and hardware timing effects in [Puschner and Schedl 1995; Engblom 2002; Theiling 2002a; Theiling 2002b; Ermedahl 2003]. Each basic block and program flow edge in the task is given a time coefficient ( $t_{entity}$ ), expressing

the upper bound of the contribution of that entity to the total execution time every time it is executed and a count variable  $(x_{entity})$ , corresponding to the number of times the entity is executed. An upper bound is determined by maximizing the sum of products of the execution counts and times  $(\sum_{i \in entities} x_i * t_i)$ , where the execution count variables are subject to constraints reflecting the structure of the task and possible flows. The result of an IPET calculation is an upper timing bound and a worst-case count for each execution count variable.

Fig. 5. Bound calculation

Fig. 5(c) shows the constraints and formulae generated by an IPET-based boundcalculation method for the task illustrated in Fig. 5(a). The *start* and *exit constraints* state that the task must be started and exited once. The *structural constraints* reflect the possible program flow, meaning that for a basic block to be executed it must be entered the same number of times as it is exited. The *loop bound* is specified as a constraint on the number of times the loop-head node A can be executed.

IPET is able to handle different types of flow information. It has traditionally been applied in a global fashion treating the whole task and all flow information

together as a unit. IPET-based bound calculation uses integer linear programming (ILP) or constraint programming (CP) techniques, thus having a complexity potentially exponential in the task size. Also, since flow facts are converted to constraints, the size of the resulting constraint system grows with the number of flow facts.

#### 3.5 Symbolic Simulation

Another static method is to simulate the execution of the task in an abstract model of the processor. The simulation is performed without input. The simulator thus has to be capable to deal with partly unknown execution state. This method combines flow analysis, processor-behavior prediction, and bound calculation in one integrated phase [Lundqvist 2002]. One problem with this approach is that analysis time is proportional to the actual execution time of the task. This can lead to a very long analysis since simulation is typically orders of magnitudes slower than native execution.

#### 4. MEASUREMENT-BASED METHODS

These methods attack some parts of the timing-analysis problem by executing the given task on the given hardware or a simulator, for some set of inputs, and measuring the execution time of the task or its parts.

End-to-end measurements of a subset of all possible executions produce estimates or distributions, not bounds for the execution times, if the subset is not guaranteed to contain the worst case. Even one execution would be enough if the worst-case input were known.

Other approaches measure the execution times of code segments, typically of CFG basic blocks. The measured execution times are then combined and analyzed, usually by some form of bound calculation, to produce estimates of the WCET or BCET. Thus, measurement replaces the processor-behaviour analysis used in static methods. Thus, the path-subset problem can be solved in the same way as for the static methods, using control flow analysis to find all possible paths and then using bound calculation to combine the measured times of the code segments into an overall time bound. This solution would include all possible paths, but would still produce unsafe results if the measured basic-block times were unsafe. Another problem is that only a subset of the possible contexts (initial processor states) is used for each measured basic block or other kind of code segment.

The context-subset problem could be attacked by running more tests to measure more contexts or by setting up a worst-case initial state at the start of each measured code segment. The first method (more tests) only decreases, but does not eliminate the risk of unsafe results and is expensive unless intensive testing is already done for other reasons. Exhaustive testing of all execution paths is usually impossible. The second method (use worst-case initial state) would be safe if one could determine a worst-case initial state. However, identifying worst-case initial states is hard or even impossible for complex processors, see below. Measurement-based tools can compute execution-time bounds for processors with simple timing behaviour, but produce only estimates of the BCET and WCET for more complex processors, as long as this problem is not convincingly solved. Other tools collect and analyse multiple measurements to provide a picture of the variability of the execution time

#### Worst-Case Execution Time Problem 17

of the application, in addition to estimates of the BCET and WCET.

There are multiple ways in which measurement can be performed. The simplest approach is by extra instrumentation code that collects a timestamp or CPU cycle counter (available in most processors). Mixed HW/SW instrumentation techniques require external hardware to collect timings of lightweight instrumentation code. Fully transparent (non-intrusive) measurement mechanisms are possible using logic analyzers. Also hardware tracing mechanisms like the NEXUS standard and the ETM tracing mechanism from ARM are non-intrusive, but don't necessarily produce exact timings. For example, NEXUS buffers its output, and time stamps are produced when events leave the buffer, i.e. with a delay. Measurements can also be performed from the output of processor simulators or even VHDL simulators.

The results of measurement-based analysis can be used to provide a picture of the actual variability of the execution time of the application. They can also be used to provide validation for the static analysi approaches. Measurement should also not produce execution times that are far lower than the ones predicted by analytical methods, because this would indicate that the latter are imprecise.

#### 5. COMPARISON OF STATIC AND MEASUREMENT-BASED METHODS

In this section, we attempt to compare the two classes of timing-analysis methods static and measurement-based—to highlight the differences and similarities in their aims, abilities, technical problems and research directions. The next section will describe some timing-analysis tools in more detail to show the state of the practice of both classes of methods.

Static methods compute bounds on the execution time. They use control-flow analysis and bound calculation to cover all possible execution paths. They use abstraction to cover all possible context dependencies in the processor behaviour. The price they pay for this safety is the necessity for processor-specific models of processor behaviour, and possibly imprecise results such as overestimated WCET bounds. In favour of static methods is the fact that the analysis can be done without running the program to be analysed—which often needs complex equipment to simulate the hardware and peripherals of the target system.

Measurement-based methods replace processor behaviour analysis by measurements. Therefore, unless all possible execution paths are measured or the processor is simple enough to let each measurement be started in a worst-case initial state, some context-dependent execution-time changes may be missed and the method is unsafe. For the estimate-calculation step, these methods may use control-flow analysis to include all possible execution paths, or they may simply use the observed execution paths (observed number of loop iterations, for example) which again makes the method unsafe. The advantages claimed for these methods are that they are simpler to apply to new target processors, because they do not need to model processor behaviour, and that they produce WCET and BCET estimates that are more precise—closer to the exact WCET and BCET—than the bounds from static methods, especially for complex processors and complex applications.

Still, since the exact WCET or BCET is usually not known, there is really no way to check how precise an estimate or bound is. Studies of precision often compare the estimates or bounds not to the exact WCET or BCET but to the extreme

observed times from a large but not exhaustive set of tests.

Users can help to improve precision for both classes of methods. For the static methods, users can improve the precision (tighten the bounds) by annotations that exclude infeasible executions from the analysis. For the measurement-based methods, users can improve the precision by adding test cases to include more possible executions in the measurements. Some measurement-based tools also allow annotations for the estimate calculation to exclude infeasible executions or to include more executions by defining larger loop bounds than have been observed.

Both classes of methods share some technical problems and solutions. The frontends are similar when both use executable code as input; control-flow analysis is similar; and bound/estimate calculation can be similar. For example, the IPET calculation is used by some static tools and by some measurement-based tools.

The main technical problem for static methods is modelling processor behaviour. This is not a problem for most measurement-based methods, where the main problem is to measure the execution time accurately, with fine granularity, and without perturbing the program being measured. The solution is often processor- or platform-specific, but implementing a measurement method for a new processor is usually less work than creating an abstract model of the processor behaviour.

The handling of timing anomalies offers an interesting comparison of the methods. For measurement-based methods, timing anomalies make it very hard to find a worst-case initial state for a measurement. To be safe, the measurement should now be done from all possible initial states, which is impractical. Measurementbased methods then use only a subset of initial states and so are not safe.

Static methods based on abstract interpretation have ways to express the absence of information and can therefore analyse large state sets, including all possible states for a safe analysis. Here, timing anomalies make it hard to define state abstractions that give a precise abstract interpretation of each instruction and of the execution time spent in the instruction—the processor behaviour tends to depend on unknown aspects of the state, forcing the abstract simulation to follow many possible executions of each basic block. Still, this laborious exploration is limited to basic blocks, because the abstract simulation considers the global flow of the task for the processor-behavior analysis by propagating simulation results between basic blocks. Thus, no worst case assumptions need to be made by the analysis on the basic block level.

Current research in these methods addresses some shared problems, while each class of methods also has its own research directions. Clearly, research into improved abstract processor models is relevant only to static methods, while the development of better measurement methods—in particular, standard interfaces for measurement for many processor types—is of interest mainly for the measurement-based methods.

Control-flow analysis, on the other hand, is a common subject of research that applies to both static methods and measurement-based meethods. Another common subject is the separation of contexts to improve the precision of the analysis. This means that a given part of the task under analysis, for example a subroutine or a loop body, can be analysed or measured separately depending on its context, for example the call-path to the subroutine, or the ieration number of the loop. Here,

the question that is common to static methods and measurement-based methods is when to separate between contexts and how—automatically or by manual annotations.

# 6. COMMERCIAL WCET TOOLS AND RESEARCH PROTOTYPES

The tool providers and researchers participating in this survey have received the following list of questions:

- —What is the functionality of your tool?

- —What methods are employed in your tool?

- —What are the limitations of your tool?

- —Which hardware platforms does your tool support?

This section has the following line-up of tools, from completely static tools such as aiT in Subsection 6.1, Bound-T in Subsection 6.2, and the prototypes of Florida (Subsection 6.3), Vienna (Subsection 6.4), Singapore (Subsection 6.5), and IRISA (Subsection 6.6), through mostly static tool with a small rudiment of measurement in SWEET (very controlled pipeline measurements on a simulator), in Subsection 6.7, and the Chalmers prototype (Subsection 6.8), through SymTA/P (cache analysis and block/segment measurement starting from a controlled cache state and bound calculation), in Subsection 6.9, to the most measurement-based tool, RapiTime (block measurement from an uncontrolled initial state and bound calculation), in Subsection 6.10.

### 6.1 The aiT Tool of AbsInt Angewandte Informatik, Saarbrücken, Germany

Functionality of the Tool. The purpose of AbsInt's timing-analysis tool aiT is to obtain upper bounds for the execution times of code snippets (e.g. given as subroutines) in executables. These code snippets may be tasks called by a scheduler in some real-time application, where each task has a specified deadline. aiT works on executables because the source code does not contain information on register usage and on instruction and data addresses. Such addresses are important for cache analysis and the timing of memory accesses in case there are several memory areas with different timing behavior.

Apart from the executable, aiT might need user input to be able to compute a result or to improve the precision of the result. User annotations may be written into parameter files and refer to program points by absolute addresses, addresses relative to routine entries, or structural descriptions (like the first loop in a routine). Alternatively, they can be embedded into the source code as special comments. In that case, they are mapped to binary addresses using the line information in the executable.

Apart from the usual user annotations (loop bounds, flow facts), aiT supports annotations specifying the values of registers and variables. The latter is useful for analyzing software running in several different modes that are distinguished by the value of a mode variable.

The aiT versions for all supported processors share a common architecture as shown in Fig. 6:

Fig. 6. Architecture of the aiT WCET analysis tool

- —First, the control flow is reconstructed from the given object code by a bottom up approach. The reconstructed control flow is annotated with the information needed by subsequent analyses and then translated into CRL (Control Flow Representation Language, a human-readable intermediate format designed to simplify analysis and optimization at the executable/assembly level). This annotated control-flow graph serves as the input for the following analysis steps.

- -Next, value analysis computes ranges for the values in the processor registers at every program point. Its results are used for loop bound analysis, for the detection of infeasible paths depending on static data, and to determine possible addresses of indirect memory accesses. An extreme case of control depending on static data is a virtual machine program interpreting abstract code given as data. [Souyris et al. 2005] report on a successful analysis of such an abstract machine.

- —aiT's cache analysis relies on the addresses of memory accesses as found by value analysis and classifies memory references as sure hits and potential misses. It is based upon [Ferdinand and Wilhelm 1999], which handles LRU caches, but had to be modified to reflect the non-LRU replacement strategies of common microprocessors: the pseudo-round-robin replacement policy of the ColdFire MCF 5307, and the PLRU (Pseudo-LRU) strategy of the PowerPC MPC 750 and 755. The deviation from perfect LRU is the reason for the reduced predictability of the cache contents in case of these two processors compared to processors with

perfect LRU caches [Heckmann et al. 2003].

- -Pipeline analysis predicts the behavior of the task on the processor pipeline. The result is an upper bound for the execution time of each basic block in each distinguished execution context.

- —Finally, bound calculation (called path analysis in the aiT framework) determines a worst-case execution path of the task from the timing information for the basic blocks.

*Employed Methods.* The structuring of the whole task of determining upper bounds into several phases allows different methods tailored to the subtasks to be used. In aiT's case, value analysis and cache/pipeline analysis are realized by abstract interpretation, a semantics-based method for static program analysis [Ferdinand and Wilhelm 1999; Ferdinand et al. 2001; Langenbach et al. 2002]. Path analysis is implemented by integer linear programming. Reconstruction of the control flow is performed by a bottom-up analysis [Theiling et al. 2000]. Detailed information about the upper bounds, the path on which it was computed, and the possible cache and pipeline states at any program point are attached to the call graph / control-flow graph and can be visualized in AbsInt's graph browser aiSee.

Limitations of the Tool. aiT includes automatic analysis to determine the targets of indirect calls and branches and to determine upper bounds of the iterations of loops. These analyses do not work in all cases. If they fail, the user has to provide annotations.

aiT relies on the standard calling convention. If some code doesn't adhere to the calling convention, the user might need to supply additional annotations describing control flow properties of the task.

Supported Hardware Platforms. Versions of aiT exist for the Motorola PowerPC MPC 555, 565, and 755, Motorola ColdFire MCF 5307, ARM7 TDMI, HCS12/STAR12, TMS320C33, C166/ST10, Renesas M32C/85 (prototype), and Infineon TriCore 1.3.

#### 6.2 The Bound-T Tool of Tidorum, Helsinki, Finland

The Bound-T tool was originally developed at Space Systems Finland Ltd under contract with the European Space Agency (ESA) and intended for the verification of on-board software in spacecraft. Tidorum Ltd is extending Bound-T to other application domains.

*Functionality of the Tool.* The tool determines an upper bound on the execution time of a subroutine, including called functions. Optionally, the tool can also determine an upper bound on the stack usage of the subroutine, including called functions.

The input is a binary executable program with (usually) an embedded symbol table (debug information). The tool is able to compute upper bounds on some counter-based loops. For other loops the user provides annotations, called *assertions* in Bound-T. Annotations can also be given for variable values to support the automatic loop-bounding.

The output is a text file listing the upper bounds etc. and graph files showing callgraphs and control-flow graphs for display with the DOT tool [Gansner and North 2000].

As a further option, when the task under analysis follows the ESA-specified HRT ("Hard Real Time") tasking architecture, Bound-T can generate the HRT Execution Skeleton File that contains both the tasking structure and the computed bounds and can be fed directly into the ESA-developed tools for Schedulability Analysis and Scheduling Simulation.

*Employed Methods.* Reading and decoding instructions is hand-coded based on processor manuals. The processor model is also manually constructed for each processor. Bound-T has general facilities for modelling control flow and integer arithmetic, but not for modelling complex processor states. Some special-purpose static analyses have been implemented, for example for the SPARC register-file overflow and underflow traps and for the concurrent operation of the SPARC Integer Unit and Floating Point Unit. Both examples use (simple) abstract interpretation followed by ILP.

The control-flow graph (CFG) is often defined to model the processor's instructionsequencing behaviour, not just the values of the program counter. A CFG node typically represents a certain pipeline state, so the CFG is really a pipeline-state graph. Instruction interactions (e.g. data-path blocking) are modelled in the time assigned to CFG edges.

Counter-based loops are bounded by modelling the task's loop-counter arithmetic as follows. The computational effect of each instruction is modelled as a relation between the "before" and "after" values of the variables (registers and other storage locations). The relation is expressed in Presburger Arithmetic as a set of affine (linear plus constant term) equations and inequalities, possibly conditional. Instruction sequences are modelled by concatenating (joining) the relations of individual instructions. Branching control-flow is modelled by adding the branch condition to the relation. Merging control-flow is modelled by taking the union of the inflowing relations.

Loops are modelled by analysing the model of the loop-body to classify variables as loop-invariant or loop-variant. The whole loop (including an unknown number of repetitions) is modelled as a relation that keeps the loop-invariant variables unchanged and assigns unknown values to the loop-variant variables. This is a first approximation that may be improved later in the analysis when the number of loop iterations is bounded. With this approximation, the computations in an entire subprogram can be modelled in one pass (without fixpoint iteration).

To bound loop iterations, Bound-T first re-analyses the model of the loop body in more detail to find loop-counter variables. A loop counter is a loop-variant variable such that one execution of the loop body changes the variable by an amount that is bounded to a finite interval that does not contain zero. If Bound-T also finds bounds on the initial and final values of the variable, a simple computation gives a bound on the number of loop iterations.

Bound-T uses the Omega Calculator from Maryland University [Pugh 1991] to create and analyze the equation set. Loop-bounds can be context-dependent if they depend on scalar pass-by-value parameters for which actual values are provided at the top (caller end) of a call-path.

The worst-case path and the upper bound for one subroutine are found by the Implicit Path Enumeration Technique, (see Section 3.4) applied to the control-flow graph of the subroutine. The lp\_solve tool is used [Berkelaar 1997]. If the subroutine has context-dependent loop bounds, the IPET solution is computed separately for each context (call path).

Annotations are written in a separate text file, not embedded in source-code. The program element to which an annotation refers is identified by a symbolic name (subroutine, variable) or by structural properties (loops, calls). The structural properties include nesting of loops, location of calls with respect to loops, and location of variable reads and writes.

Limitations of the Tool. The task to be analyzed must not be recursive. The control-flow graphs must be reducible. Dynamic (indexed) calls are only analyzed in special cases, when Bound-T's data-flow analysis finds a unique target address. Dynamic (indexed) jumps are analyzed based on the code patterns that the supported compilers generate for switch/case structures, but not all such structures are supported.

Bound-T can detect some infeasible paths as a side-effect of its loop-bound analysis. There is, however, no systematic search for such paths. Points-to analysis (aliasing analysis) is weak, which is a risk for the correctness of the loop-bound analysis.

The bounds of an inner loop cannot depend on the index of the outer loop(s). For such "non-rectangular" loops Bound-T can often produce a "rectangular" upper bound. Loop-bound analysis does not cover the operations of multiplication (except by a constant), division or the logical bit-wise operations (and, or, shift, rotate).

The task to be analyzed must use the standard calling conventions. Furthermore, function pointers are not supported in general, although some special cases such as statically assigned interrupt vectors can be analyzed.

No cache analysis is yet implemented (the current target processors have no cache or very small and special caches). Any timing anomalies in the target processor must be taken into account in the execution time that is assigned to each basic block in the CFG. However, the currently supported, cacheless processors probably have no timing anomalies. As Bound-T has no general formalism (beyond the CFG) for modelling processor state, it has no general limitations in that regard, but models for complex processors would be correspondingly harder to implement in Bound-T.

Supported Hardware Platforms. Intel-8051 series (MCS-51), Analog Devices ADSP-21020, ATMEL ERC32 (SPARC V7), Renesas H8/300, ARM7 (prototype) and ATMEL AVR and ATmega (prototypes).

#### Research Prototype from Florida State University, North Carolina State University, 6.3 Furman University

The main application areas for our timing analysis tools are hard real-time systems and energy-aware embedded systems with timing constraints. We are currently working on using our timing analyzer to provide QoS for soft real-time systems.

Functionality of the Tool. The toolset performs timing analysis of a single task or a subroutine.

A user interacts with the timing analyzer in the following manner. First, the user compiles all of the files that comprise the task. The compiler was modified to produce information used by the timing analyzer, which includes number of loop iterations, control flow, and instruction characteristics. The number of iterations for simple and non-rectangular loop nests are supported. The timing analyzer produces lower bounds and upper bounds for each function and loop in the task. This entire process is automatic.

*Employed Methods.* The tool uses data-flow analysis for cache analysis to make caching categorizations for each instruction [Arnold et al. 1994]. It supports directmapped and set-associative caches [Mueller 2000]. Control-flow analysis is used to distinguish paths at each loop and function level in the task [Arnold et al. 1994]. The pipeline is simulated to obtain the upper bound of each path, caching categorizations are used during this time so that pipeline stalls and cache-miss delays can be properly integrated [Healy et al. 1995]. The loop analysis iteratively finds the worst-case path until the caching behavior reaches a fixed point that is guaranteed to remain the same [Arnold et al. 1994; Mueller 2000]. Loop bounds analysis is performed in the compiler to obtain the number of iterations for each loop. The timing analyzer is also able to address non-rectangular loop nests, which is modeled in terms of summations [Healy et al. 2000]. Parametric timing analysis support is also provided for run-time bound loops by producing a bounds formula parameterized on loop bounds rather than cycles [Vivancos et al. 2001]. Branch constraint analysis is used to tighten the predictions by disregarding paths that are infeasible [Healy and Whalley 2002]. A timing tree is used to evaluate the task in a bottom-up fashion. Functions are distinguished into instances so that caching categorizations for each instance can be separately evaluated [Arnold et al. 1994].

Limitations of the Tool. Loop bounds for numeric timing analysis are required to be statically known, or there has to be a known loop bound in the outer loop in a non-rectangular loop nest. Loop bounds need not be statically known when using parametric timing analysis support. Like most other timing analysis tools, no support is provided for pointer analysis or dynamic allocation. No calls through pointers are allowed since the call graph must be explicit to analyze the task. We also do not allow recursion since we do not currently provide any support to automatically determine the maximum number of recursive calls that can be made in a cyclic call graph. We provide limited data cache support wrt. access patterns [White et al. 1999]. We also provide limited support for data cache analysis for array accesses in loop nests using cache miss equations [Ramaprasad and Mueller 2005]. The timing analyzer is only able to determine execution-time bounds of applications on simple RISC/CISC architectures. The tool has limited scalability in terms of analyzing small codes in seconds, medium-sized codes in minutes. But entire systems may take hours/days, which we do not deem feasible. Scalability depends on the system/target device and is less of a problem with 8-bit systems, but a more significant problem with 32-bit systems.

Supported Hardware Platforms. The hardware platforms include a variety of uniprocessors (multiprocessors should be handled in schedulability analysis). These ACM Transactions on Programming Languages and Systems, Vol. V, No. N, Month 20YY.

include the MicroSPARC I, Intel Pentium, StarCore SC100, PISA/MIPS, and Atmel Atmega [Anantaraman et al. 2003; Mohan et al. 2005]. Experiments have been performed with the Force MicroSPARC I VME board. The timing analyzer WCET predictions have been validated on the Atmel Atmega to cycle-level accuracy [Mohan et al. 2005].

#### 6.4 Research Prototypes of TU Vienna

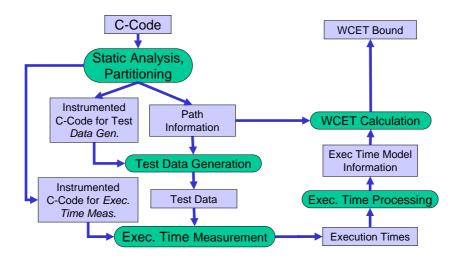

The TU Vienna real-time group has developed a number of tool prototypes for experimenting with different approaches to execution-time analysis. Three of these are presented in this paper: The first is a prototype tool for *static timing analysis* that has been integrated into a Matlab/Simulink tool chain and can analyze C code or Matlab/Simulink models. Second we present a *measurement-based tool* that uses genetic algorithms to direct input-data generation for timing measurements in the search for the worst case or long program execution times. The third tool is a *hybrid tool* for timing analysis that uses both measurements and elements from static analysis to assess the timing of C code.

#### 6.4.1 TU Vienna Research Prototype for Static Analysis.

Functionality of the Tool. The timing analysis for C programs performs timing analysis for software coded in WCETC, where WCETC is a subset of C with extensions that allow users or tool components for flow analysis to make annotations about (in)feasible execution paths [Kirner 2002]. The tool cooperates with a C compiler. The compiler translates the WCETC code into object code and some information for the WCET analyzer. This object code is then analyzed to compute an upper bound. Back annotation of bound information for single statements, entire functions, and tasks are possible.

A component of the static tool has been built into the Matlab/Simulink tool chain. This component generates code from the block set that includes all path annotations necessary for timing analysis, i.e., there is no need to perform any additional flow analysis or annotate the code. In that way the tool supports fully automatic timing analysis for the complete Matlab/Simulink block set defined within the European IST project SETTA, see [Kirner et al. 2002]. In addition, the tool supports back annotation of detailed execution-time information for individual Matlab/Simulink blocks and entire Matlab/Simulink application models.

*Employed Methods.* A number of adaptations had been made to the Matlab/Simulink tool chain. First, the code-generation templates used by the target language compiler (TLC) were modified. The templates for our block set were changed so that TLC generates Code with WCETC macros instead of pure C code. Second, a GNU C compiler was adapted to translate WCETC code and cooperate with the WCET analyzer. The modified C compiler uses abstract co-interpretation of path information during code translation in order to trace changes in the control structure as made by code optimization. This co-transformation of path information is the key to keeping path information consistent in optimizing compilers, thus facilitating timing analysis of highly optimized code [Kirner and Puschner 2003; Kirner 2003]. It computes execution-time bounds for the generated code by means of integer linear programming adding information about infeasible execution paths [Puschner and Schedl 1997].

Back annotation of timing-analysis results to the Matlab/Simulink specification level is done via dedicated WCET blocks that represent time bounds for blocks and entire tasks.

Limitations of the Tool. If used together with the SETTA Matlab/Simulink block set, the static WCET tool provides a fully automated timing analysis, i.e., there is no need for annotations or help from the user to calculate execution-time bounds. So there are no limitations besides the fact that the programmer must only use blocks from the block set.

In case the tool is to be used to analyze C code it may be necessary to annotate the code with information about (in)feasible paths (either by using a flow-annotation tool or by providing manual annotations). In the latter case the quality of the computed bounds strongly depends on the quality of the annotations.

Supported Hardware Platforms. M68000, M68360, and C167.

6.4.2 TU Vienna Research Prototype for Measurement-based Analysis.

*Functionality of the Tool.* The measurement-based tool for dynamic executiontime analysis yields optimistic approximations to the worst-case execution times of a piece of code.

*Employed Methods.* Genetic algorithms are used to generate input data for execution-time measurements [Puschner and Nossal 1998] as follows: At the beginning, the task or program under observation is run with a number of random inputdata sets. For each of the input data sets the execution time is measured and stored. The execution-time values are then used as fitness values for their respective input data sets (i.e., longer execution times imply higher fitness). The fitness values, in turn, form the basis for the generation of a new population of input-data sets by the genetic algorithms. The GA-based input-data generation strategy is repeated until the termination criterion as specified for the analysis is reached [Atanassov et al. 1999].

*Limitations of the Tool.* GA-based bounds search can in general not guarantee to produce safe results, as measurement-based techniques approach the upper bound from the side of lower execution times.

Supported Hardware Platforms. The targets supported include the C167, and PowerPC processors.

6.4.3 TU Vienna Research Prototype for Hybrid Analysis.