Year 4 D2-Mgt-Y4

Executive Summary

IST-004527 ARTIST2 Network of Excellence on Embedded Systems Design

# Periodic Activity Report for Year 4

Executive Summary

Joseph Sifakis – Artist2 Scientific Coordinator Bruno Bouyssounouse – Artist2 Technical Coordinator

Artist2 Consortium

## 1. Project Objectives

These objectives have remained in place since the start of the Artist2 NoE.

The strategic objective of the ARTIST2 Network of Excellence is to strengthen European research in Embedded Systems Design, and promote the emergence of this new multidisciplinary area. We gather together the best European teams from the composing disciplines, and will work to forge a scientific community. Integration will be achieved around a Joint Programme of Activities, aiming to create critical mass from the selected European teams.

The ARTIST2 Network of Excellence on Embedded Systems Design implements an international and interdisciplinary fusion of effort to create a unique European virtual centre of excellence on Embedded Systems Design. This interdisciplinary effort in research is mandatory to establish Embedded Systems Design as a discipline, combining competencies from electrical engineering, computer science, applied mathematics, and control theory. The ambition is to compete on the same level as equivalent centres in the USA (Berkeley, Stanford, MIT, Carnegie Mellon), for both the production and transfer of knowledge and competencies, and for the impact on industrial innovation.

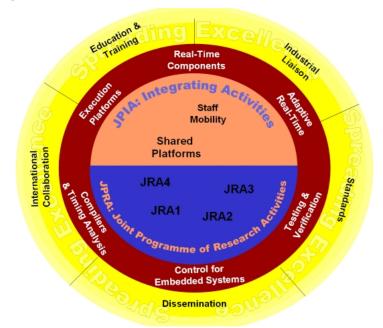

ARTIST2 has a double core, consisting of leading-edge research in embedded systems design issues (described later in this document) in the Joint Programme of Research Activities (JPRA), and complementary activities around shared platforms and staff mobility in the Joint Programme of Integration Activities (JPIA).

Building the embedded systems design scientific community is an ambitious programme. To succeed, ARTIST2 builds on the achievements and experience from the ARTIST1 FP5 Accompanying Measure on Advanced Real-Time Systems. ARTIST1 provided the opportunity to test the concept of a two-level integration (within and between clusters) – four clusters in ARTIST2 originated as "actions" in ARTIST1. Building the ARTIST2 consortium and associated structure is the culmination of discussions and ambitions elaborated within ARTIST1.

ARTIST2 addresses the full range of challenges related to Embedded Systems Design, covering all aspects, ranging from theory through to applications.

#### Year 4 D2-Mgt-Y4 Executive Summary

## 2. Contact Details and Contractors Involved

## 2.1 Core Partners

For a complete description including web links, see: <u>http://www.artist-embedded.org/artist/-Core-Partners-.html</u>

| Scientific Coordinator: | Technical Coordinator:      |  |

|-------------------------|-----------------------------|--|

| Joseph Sifakis          | Bruno Bouyssounouse         |  |

| Tel: +33 4 56 52 03 51  | Tel: +33 4 56 52 03 68      |  |

| Joseph.Sifakis@imag.fr  | Bruno.Bouyssounouse@imag.fr |  |

Mailing address: Verimag Laboratory - Centre Equation - 2, ave de Vignate - 38610 Gières - France

| Partic<br>N° | Participant name                                                    | Country     | Partic<br>N° | Participant name                      | Country         |

|--------------|---------------------------------------------------------------------|-------------|--------------|---------------------------------------|-----------------|

| 1            | Caisse des Dépots et<br>Consignations                               | France      | 21           | Kuratorium OFFIS e. V.                | Germany         |

| 2            | UJF / Verimag                                                       | France      | 22           | PARADES                               | Italy           |

| 3            | RWTH Aachen                                                         | Germany     | 24           | Universidad Politecnica de Madrid     | Spain           |

| 4            | BRICS – Aalborg University                                          | Denmark     | 25           | Saarland University                   | Germany         |

| 5            | AbsInt GmbH                                                         | Germany     | 27           | TU of Eindhoven                       | Netherland<br>s |

| 6            | University of Aveiro                                                | Portugal    | 28           | TU of Vienna                          | Austria         |

| 7            | Universidad de Cantabria                                            | Spain       | 29           | TU Braunschweig                       | Germany         |

| 8            | Commissariat à l'Énergie<br>Atomique – Laboratoire LIST             | France      | 30           | University of Twente                  | Netherland<br>s |

| 9            | CFV, Université de Liège                                            | Belgium     | 31           | University of Bologna                 | Italy           |

| 10           | Czech Technical University                                          | Czech Rep.  | 32           | Uppsala University                    | Sweden          |

| 11           | Dortmund University                                                 | Germany     | 33           | Universidad Polytechnical de Valencia | Spain           |

| 12           | Technical University<br>of Denmark                                  | Denmark     | 34           | University of York                    | UK              |

| 13           | Swiss Federal Institute of<br>Technology – Zurich                   | Switzerland | 35           | Polytechnic Institute of<br>Porto     | Portugal        |

| 14           | France Telecom R&D                                                  | France      | 36           | EPFL                                  | Switzerlan<br>d |

| 15           | Institut National de<br>Recherche en Informatique<br>et Automatique | France      | 37           | Scuola Sant'Anna – Pisa               | Italy           |

| 16           | Royal Institute of<br>Technology (KTH)                              | Sweden      | 38           | Ace                                   | Netherland      |

| 17           | Linköping University                                                | Sweden      | 39           | Tidorum                               | Finland         |

| 18           | CNRS / Laboratoire LSV                                              | France      | 40           | TU Kaiserslautern                     | Germany         |

| 19           | Lund University (Sweden)                                            | Sweden      | 41           | TU Berlin                             | Germany         |

| 20           | University of Mälardalen                                            | Sweden      |              |                                       |                 |

The following partners have withdrawn from the NoE:

- Partner 23 University of Pavia (Italy)

- Partner 26 ST Microelectronics, Central R&D (France)

## 2.2 Affiliated Partners

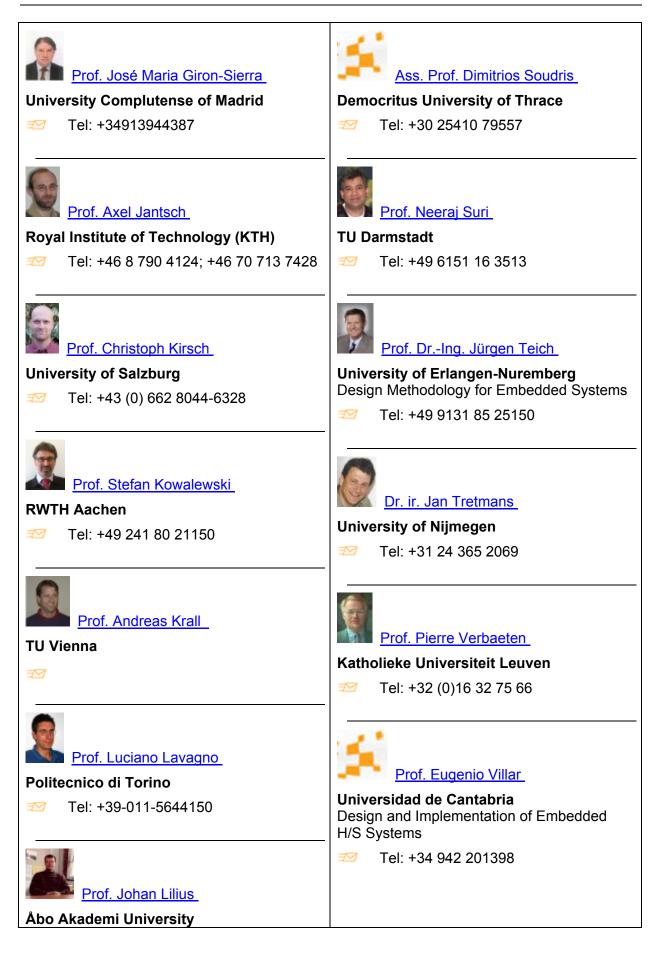

Affiliated partners play a very strong role in the Spreading Excellence from the core partners to the research and industrial communities at large.

Affiliated partners generally play an active role in the research activities, either participating directly in research, or transferring the results directly to industry.

Each of the JPRA and JPIA activities' deliverables provides the list of the corresponding affiliated partners and roles.

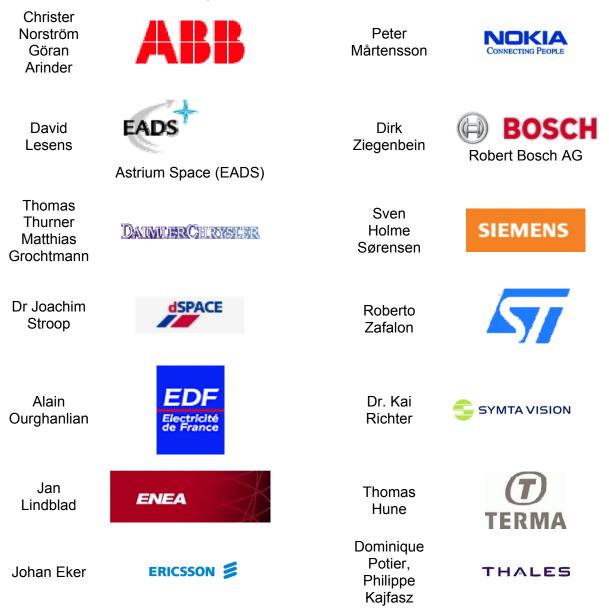

#### Affiliated Industrial Partners

The complete set of Affiliated Industrial partners, including web links, is available online, here: <u>http://www.artist-embedded.org/artist/-Affiliated-Industrial-Partners-.html</u>

|                        | RTIST2 ARTIST2 NoE<br>Activity Report<br>Executiv | Year 4<br>D2-Mgt-Y4<br>e Summary | Information Society<br>Technologies |

|------------------------|---------------------------------------------------|----------------------------------|-------------------------------------|

| Philippe<br>Baufreton  | Groupe SAFRAN                                     | Fabian<br>Wolf                   |                                     |

| Vladimir<br>Havlena    | Honeywell                                         | Magnus<br>Hellring               | VOLVO                               |

| Dr. Michael<br>Winokur |                                                   | Magnus<br>Hellring               | VOLVO                               |

| Dr. Matthias<br>Gries  | (intel)                                           | Jakob<br>Axelsson                | <b>VOLVO</b><br>for life            |

|                        | Intel Gmbh                                        |                                  |                                     |

|                        |                                                   |                                  |                                     |

Peter Mårtensson

**Affiliated SME Partners** Idence Paolo Gai Alan Moore Dr. Monica BullDAST Donno Carl von Platen STEN Joachim António dSPACE LIFTECH LIFT TECHNOLOGIES Stroop Garrido Fernando Jan Lindblad Santos ENEA Aicro I/O **Bernard Dion** ESTEREL S

Executive Summary

### Affiliated Academic Partners

| LIAFA - Université Paris 7 & CNRS UMR Univer | Prof. Lucia Lo Bello<br>sity of Catania<br>Tel: +39 095 7382386 |

|----------------------------------------------|-----------------------------------------------------------------|

| Dr. Frédéric Boulanger Prof. D               | r. Miroslaw Malek_                                              |

| Faala aumériaura diéla stricité (Qumélas)    | oldt University Berlin                                          |

| Computer Science Department                  | Tel: +49 30 2093 3027                                           |

| ✓ Tel: +33 1 69 85 14 84                     |                                                                 |

|                                              | <u>Dr. Pau Martí Colom</u>                                      |

|                                              | sitat Politècnica de Catalunya                                  |

| Prof. Lubos Brim                             | Геl: +34 93 401 1679                                            |

| Masaryk University Brno                      |                                                                 |

| Tel: +420 549 493 647                        |                                                                 |

| 10                                           | <u>Dr. Fabio Martinelli</u>                                     |

| WK-A                                         | o di Informatica e Telematica                                   |

| Prof. Dr. Dr. h.c. Manfred Broy Nation       | al Research Council C.N.R.                                      |

| TU München 🏾 🖅 -                             | Tel: +39.050.315.3425                                           |

| 至 Tel: +49 89 289-17304                      |                                                                 |

|                                              | Dr. Marius Minea                                                |

| Ass. Prof. Salvatore Carta Timiso            | ara - Institute e-Austria Timisoara                             |

| Università degli Studi di Cagliari 🛛 🚽 -     | Tel: +40-256-403284                                             |

| ✓ Tel: +39 070-675-8780                      |                                                                 |

| Dr. Francky Catthoor ENST                    | Associate Prof. Laurent Pautet                                  |

|                                              | Tel: +33 1-45-81-73-22                                          |

| <sup>™</sup> Tel: +32 16 281202              | 101. 100 1- <del>1</del> 0-01-10-22                             |

|                                              |                                                                 |

| 12                                                                                                                                   | Julián Proenza                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Prof. Geert Deconinck                                                                                                                | University of the Balearic Islands                                                                                                                                               |

| Katholieke Universiteit Leuven                                                                                                       | 📨 Tel: (+34) 971 17 29 92                                                                                                                                                        |

| ✓ Tel: +32 16 32.11.26                                                                                                               |                                                                                                                                                                                  |

| Prof. Giovanni DeMicheli EPFL Lausanne ∞ Tel: (+41 21) 693-0911                                                                      | IRISA         ∞       Tel: +33 02 99 84 73 10                                                                                                                                    |

| <ul> <li>Prof. Ivo De Lotto</li> <li>Università degli studi di Pavia</li> <li>Team leader</li> <li>Tel: +39 0382 98 53 57</li> </ul> | Michael Rusinowitch<br>INRIA<br>Formal methods on embedded systems – in<br>particular on verification of security<br>properties.<br>Tel: +33 03 83 59 30 20                      |

| Prof. Dr. Ed Deprettere         Leiden University         ✓       Tel: +31 (0)71 5275776         Prof. Luca Fanucci                  | <ul> <li>Prof. Pablo Pedro Sanchez</li> <li>Universidad de Cantabria</li> <li>Design and Implementation of Embedded</li> <li>H/S Systems</li> <li>Tel: +34 942 201548</li> </ul> |

| University of Pisa                                                                                                                   | Dr. Markus Schordan<br>TU Vienna                                                                                                                                                 |

| <ul> <li>Prof. Dr. Marisol Garcia-Valls_</li> <li>Universidad Carlos III de Madrid</li> <li>✓ Tel: +34 91-624-8783</li> </ul>        | <ul> <li>Prof. Donatella Sciuto</li> <li>Politecnico di Milano</li> <li>Tel: +39-02-2399 3662</li> </ul>                                                                         |

Year 4 D2-Mgt-Y4 Executive Summary

Year 4 D2-Mgt-Y4 **Executive Summary**

3M Tel: +358-40-544 0741

#### Affiliated International Collaboration Partners

Prof. Tarek Abdelzaher

University of Illinos at Urbana-Champaign Technical expert

Tel: +1 217 265-6793

Prof. Zhou Chaochen

**Chinese Academy of Sciences**

Prof. Giovanni De Micheli

#### **EPF** Lausanne

Tel: +41 21 693-0911

Assoc. Prof. Stephen A. Edwards

#### **Columbia University**

Tel: +1 212 939 7019

#### Prof. Sharon Hu

University of Notre Dame - Indiana USA Design for Low Power

Tel: +1 574 631-6015

### Shankar Sastry

#### **Berkeley University**

Z Tel: +1 (510) 643-2200

#### Prof. Heinz Schmidt

Monash University (Australia)

3M Tel: +61 3 9905-2479

## Prof. Lui Sha

University of Illinos at Urbana-Champaign Technical expert.

Tel: +1 244-1887

#### Assoc. Prof. Mircea R. Stan

#### University of Virginia

Power and thermal modeling at the device, circuit and system level. Self-consistent power modeling by taking into account thermal effects. Temperature-aware circuit design. Automotive computing applications. Participates in the activity on Design for Low Power.

Tel: +1 434 924 3503 ME

Year 4 D2-Mgt-Y4

**Executive Summary**

#### Prof. Mathai Joseph

Tata Research Development & Design Centre (TRDDC)

#### UC Berkeley

Prof. Xiaojian Liu

UNU-IIST Macau

Co-organiser of the <u>Artist2 / UNU-IIST</u> <u>School in China - 2007</u>

📨 Tel: +853 712930

#### Prof. Kang Shin

#### University of Michigan

📨 🛛 Tel: +1 (734) 763-0391

# Prof. John Stankovic

### University of Virginia

📨 Tel: +1 (434) 982-2275

Prof. Janos Sztipanovits

Vanderbilt University USA

7 Tel: +1 615-343-7572

Prof. P.S. Thiagarajan

#### **National University of Singapore**

Tel: (65) 6516 7998

## 3. Vision and Assessment of the Work Performed

Artist2 has financed durable integration between teams and not the concrete elements of the JPA which most often belong to other projects. These specific technical objectives may or may not be attained (this is the essence of research as opposed to development), but we feel that the main product of Artist2 is the emergence of a lasting European research community, that has a significantly enhanced capacity for preparing Europe's future.

The research is completed by work on the JPIA Platforms, which aim to transform research results in tangible tools and components.

We believe that the topics chosen provide a good coverage of the area, for embedded software and systems.

The ARTIST2 NoE is a complex construction assembled from world-leading communities, teams, and individuals. This is certainly an asset, but also a source of complexity in management. Each team has two essential characteristics: world-class excellence and strong interaction with top industrial players. Artist2 partners play a leading role in the different communities in embedded systems design, and they advance the state of the art in each of these.

Over the course of Years 1-4, Artist2 has been extremely active in submitting new proposals

It is difficult to abstract out a global synthesis of the overall technical achievements. This is due to the diversity and the low granularity of the actions to be covered (meetings, publications, attendance at workshops, visits, and platforms).

The following is a certainly non-exhaustive assessment of the work in the Joint Programme of Activities' 4 main branches.

## **3.1** Joint Programme of Research Activities (JPRA)

#### 3.1.1 Structure of the Research Effort

This is unchanged with respect to the end of Year 3 – included here as a useful introduction.

The JPRA is composed of intra and inter-cluster research activities on cutting-edge topics in embedded systems design. While the main bulk of financing for these activities is taken up by outside programmes (Integrated Projects, National Programmes, Industrial Contracts, etc), the Artist2 NoE finances the extra burden due derived from integrating these into a single coherent research programme.

Thus, the essential ingredient within Artist2 is the JPRA, which motivates the participating research teams far more than the actual financing, which is tiny in comparison with the overall research aims. It is completed by the Joint Programme of Integrating Activities (JPIA), and the Joint Programme of Activities for Spreading Excellence (JPASE), and overseen by the Joint Programme of Management Activities (JPMA).

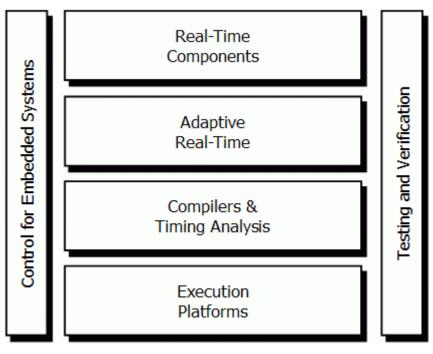

The structure of the research activities reflects the following decomposition of the embedded systems design flow.

This design flow is composed of the following cooperating activities, starting with componentbased modelling and leading to implementation. These activities must be well coordinated, and supported by tools and methods to ensure satisfactory levels of productivity and quality. Accordingly, we have structured the area of embedded systems design into the following topics.

Executive Summary

<u>Real-Time Components</u>: The development of a general framework for component-based engineering of complex heterogeneous embedded systems is a grand challenge which spans many research problems. A key characteristic of component-based embedded systems is heterogeneity of component models. This heterogeneity concerns different execution models (synchronous, asynchronous, vs. timed), communication models (synchronous vs. asynchronous), as well as different scheduling paradigms. Technology must be provided to allow designing heterogeneous embedded systems from diverse types of components, and allow predicting and optimizing functional and non-functional properties of the designed systems.

<u>Adaptive Real-time</u>: This is a more recent approach to embedded systems design, where temporal constraints can be relaxed, which allows optimized use of resources. This includes applications – where managing the Quality of Service (QoS) is essential, such as telecommunication systems, multi-media, and wide-area networked applications. In this relatively new area, there is a recognized lack of design theory and tools.

<u>Compilers and Timing Analysis</u>: Once the application software has been developed, using the above, the system must be implemented on a given target platform. Compilation tools and their associated technologies play a fundamental role for automating this process. For the implementation of embedded systems, we need tools capable of combining platform independent software and a description of the target platform, to generate an executable code having the desired properties related to use of such resources as memory, power, energy, network bandwidth, and computation time). Resource-aware compilation requires the use of Timing Analysis tools to estimate the execution times of embedded software on a given platform.

<u>Execution Platforms</u>: This topic is strongly linked to the compilation and implementation of embedded systems. For a given application, it is important to have the technology, methods and tools to make rational choices about the platform and the design used, before proceeding to final implementation. Research in Execution Platforms targets the development of the theoretical and practical tools for modelling the dynamic behaviour of application software for a given platform. This is a new area of research, which will allow greater flexibility in designing optimal embedded systems.

<u>Testing and Verification</u>: This is transversal topic, which interacts with all the other topics in embedded systems design. It aims to ensure that the different design steps meet given properties, as well as the overall correctness of the implementation. This is a very active research topic, with results at different levels of the design process. The current challenge is in achieving on overall approach for testing and verification, focussing on two important aspects.

First is the Verification and Testing of real-time properties, to ensure that hard real-time constraints or quality of service constraints are met. Second is for Verification of Security Properties, where identification of gaps in security is desired.

<u>Control for Embedded Systems</u>: Embedded systems are deployed in the real world, and are often reactive to it. This interaction with the environment is intrinsic to the service provided. A large proportion of embedded systems can be considered to be controllers. On the other hand, most automated control applications will be implemented as embedded components. Thus, it is essential that work on joining control theory and embedded systems be included in the ARTIST2 NoE.

#### 3.1.2 Overview of the Year4 Research Results

An overview of each intra-cluster ("Cluster Integration") and inter-cluster ("NoE Integration") research activities is provided.

#### 3.1.2.1 Real Time Components

We have obtained some very significant results, on modelling heterogeneous systems:

- Work by INRIA, PARADES, and VERIMAG, on the theory of tagged systems provides conditions for correct implementation of synchronous systems on "less synchronous" architectures. Work by INRIA on new models of computation, the Kahn-extended Event Graph (KEG), which adds "static control" in the Model of Computation of Marked Graphs.

- Work on the BIP component framework, introduces a notion of expressiveness for component-based formalisms, which provides a basis for their comparison. This notion drastically differs from the usual one, as it takes into account the expressive power of composition operators (glue operators).

- Significant progress has been achieved in methods for distributed implementation of non-distributed specifications. VERIMAG studied a method for the automatic generation of distributed implementations of BIP models. INRIA, PARADES and VERIMAG studied the concept of loosely time-triggered architectures, implementing time-triggered architectures. Finally, fully asynchronous implementations of synchronous systems have been studied.

- Other results on distributed implementations include reliability, new heuristics in scheduling for reliability, design of communication architectures and time-triggered system-on-chip architectures.

We have also obtained significant results on Interfaces and Composability, including:

- The development of interface theories supporting component reuse (EPFL). We have shown that existing interface theories provide no formal support for component reuse. We enriched interface theories with a new operation allowing the same component to implement several different interfaces in a design.

- The development of contract-based verification techniques for the heterogeneous rich component (HRC) model (INRIA, PARADES, VERIMAG), in the framework of the SPEEDS project. The techniques allow handling multiparty interaction, as well as many different languages for describing notions of refinement under contexts. These results found application in the verification and analysis of HRC models.

- In joint work, ETHZ and Uppsala propose modular performance analysis techniques, based on the real-time calculus and timed automata. A prototype tool name CATS for compositional timing and performance analysis has been developed.

- VERIMAG has continued the work on compositional deadlock verification of BIP programs, and its implementation in the DeadlockFinder tool. Other results include the enhancement of existing component models, such as the synthesis of controllers from specifications and the generation of component models from their observed behaviour.

#### 3.1.2.2 Adaptive Real Time

The main results on "Flexible Resource Management for Real Time Systems" deal with flexible scheduling frameworks and their implementation:

- The architectural model developed in previous years has been updated and its API has been redesigned to support: Updated energy management, disk bandwidth management services, feedback control, and memory management. New communication networks have been added: CAN bus, WiFi, wired Ethernet, and switched Ethernet.

- The architectural model has been designed to be implementable on different platforms. Work has been performed in cooperation with Thalès Communications France, to integrate the contract-based scheduling framework, with a component-based framework.

- A work on the implementation of flexible traffic scheduling for switched Ethernet has been carried out in collaboration with the University of Pennsylvania and CMU. The aim of the work is to equip COTS switches with new scheduling capabilities allowing dynamic QoS management.

- A number of theoretical developments have been made this year including hierarchical scheduling, a multiframe extension to fixed priority scheduling, and adaptive algorithms for flexible resource management.

The main results on "Real Time Languages" deal with:

- The production of a survey on Real-Time Programming Languages. <u>http://www.artist-embedded.org/artist/ARTIST-Survey-of-Programming.html</u> The survey includes contributions from a large number of Artist2 partners and non-Artist2 individuals linked to the ARTIST community. It considers over 20 programming languages by presenting an overview of the main features and a classification allowing the comparison of their main features.

- Work on Ada 2005, including development of real-time utilities and the implementation of specific real-time mechanisms.

- Work on RT-Java, including a distributed version of RTSJ.

The main results on "Dynamic and Pervasive Networking" deal with:

- Work on the analysis and implementation of Wireless Sensor Networks.

- We have studied a methodology for modelling cluster-tree Wireless Sensor Networks. The methodology enables the computation of the worst-case end-toend delays, buffering and bandwidth requirements across source-destination paths.

- We also implemented QoS add-ons to the IEEE 802.15.4 and ZigBee protocols.

For these protocols, we have worked towards the implementation of the protocol stack over Erika, the real-time operating system for adaptive resource management developed by Pisa.

- Work on the analysis and implementation of Wired Networks.

- We studied topologies for robust communication in CAN and Ethernet networks. Robustness is characterized as protection against faults in the time domain and overloads.

- We studied schedulability analysis techniques for specific traffic types involving the transmission of long messages.

- Other work includes real-time support for middleware layers, as well as an Educational Testbed, supporting teaching of industrial wired/wireless networks.

The main results on "QoS Aware Components" are described in the section on "Inter-cluster Integration" below.

#### 3.1.2.3 Compilers and Timing Analysis

#### **Timing Analysis**

In addition to experimental work, we developed important results on Timing Analysis.

We have studied a notion of time predictability of cache architectures, which is the first precise notion found in the literature. Four different cache replacement strategies were compared and the LRU strategy was found to be optimal. This research is related to work within the PREDATOR FP7 project, which attempts to reconcile performance and predictability.

The study of Timing anomalies, where local worst-case choices may not lead to the global worst-case scenario, is essential for time predictability. We have studied techniques for handling timing anomalies for efficient WCET analysis, as well as for measuring the impact of timing anomalies on WCET analysis.

Other work on Timing Analysis includes parametric Timing Analysis, where some parameters of the program can remain unknown until execution. We also developed Timing Analysis techniques, in collaboration with BOSCH, taking into account operating modes of programs, computed semi-automatically. Finally, we developed WCET analysis for systems with preemptive scheduling.

#### Compilers

We developed research in the following directions:

We studied the influence of scratchpad memory allocation techniques on worst case execution times (WCET). We developed integer linear programming models to decide which parts of a program's code or data can be moved onto the highly predictable scratchpad. First experiments show WCET reductions of more than 50% for several benchmarks.

We also investigated WCET-aware register allocation techniques, by extending existing techniques based on graph colouring.

- TU Berlin studied optimization and verification methods for compilers. These techniques have been applied in a platform based on the Cosy compiler provided by ACE. We investigated new compiler optimizations to mitigate the impact of the memory wall on program performance, in particular for VLIW processors, such as Itanium. Furthermore, we investigated how code generation can be verified formally. The code generation process is specified by a set of rules describing how an abstract-level construct can be mapped to the machine level.

- We continued work on scalable source-level analysis and annotation-based timing analysis methods. The SATIrE infrastructure allows building analysers that take source code annotations as additional input, and generate output as annotations. This allows a significant increase in productivity, by requiring the user to annotate the relevant timing information that cannot be automatically computed. The integration of PAG was instrumental in investigating the scalability of analyses.

#### 3.1.2.4 Execution Platforms

For "Communication-centric Systems", we developed the following results:

We have developed new compositional performance evaluation techniques, based on modelling of systems as a hierarchically-structured network of functional nodes. The technique allows merging several single event streams to a hierarchical event-stream. It greatly improves the accuracy of the performance analysis.

Furthermore, we have studied online performance analysis techniques, allowing performing optimisations based on pending resource demands.

- We studied fault tolerance techniques for soft real-time systems. The issue is to be able to guarantee the deadlines for hard real-time processes, even in the presence of faults, while maximising the overall utility of the system. We have proposed a new scheduling strategy, where a set of fault-tolerant schedules is synthesized offline.

Furthermore, we have investigated fault-tolerance aspects related to the FlexRay protocol. Several techniques have been proposed for tolerating transient faults.

- We have studied analysis techniques for distributed wireless sensor networks.

Furthermore, we have extended existing communication-centric performance analysis techniques to systems with cyclic dependencies. We have shown that the analysis requires the iterative solution of fixpoint equations.

We have studied programming models for NOC-based systems, with a focus on parallelisation of the application, and reduction of load imbalance.

For "Design for Low Power", we have developed the following results:

- We have worked on modelling and optimisation of a miniaturized solar energy harvester. We focused on the optimisation of two important metrics: a) maximisation of the energy harvesting efficiency and b) the minimisation of the energy used for ineffective operations. A hierarchical control solution has been designed which overcomes several drawbacks of previously proposed approaches. A novel algorithm for approximate multi-parametric linear programming has also been proposed.

- We studied scheduling-based energy optimisation techniques for energy-scavenging wireless sensor networks.

We have worked on temperature-aware system level power optimisation techniques. The main challenge is to integrate temperature modelling into the framework of energyefficient system-level scheduling and voltage selection. The results obtained include power optimisation and analysis for nanometer technologies, system-level performance and power analysis for multi-processor systems on chip (SoC), system-level energy optimisation of real-time systems.

#### 3.1.2.5 Control for Embedded Systems

For "Control in Real-Time Computing", we have worked in the following directions:

- The work on <u>control of server systems</u> in Lund has continued.

We have expanded the feedback-based prediction scheme for controlling a single server queue, with a new control strategy. Our method maintains or improves performance, regarding average response time and loss of computational resources.

- We studied, in collaboration with Ericsson, techniques for feedback-based resource management in cellular devices.

- We studied, in collaboration with ABB, techniques for control and optimisation of networked systems.

For "Real-time techniques in control system implementations", we have worked in the following directions:

We studied <u>properties of event-based</u> control systems. We have continued our previous investigation of sporadic control of first-order stochastic systems. We have analysed how delay, jitter and measurement noise affect the performance of the control loops.

We have also studied event-based control for higher-order systems.

The implementation of event-based PI controllers has been studied, for measurements available at irregular intervals.

Finally, we studied state estimation techniques for event-based systems. The eventbased characteristics of the measurements are modelled as uncertainty sets. In each timestamp, the uncertainty sets and the regular noise descriptions are combined and simplified, keeping the complexity bounded.

- We developed a <u>control kernel</u>, which plays a role similar to an OS kernel. An efficient implementation has been completed and experimented for small control systems.

- We developed control-based techniques for <u>networked systems</u>.

We studied a modular control design methodology, ensuring maximal performance, stability, and adaptability.

We developed new results on optimal flow routing in multi-hop sensor networks.

In a continuation of work from Year 3, we have studied scheduling techniques for control and signal processing. We have implemented our own heuristics and evaluated their performances.

#### 3.1.2.6 Inter-cluster Integration

The planned NoE Integration activities have led to the following results:

#### QoS Aware Components:

We developed results along the following directions:

- <u>Specification of QoS properties using UML profiles and aspect-based approaches</u>. We studied methods for the composition of applications in real-time, taking into account their corresponding QoS properties.

- <u>Generation of analysable models from the UML models</u>. We studied techniques for extracting, from UML models, models for safety analysis. These models synthesize safety annotations included in the UML models.

We have participated in collaboration with companies and universities for defining the OMG standard « MDA Tool Component RFP ».

- <u>Composition of QoS-aware components and adaptability</u>. Our contributions include important results on achieving fault tolerance and adaptability in component frameworks (CEA-LIST, Thalès, UPM). We studied a concept of quality of service adaptability characterising a component's ability to adapt its quality during runtime. We have extended the UML standard profile to define adaptable elements with the associated QoS functions and their composition. The results obtained should allow the evaluation of architectural models to predict a system's QoS behaviour before its implementation.

- <u>QoS support in run-time components frameworks</u>. Our work in this direction includes a contribution to an API standard for QoS support in runtime components for multimedia middleware (UPM), as well as the design of a QoS management platform using a model-driven engineering process (INRIA).

#### **Resource-aware Design**

We developed work in the following directions:

- We studied resource analysis and management techniques. We used timed automata and the UPPAAL tool has been used for solving resource optimization problems. Furthermore, we studied experimental techniques for dynamic configuration on a coprocessor-coupled architecture.

- A key issue is <u>predictability</u> for multi-processor systems with a shared communication infrastructure. To cope with uncertainty in such systems and thus enforce their predictability, we studied the application of control-based techniques.

Other work on predictability included deals with the uncertainty of execution times. To reduce this uncertainty, we have studied parametric timing analysis techniques, allowing a more precise estimation of execution time bounds. Another avenue for improving predictability is the study of cache replacement strategies.

- As reported in a section on Timing Analysis, various Timing Analysis techniques have been studied in collaboration with teams from the CTA cluster.

- We worked on resource-aware techniques, both for design space exploration and mapping. These techniques use performance analysis by simulation and/or analytic models to determine optimal mappings for given efficiency requirements.

• We integrated MPARM multiprocessor simulation platform from Bologna, and the MEMSIM versatile memory hierarchy simulator from Dortmund.

#### Adaptive Real-time, HRT and Control

Work has progressed in the following directions:

- We studied various scheduling techniques, which require competencies, both from Adaptive Real Time and Control. These include: a) optimal period selection for multiple controllers under fixed-priority scheduling; b) optimal period selection and scheduling for multiple distributed controllers; c) event-driven control, embedded control and feedback scheduling.

- We also studied control-based mechanisms for <u>multimedia systems and protocols</u>. Three key technologies have been combined: a) reservation-based resource management; b) feedback scheduling; and c) dataflow modelling of multimedia applications.

- As mentioned for RTC, the LTTA (Loosely Time-Triggered Architecture) architecture has been proposed in the form of a middleware.

#### Quantitative Testing and Verification

Work has been carried out in the following directions:

- Significant contributions to <u>game-theoretic</u> approaches to real-time system testing. By modelling the systems as timed game automata and specifying the test purposes as formulas, we developed a timed game solver Tiga to synthesize testing strategies.

We studied games for different extensions of timed automata such as weighted timed automata, priced timed automata, multi-priced timed automata. The results relate to the complexity of decision problems for these automata, as well as model checking and synthesis algorithms. The notion of timed parity games has been studied, with a focus on robustness and complexity. We have also studied reachability in timed games.

- Continuing on work from previous years, we have extended and improved the functionality of the <u>UPPAAL tool</u>, including the use of slicing techniques for model optimization as well as features supporting interface theory for real-time systems.

- We have studied <u>quantitative testing</u> techniques. In particular, we have developed a theory allowing testing of systems in the presence of measurement imprecisions. We also studied testing methods for probabilistic processes.

- We have studied <u>quantitative model checking</u> techniques for timed models, including timed automata, linear hybrid automata and general non-linear hybrid systems. The work on verification has been applied to non-trivial case studies and systems, in particular in collaboration with industry.

- Finally, we have studied <u>compositional synthesis and verification techniques</u>. These include modular supervisory control, as well as the verification of component-based systems.

## 3.2 Joint Programme of Integration Activities (JPIA)

#### 3.2.1 Structure of the Integration Effort

This introduction has remained constant since the beginning of the project.

The Joint Programme of Integrating Activities contains the technical but non-research activities that participate in the overall effort. As with the JPRA, the main financing for these technical activities is derived from other sources, and is small in comparison with the overall objectives.

The JPIA is composed of Platform Activities (roughly one for each cluster), and Mobility actions between partners – both core and affiliated partners.

Integration between research teams work to achieve critical mass in 2 important dimensions:

- Strong integration within selected topics by assembling the best European teams, to advance the state of the art in the topic.

- Integration between topics to achieve the multi-disciplinary excellence and skills required for the development of future embedded technologies.

The ARTIST2 platforms integrate the results of long-term efforts, and are meant to be durable, evolving with the state of the art. The partners are committed to durability, and have invested significant resources into their development. The construction of ARTIST2 has provided the opportunity to assemble existing pieces into a rationally-structured set of platforms, covering the area of embedded systems design.

Some of the ARTIST2 platforms have international visibility, and the ambition is for these to serve as world-wide references in their respective topics.

Both types of integration are achieved through Joint Programme of Integration Activities (JPIA) activities involving state of the art research platforms, composed of competencies, resources, and tools targeting specific technical and scientific objectives around a chosen topic. These are made available to the R&D community for experimentation, demonstration, evaluation, and teaching.

Our assessment of Artist2 progress on integration over Year 4 is very positive.

#### 3.2.2 Progress on the Platforms

The following are the main highlights from the different clusters over the course of Year 4. These represent only a part of the total effort deployed.

#### 3.2.2.1 Real Time Components

Important results come from the SPEEDS IP, which developed modelling and validation techniques for the HRC (Heterogeneous Rich Component) framework. We defined and implemented a semantic-based common meta-model; developed a framework for a multiple-viewpoint component engineering; developed a framework for the composition of heterogeneous components. The HRC environment is connected to the BIP and Metropolis toolsets via translation tools. In particular, this allows the application of analysis and design space exploration techniques.

Work within the French national platform "OpenEmbeDD" includes the following contributions from CEA, INRIA and VERIMAG, in collaboration with industrial partners: 1) The development of the Papyrus editor for the UML / MARTE profile; 2) the performance evaluation tool PERSIFORM; 3) the BIP toolset.

Applications of our tools include work on "componentisation" of complex software by using BIP in collaboration with ASTRIUM, the simulation of wireless sensor networks by using PERSIFORM, and the certification of Smart-Card applications.

#### 3.2.2.2 Adaptive Real Time

We have concentrated our efforts on the development of an embedded platform for running real-time applications under severe resource constraints. The platform is composed of the Erika Enterprise real-time kernel, and the Flex hardware platform. We have developed a set of challenging real-time applications which are made available via the web. The same platform is used for educational experiments including a real-time controller.

#### 3.2.2.3 Compilers and Timing Analysis

#### Timing Analysis

Work on the AIR format has continued. The format was extended and adapted to the needs of the partners. The attribute database was extended with new attributes.

We also worked on the development and improvement of formats for ensuring the interoperability of the tools. The work on formats includes ALF for computation semantics representation, conversion of the ABSINT AIR format to SWEET format, and the definition of common flow description attributes.

As was the case last year, the WCET Challenge 2008 consisted of a set of benchmark programs and analysis tasks to be performed by the contestants. http://www.artist-embedded.org/artist/-WCET-08-.html

#### Compilers

We developed work in the following directions:

We designed a Static Loop Analyzer, allowing to estimate loop iteration bounds. This

information is essential for a large number program analyses. Our analyser improves

analysis techniques based on conventional abstract interpretation by integrating a new

static polytope-based loop evaluation method.

We have demonstrated the applicability of the analyser on benchmarks taken from the benchmark suites MRTC, DSPStone, MiBench, UTDSP and MediaBench. Our loop analyser was the only tool able to answer all questions related to flow fact during the WCET tool challenge 2008.

- In continuation of work performed in Year 3, we developed a new WCET-aware procedure positioning and cloning technique. The compiler optimisations obtained were exploited for WCET reduction. Results on real-world benchmarks show WCET reductions of 10% on average, while ACET is reduced by 2 on average.

- The cooperation between ACE and Aachen on the retargetable code optimizations has been continued. The conditional execution engines have been extended by a strong retargeting formalism.

#### 3.2.2.4 Execution Platforms

For "System Modeling Infrastructure", the work for Year4 was concentrated on extending formal models for platform modelling and performance, although some simulation-based work was continued. We developed work in the following directions:

- We worked on the formal verification of embedded systems and hardware architectures. The modelling is performed by using timed automata, and verification by using the UPPAAL tool. The models are generated automatically from high-level description languages. The properties verified are real-time with a focus on schedulability analysis, as well as design properties for a few circuits including the Simplified Data Encryption Standard (SDES).

- An important work direction is modelling and performance analysis for multi-processor and/or networked systems.

We studied relations between simulation-based and analytical methods for performance evaluation of distributed real-time systems. Based on experimental simulation results, we were able to draw interesting conclusions regarding the pessimism of formal approaches. The experiments were performed on FlexRay and CAN-based distributed systems.

We also studied interesting relations between MPA (Modular Performance Analysis) and Timed Automata.

- We have extended the fault-tolerant process model, to consider a combination of hardware and software fault-tolerant techniques. We have proposed a method for computing the reliability of a system, taking into account: a) hardening levels in hardware; b) the re-execution levels in software; c) scheduling for sharing recovery slacks.

- DTU has extended its simulation framework COSMOS to study the dynamic behaviour of runtime reconfigurable systems through design-space exploration experiments. Critical design issues in the reconfigurable architecture have been identified.

#### 3.2.2.5 Control for Embedded Systems

Work has been carried out in the following directions:

Continuing on work in previous years, we have added new features to TrueTime, a Matlab/Simulink -based tool for co-simulation of real-time control systems. New features in TrueTime include a new Ultrasound Network block, better support for Constraint Bandwidth Server scheduling and an improved user interface. The tool is available under the GNU General Public License (GPL). It has been used in laboratories and for educational purposes.

TrueTime is also used in the EUROSYSLIB ITEA2 project, led by Dassault Systems, as well as in the DySCAS project for modelling and simulating dynamically configurable systems.

- Continuing on work in previous years, we have extended and added new features to the TORSCHE scheduling toolbox for Matlab.

- We have worked within the framework of the DySCAS project, to provide simulation and analysis techniques. DySCAS is an autonomic platform-independent middleware for automotive embedded systems. It supports automatic configuration for contextaware behaviour, resource use efficiency, and self-healing to handle runtime-detected faults. Simulations within the Matlab/Simulink environment have been carried out, to

validate interfaces and functional behaviour as well as to validate quality of service and load balancing.

In the framework of the ATESST project, a UML profile for automotive embedded systems modelling has been studied. We developed a tool translating Simulink behavioural models into UML models for the CEA's Papyrus tool. Furthermore, a new approach for representing safety cases in Papyrus has been implemented.

#### 3.2.2.6 Testing and Verification

In continuation of the work initiated in previous years, we have pursued the following directions:

- We have further developed the UPPAAL Tiga tool for controller synthesis. The UPPAAL model checker has been further improved and optimized.

- IRISA have improved the symbolic test generation tool, STG, and a new version can be downloaded from INRIA Gforge: <u>https://gforge.inria.fr/plugins/scmsvn/viewcvs.php/?root=bjeannet</u>

- VERIMAG have applied their test generation tool TTG <u>http://www-verimag.imag.fr/~krichen/ttg/index.html</u> for the automatic generation of robotics observers.

- OFFIS have developed a modelling and verification framework for protocol validation and illustrated the concepts through a major industrial traffic communication protocol.

- BRNO have further optimized the DiVinE tool and evaluated its performance and scalability on large-scale parallel systems.

## **3.3 Joint Programme of Activities for Spreading Excellence** (JPASE)

The achievements and results from the Joint Programme of Activities for Spreading Excellence (JPASE) are contained in a separate deliverable, entitled: "Spreading Excellence".

Our actions for Spreading Excellence are at 2 levels:

- *Targeted towards affiliated partners* Affiliated partners are not core members in the consortium, but receive support for travelling to Artist2 meetings, and actively contribute to the implementation of the Joint Programme of Activities (JPA). These affiliated partners include industrial, SME, academic, and international collaboration affiliates.

- *Targeted towards the scientific and technical community in the large* This is achieved mainly bottom-up through the organisation of scientific events, publications, distribution of tools and components, industrial partnerships (not funded by Artist2), education; and through the Artist2 web pages.

- Targeted towards students

A particular focus has been placed on the Artist2 Summer Schools this year with a truly

outstanding programme of lecturers, and the innovation of providing the lectures in video

form on the Artist website.

Regarding Scientific events, we distinguish between conferences and workshops, schools, and high-level events mainly for International Collaboration.

#### 3.3.1 International Collaboration

Here, we focus on the workshops and schools organized outside the EU, globally by the NoE.

Further International Collaboration is carried out within the clusters, as reported in the cluster– level activity reports.

#### ARTIST2 South-American School for Embedded Systems 2008

http://www.artist-embedded.org/artist/-ARTIST-2-South-American-School-.html August 25-29, 2008 Universidade Federal de Santa Catarina, Florianopolis, Brazil Organised and funded by Artist.

After the successful First ARTIST2 South-American School for Embedded Systems in Buenos Aires, Argentina, this second edition in Florianopolis, Brazil, strengthens the cooperation between Europe and South America in the area of embedded systems, both at educational and research levels. For this purpose, the goal of the school is to provide state-of-the-art courses on embedded systems oriented towards advanced students and young researchers.

We believe the school provides the ground for cross-fertilization between Europe and South-America with an expected mutual high added-value. Therefore, the lectures given by European researchers were accompanied by talks and a poster session for participants to present and discuss their ongoing work.

Year 4 D2-Mgt-Y4

Executive Summary

#### Artist2 Summer School in China 2008

http://www.artist-embedded.org/artist/-Artist2-Summer-School-in-China-.html July 12-18, 2008 Shanghai, China Organised and funded by Artist.

This was the 3rd edition of a school on Embedded Systems Design. This year, the school was organized in collaboration with the SEI/ECNU and the LIAMA.

This year, we were able to do a far stricter degree of selection amongst the candidates. We selected 81– the fill list is available <u>here</u>.

#### Foundations of Component-based Design

September 30th, 2007 Salzburg, Austria - within <u>EmSoft</u> / <u>ES Week</u> <u>http://www.artist-embedded.org/artist/-Foundations-of-Component-based-.html</u> Artist2 organised and funded this event, within Embedded Systems Week.

Discuss recent results on component-based design with emphasis on design frameworks for real-time systems encompassing heterogeneous composition and models of computation. Especially frameworks for handling non-functional and resource constraints, design under conflicting dependability criteria, trade-offs between average performance and predictability.

The workshop aims to gather together researchers from computer science and electrical engineering and will seek a synthesis between the underlying paradigms and techniques. The focus is not only on fundamental results but also on their implementation in methods and tools and their concrete application in areas such as automotive, avionics, consumer electronics and automation.

#### Workshop on Embedded Systems Education (WESE 2007)

October 4-5, 2007 Salzburg, Austria (within <u>ES Week</u>) <u>http://www.artist-embedded.org/artist/-WESE-07-.html</u> Organised and funded by Artist

It is widely recognized that the embedded system domain is a multidisciplinary one, requiring a large variety of skills from control and signal processing theory, electronics, computer engineering and science, telecommunication, etc., as well as application domain knowledge.

This has motivated a recent but ever growing interest in the question of educating specialists in this domain and this has also been recognized as a particularly difficult problem.

This third workshop on the subject aims to bring researchers, educators, and industrial representatives together to assess needs and share design, research, and experiences in embedded systems education. Industrial needs regarding embedded systems education

#### Year 4 Event: ARTIST2 meeting on Integrated Modular Avionics

November 12-13, 2007 Roma, Italy http://www.artist-embedded.org/artist/-ARTIST2-meeting-on-Integrated-.html Organised and funded by Artist

Today, the exponentially increasing diversity of airborne systems results in an increasing number of computers and controllers for system management, monitoring, and control. The development of specific ad-hoc solutions causes increases in costs, which in turn impacts purchase prices and operational costs. To overcome this, standardization principles and reuse of function units are now considered, via Integrated Modular Avionics.

Integrated Modular Avionics (IMA) has set the principles of standardized components and interfaces of hardware and software in aircraft. These principles have been applied for the first time in the development of the Airbus A380. Further developing IMA raises a number of issues that require fundamental research efforts, in tight coordination with engineering needs.

ARTIST2, the European Network of Excellence on embedded systems has organized, as part of its activity on "scientific challenges in specific industrial sectors", a two-day workshop dedicated to Systems, Software, and Architecture, aspects of IMA.

#### 3.3.2 Organisation of Schools

In Year 4, Artist2 has directly organized and funded the following schools and courses:

#### Special Year 4 Event: ARTIST2 Summer School 2008 in Europe September 8-12, 2008 Autrans (near Grenoble), France http://www.artist-embedded.org/artist/-ARTIST2-Summer-School-2008-.html Organised and funded by Artist –this school was an outstanding success.

NB: Videos from the lectures are in post-production and will be made available free of charge to the general public.

The Summer School offered a number of foundational tutorials, accompanied by a selection of lectures on exciting emerging technologies and industrial applications - given by leading scientific and/or industrial experts.

An innovative step has been to provide the lectures in the form of videos, available for free via the website (currently under preparation – this will be shown at the review).

The ARTIST Summer School 2008 was held in the beautiful Vercors mountains in Autrans, near Grenoble, Sept 8-12. The school was organised by the Artist2 European Network of Excellence on Embedded Systems Design, which gathers 42 top European institutions. Artist's mission is to coordinate European research in the area around an ambitious joint research agenda, and to spread excellence through targeted events such as international workshops, schools and seminars.

Artist has a strong tradition in organising top-quality schools. This is the fourth edition of yearly schools on embedded systems design, and is meant to be exceptional in terms of both breadth of coverage and invited speakers.

The topics covered include Modeling and Validation, Compilers and Timing Analysis, Adaptive Real Time Systems, Control for Embedded Systems, Execution Platforms and MPSoC. We seek a balance between foundational aspects and applications. Speakers included recognized leading researchers and engineers.

The school was open to PhD students, researchers, and engineers. Attendance will be limited to 80 selected participants.

#### ARTIST2 South-American School for Embedded Systems 2008

August 25-29, 2008 Universidade Federal de Santa Catarina, Florianopolis, Brazil http://www.artist-embedded.org/artist/-ARTIST-2-South-American-School-.html

After the successful First ARTIST2 South-American School for Embedded Systems in Buenos Aires, Argentina, this second edition in Florianopolis, Brazil, strengthens the cooperation between Europe and South America in the area of embedded systems, both at educational

and research levels. For this purpose, the goal of the school is to provide state-of-the-art courses on embedded systems oriented towards advanced students and young researchers.

This school is described in detail above, in the section on International Collaboration.

#### Artist2 Summer School in China 2008

July 12-18, 2008 Shanghai, China http://www.artist-embedded.org/artist/-Artist2-Summer-School-in-China-.html

This was the 3rd edition of a school on Embedded Systems Design. This year, the school was organized in collaboration with the SEI/ECNU and the LIAMA.

This year, we were able to do a far stricter degree of selection amongst the candidates. We selected 81participants – the fill list is available <u>here</u>.

This school is described in detail above, in the section on International Collaboration.

#### **Real-Time Kernels for Microcontrollers: Theory and Practice**

June 23-25, 2008 Pisa, Italy http://www.artist-embedded.org/artist/-Real-Time-Kernels-for-.html

The course on Real-Time Kernels for Microcontrollers aims to introduce the basic concepts of Real-time Systems targeted to Embedded Systems, which are often implemented using microcontrollers. The course will briefly illustrate the theoretical background of real-time scheduling, resource-aware techniques, and wireless communication based upon the IEEE 802.15.4 protocol.

ARTIST2 Graduate Course on: Automated Formal Methods for Embedded Systems 2008 June 16-24, 2008 DTU - Lyngby, Denmark

http://www.artist-embedded.org/artist/-Automated-Formal-Methods-for-.html

In the lectures, we introduce a comprehensive set of state-based models as well as automatic procedures for their analysis. The exercise classes will complement this by providing hands-on experience with appropriate verification tools.

#### ARTIST2 Graduate Course on Embedded Control Systems

May 26-30, 2008 Stockholm, Sweden http://www.artist-embedded.org/artist/-Graduate-Course-on-Embedded-.html

The course provides an account of state of the art theory and techniques that address the connection and integration of the areas of Control systems and Embedded systems.

#### 3.3.3 Organisation of Workshops

In Year 4, Artist2 has directly organized and funded the following workshops.

#### MoCC 2008

July 3-4, 2008 Eindhoven, Netherlands http://www.artist-embedded.org/artist/-MoCC-2008-.html

Embedded systems are omnipresent in modern society, and society crucially depends on their proper functioning. The complexity of embedded system design however is increasing rapidly, through the use of multiprocessor cores, through the integration of embedded systems in

ubiquitous networks, and through the increasing interaction between embedded systems and their users and environments. To obtain a reliable operation of embedded systems while maintaining resource efficiency, the embedded system design process needs to be based on a solid basis of computational models.

#### WCET'08

July 1st, 2008 Prague, Czech Republic (with <u>ERCTS 2008</u>) http://www.artist-embedded.org/artist/-WCET-08-.html

The goal of the workshop is to bring together people from academia, tool vendors and users in industry that are interested in all aspects of timing analysis for real-time systems. The workshop fosters a highly interactive format with ample time for in-depth discussions.

#### **OSPERT 2008**

*July 1st, 2008 Prague, Czech Republic (in conjunction with <u>ECRTS</u>) <u>http://www.artist-embedded.org/artist/-OSPERT-2008-.html</u>*

This workshop is intended as a forum for researchers and practitioners of RTOS to discuss the recent advances in RTOS technology and the challenges that lie ahead.

#### Movep'08

June 23-27, 2008 Orleans, France http://www.artist-embedded.org/artist/-Movep-08-.html

MOVEP brings together researchers, students and people from industry working in the fields of control and verification of concurrent and reactive systems.

#### **COMES 2008**

June 17-18, 2008 Sigtuna, Sweden http://www.artist-embedded.org/artist/-COMES-2008-.html

Component-based development aims of separation of development of components from systems, and reuse of existing components. This approach brings many (known) advantages, but also many challenges of which some are specific or in particular important for embedded systems. Since for embedded systems non-functional properties and resource constraints are of particular importance, this workshop focus on component-based approaches that ensure predictability of the system properties.

#### Mapping of Applications to MPSoCs

June 16-17, 2008 Schloss Rheinfels, St. Goar, Germany http://www.artist-embedded.org/artist/-Mapping-of-Applications-to-MPSoCs-.html

1st Workshop on Mapping of Applications to MPSoCs

#### DataFlow Modeling for Embedded Systems

May 5th, 2008 Pisa, Italy

http://www.artist-embedded.org/artist/-DataFlow-Modeling-for-Embedded-.html

The topic of this workshop is the dataflow model/language CAL (CAL Actor Language), that recently has been developed within the Ptolemy II project at University of Berkeley. CAL is currently being used within the FP7 STREP project ACTORS and by Xilinx for modelling FPGA applications. CAL is also in the process of being adopted as the specification language for codecs within the MPEG-4 standard.

The aim of this workshop is to bring together the groups that are working with CAL and to discuss how CAL can be used within the context of embedded systems. The workshop is a

one day event with a number of invited speakers, both from industry and academia. It is aimed at the novice CAL programmer, as well as the more seasoned dataflow researcher.

#### APRES'08

April 21st, 2008 St. Louis, MO, USA http://www.artist-embedded.org/artist/-APRES-08-.html

Adaptive systems can respond to environmental changes including hardware/software defects, resource changes, and non-continual feature usage. As such, adaptive systems can extend the area of operations and improve efficiency in the use of system resources. However, adaptability also incurs overhead in terms of system complexity and resource requirements. The purpose of the workshop is to discuss new and on-going research that is centred on the idea of adaptability as first class citizen and consider the involved tradeoffs.

#### SLA++P'2008

*April 5th, 2008 Budapest, Hungary* - an <u>ETAPS'08</u> event. <u>http://www.artist-embedded.org/artist/-SLA-P-2008-.html</u>

Model-driven High-level Programming of Embedded Systems, SLA++P'2008

#### ARTIST2 Timing Analysis activity meeting

March 13th, 2008 Munich, Germany http://www.artist-embedded.org/artist/-ARTIST2-Timing-Analysis-activity-.html

Timing Analysis activity meeting within the Compilers and Timing Analysis cluster of ARTIST2 (in conjunction with the DATE'08 conference)

#### ATESST Open Workshop

March 3rd, 2008 Brussels, Belgium http://www.artist-embedded.org/artist/-ATESST-Open-Workshop-.html

Model based development of embedded systems: the EAST-ADL approach for automotive applications - An <u>ATESST project</u> Event.

#### Synchron 2007

November 26-30, 2007 Bamberg, Germany http://www.artist-embedded.org/artist/-Synchron-2007-.html

This workshop is devoted to all aspects of synchronous programming: languages, compiling techniques, formal methods, programming environments, execution platforms, semantics issues, code generation.

#### ARTIST2 meeting on Integrated Modular Avionics

November 12-13, 2007 Roma, Italy http://www.artist-embedded.org/artist/Integrated-Modular-Avionics.html

Integrated Modular Avionics (IMA) has set the principles of standardized components and interfaces of hardware and software in aircraft, applied for the first time in the development of the Airbus A380.

WESE'07: WS on Embedded Systems Education October 4-5, 2007 Salzburg, Austria (within <u>ES Week</u>) http://www.artist-embedded.org/artist/WESE-07.html

This third workshop on the subject aims to bring researchers, educators, and industrial representatives together to assess needs and share design, research, and experiences in embedded systems education.

#### Foundations of Component-based Design

September 30th, 2007 Salzburg, Austria - within <u>EmSoft</u> / <u>ES Week</u> <u>http://www.artist-embedded.org/artist/Foundations-of-Component-based.html</u> Discuss recent results on component-based design with emphasis on design frameworks for real-time systems encompassing heterogeneous composition and models of computation.

#### Between Control and Software (in honour of Paul Caspi)

September 28th, 2007 VERIMAG - Grenoble, France

This workshop, synchronized with the retirement of Paul Caspi in autumn 2007, brought together experts in the field and collaborators of Paul at different periods for a series of lectures.

http://www.artist-embedded.org/artist/Between-Control-and-Software.html

#### 3.3.4 Keynotes, Tutorials provided to the Embedded Systems Community

Over the course of Year 4, the Artist2 consortium has provided at least 178 keynotes, workshops, and tutorials to the embedded systems community.

Details including web links are available in the deliverable on Spreading Excellence.

#### 3.3.5 Industrial Liaison

Artist2 has a wide array of affiliated industrial and SME partners, as described above. Most of these partners have participated in some way in the Artist2 technical meetings and the overall effort. There is strong, high-level industry participation through the various Spreading Excellence events organised by Artist2. Our active involvement in the European Technology Platform ARTEMIS also has a significant and long-term impact.

A more detailed description of industrial liaison activities is provided below.

#### 3.3.5.1 ARTEMIS ETP

Several RTC Cluster partners, including CEA, INRIA, OFFIS, PARADES, VERIMAG; and TU Vienna, are actively involved in ARTEMIS, an initiative to form a European technology platform on embedded systems supporting the needs for various industrial and academic embedded application domains, such as the automotive, avionics, but also the real-time requirements of consumer electronics. The interaction with ARTEMIS is expected to influence the work within ARTIST2 positively towards establishing a well-defined conceptual fundament that is useful for academia and industry. Several partners (CEA, INRIA, OFFIS) are involved in EICOSE, the recently established European Institute for COmplex and Safety Critical Embedded Systems Engineering pushed by two French clusters System@tic Paris Région and Aerospace in association with the German cluster SafeTrans. EICOSE has been selected as the ARTEMIS Innovation Cluster on Transportation. VERIMAG and FT R&D contribute within French MINALOGIC cluster to promote the creation of a center of excellence in ARTEMIS encompassing "Nomadic environments" and "Private space" application contexts of

the ARTEMIS SRA chart. Contacts have been taken with Nokia and ElectroBit from the Finlandais Symetra Consortium.

The Joint Undertaking Artemis has been created in February 2008, and is about to close the evaluation of proposals submitted to the first call of the Artemis Joint Undertaking. As described above, EICOSE has played an instrumental role in coordinating the research priorities of both industrial and academic stakeholders in the transportation domain, contributing significantly to the Artemis Multi Annual Strategic Plan in the formation of three out of eight subprograms also forming the basis for the 1<sup>st</sup> call. Both OFFIS and CEA are members of the EICOSE steering board.

#### 3.3.5.2 Industrial Liaison within the clusters

In the section on "Industrial Sectors", within the cluster-level activity reports, detailed descriptions of collaborations between Artist2 teams and industrial partners are provided.

#### 3.3.6 Publications

The Artist2 community has continued to be very active in publishing in scientific journals and conferences, as attested by the list of publications provided in this document. Clearly, this represents a huge amount of work. Publication of research is a bottom-up process, which may seem chaotic – but this is intrinsic to research.

Over the course of Year 4, the Artist2 consortium has published at least 184 joint papers, involving at least two distinct Artist2 core or affiliated partners. References for these are provided in the deliverable on Spreading Excellence.

The ARTIST community clearly leads the area, through the organisation of scientific events, the publication of seminal papers, education, and international collaboration.

### **3.4 Managing the Network of Excellence (JPMA)**

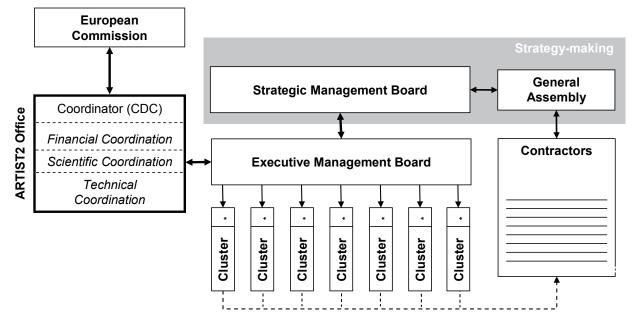

#### Joint Programme of Management Activities

We believe that the current two-tiered Management structure - dividing the management amongst cluster leaders and the Strategic Management Board composed of both cluster leaders and a limited number of other selected prominent core partners – has been the right one for managing such a large research entity. It has provided the right combination of flexibility and accountability, while leaving room for innovation and evolution.

This management structure is reproduced with adaptations in the ArtistDesign NoE. The adaptations reflect the greater cohesion between partners, and move to capitalize on and strengthen the integration achieved in Artist2.

## 4. End Results

We have achieved a significantly more integrated scientific community. Initially, there was a strong fragmentation by topics and communities, with little interaction between them. Over the course of the NoE, the clusters have evolved and merged. A gradually cohesion has taken place, through transversal "NoE Integration" activities, and more importantly through strategic alliances.

We are seeing a convergence of interests, and the gradual emergence of recognized leaders.

**Executive Summary**

Year 4 D2-Mgt-Y4

Executive Summary

IST-004527 ARTIST2 Network of Excellence on Embedded Systems Design

# Periodic Activity Report for Year 4

Joseph Sifakis – Artist2 Scientific Coordinator Bruno Bouyssounouse – Artist2 Technical Coordinator

Artist2 Consortium

Executive Summary

## **Table of Contents**

| Executive Summary                                                    |    |

|----------------------------------------------------------------------|----|

| 1. Project Objectives                                                | 2  |

| 2. Contact Details and Contractors Involved                          | 3  |

| 2.1 Core Partners                                                    | 3  |

| 2.2 Affiliated Partners                                              | 4  |

| 3. Vision and Assessment of the Work Performed                       | 11 |

| 3.1 Joint Programme of Research Activities (JPRA)                    | 12 |

| 3.1.1 Structure of the Research Effort                               | 12 |

| 3.1.2 Overview of the Year4 Research Results                         | 14 |

| 3.2 Joint Programme of Integration Activities (JPIA)                 | 21 |

| 3.2.1 Structure of the Integration Effort                            | 21 |

| 3.2.2 Progress on the Platforms                                      | 21 |

| 3.3 Joint Programme of Activities for Spreading Excellence (JPASE)   | 25 |

| 3.3.1 International Collaboration                                    | 25 |