### synchronous dataflow for free (SDF<sup>3</sup>) and other tool developments

Sander Stuijk, Marc Geilen, Twan Basten m.c.w.geilen@tue.nl

Map2MPSoC Workshop, November 28, 2008

### overview

- tools TU/e

- **SDF**<sup>3</sup> (extensions)

- Pareto Calculator

- MAMPS

- developments

- dynamism, scenarios, SADF

- memory mapping

- relation to other work

- SDF3 demo

### mocc

- model-based approach to mapping and scheduling with performance guarantees

- dataflow model of computation

- specifically (extensions of) synchronous dataflow (border of decidability in Christian's/Twan Basten's slide)

## what do we have?

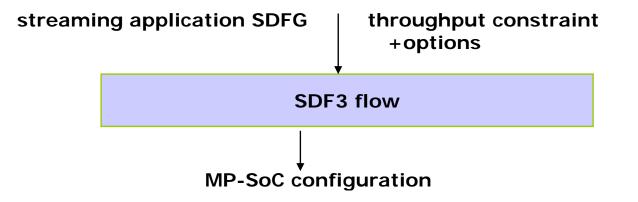

- yes, it's a 'model to model' flow...

- but a fairly realistic one...

- ...and some generic dataflow analysis tools

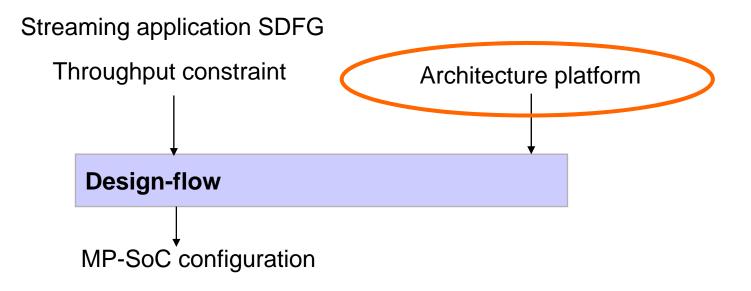

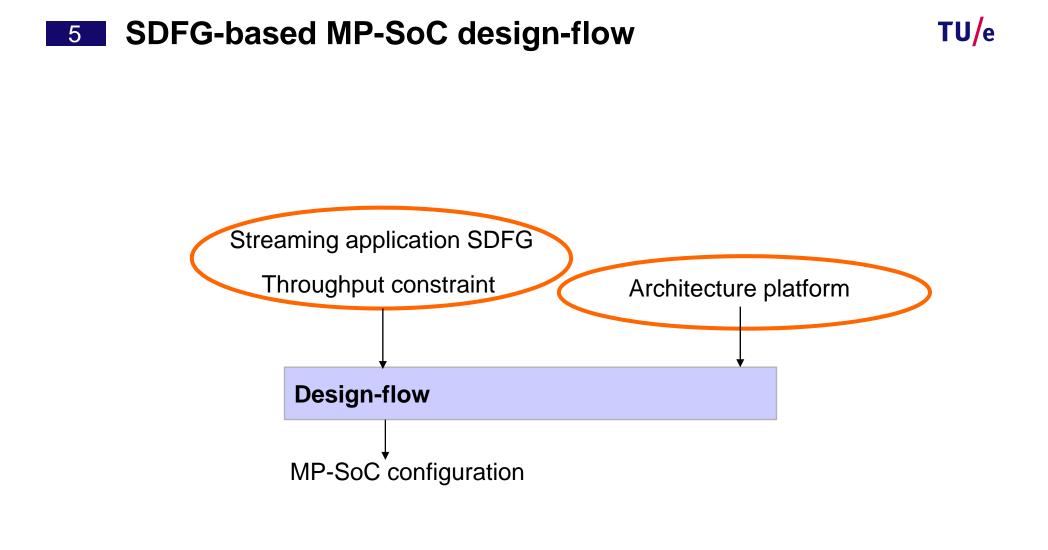

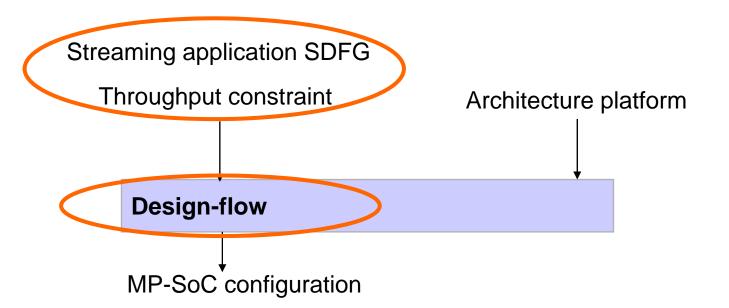

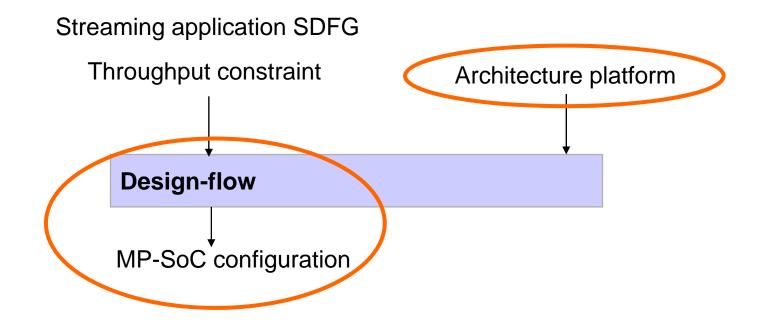

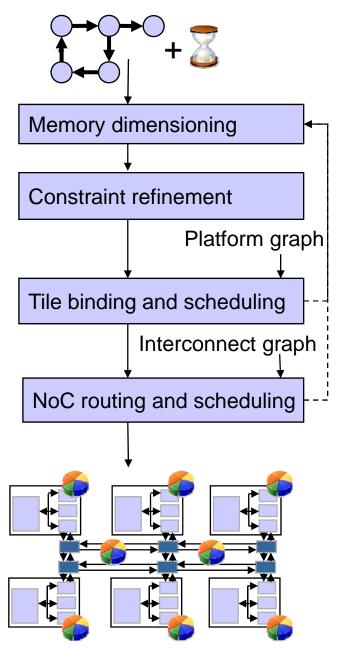

### **SDFG-based MP-SoC design-flow**

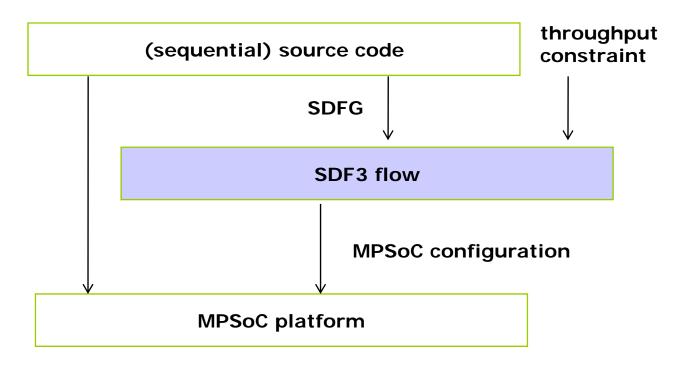

## what we want to get

- to use model and flow for source code to realisation flow

- to allow more dynamism in the model

### SDF

- synchronous dataflow model of computation

- model applications conservatively

- model resources, fifos, NoCs

- model predictable arbitration, TDMA, latency-rate

- analysis algorithms

- efficient throughput calculation

- latency

- deadlock, liveness, boundedness

- parametric throughput analysis

# **SDF<sup>3</sup>: SDF For Free**

#### SDF3 offers

- SDFG transformation and analysis algorithms

- an SDFG random graph generator, more powerful than TGFF

- links to visualization and simulation software for SDFGs

- advanced MP-SoC binding and scheduling functions for SDFGs

#### SDF3 functionality is available as

- command-line tools

- C/C++ API

## other TU/e tools

#### Pareto Calculator

- supports compositional calculation of multi-dimensional trade-offs

- trade-offs are used for instance also by Erlangen, Zürich, Daedalos

- based on concept of Pareto optimality

- implements Pareto Algebra

- on the web: www.es.ele.tue.nl/pareto

# other TU/e tools

- **MAMPS** (work by Akash Kumar)

- Multi-Application Multi-Processor Synthesis

- profiling based automatic mapping of multiple applications onto an FPGA based multiprocessor system with Microblaze cores and point-to-point connections.

- uses Leiden's KPNGen for paralellisation.

- on the web: www.es.ele.tue.nl/mamps

## relation to other work

- dataflow models used by several partners. Leiden, Bologna, NXP, Zürich, Erlangen, ...

- can use our generic SDF analysis algorithms

- use SDF<sup>3</sup> instead of Task Graphs For Free (TGFF) ! :-)

- Pareto analysis and trade-offs. Genereric multidimensional trade-off analysis and desing-space exploration.

compute Pareto front, approximations, compositional calculations, fancy things like partially ordered objectives

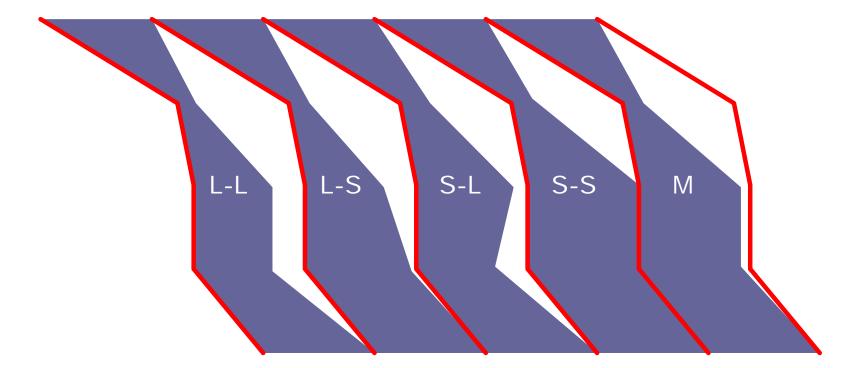

### scenarios

- scenarios: situations similar from a resource usage point of view

- for instance frame types or block types

- if we can detect scenarios, we can exploit them

- for dataflow models: every scenario has its own dataflow graph (sometimes that is the same graph structure, but with different execution times)

- Scenario Aware Dataflow synchronous dataflow graphs are (too?) static

### scenario aware dataflow

- Synchronous Data Flow is attractive for its analysability

- ...but it is often too static

- dynamism in SDF can be modelled as different scenarios of ordinary SDF behaviour

- system switches between scenarios

- there is no free lunch: analyse scenario switches

- we can analyse SADFs using Max-Plus algebra (not yet in SDf3)

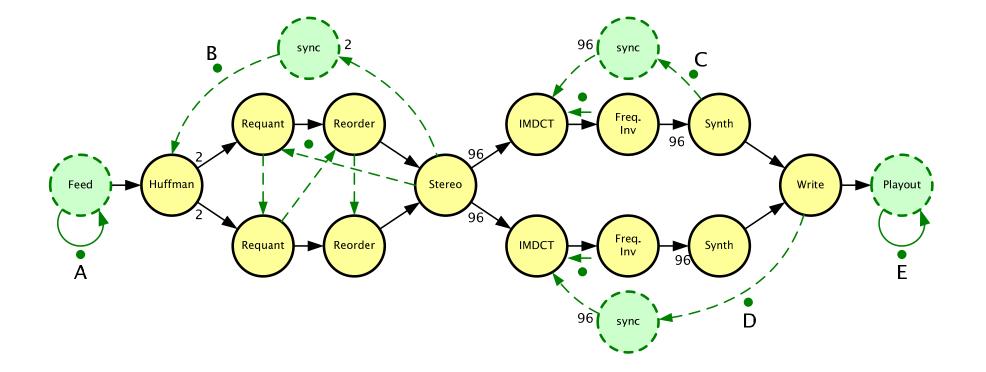

### mp3 short block scenario

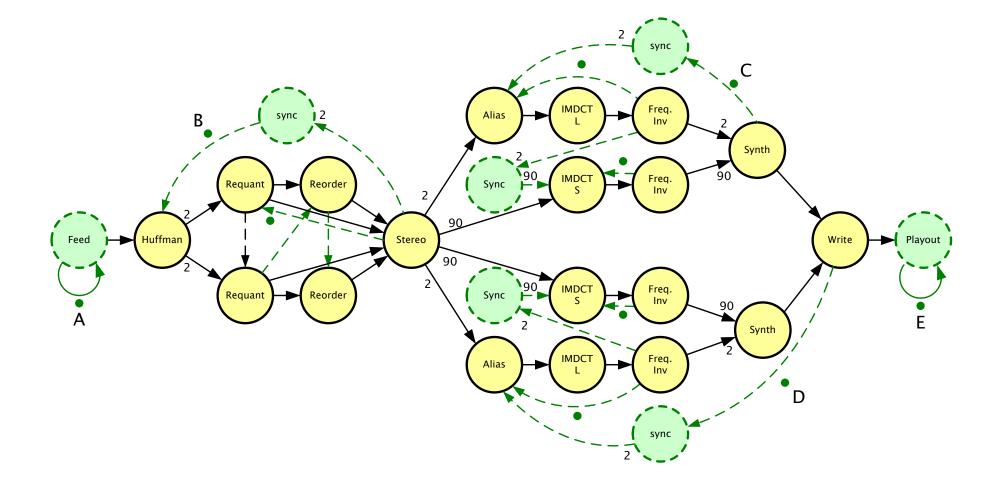

### mp3 mixed block scenario

#### **SDF<sup>3</sup>: SDF For Free**

Department of Electrical Engineering Electronic Systems

TU/e

SDF3 offers

- SDFG transformation and analysis algorithms

- an SDFG random graph generator

- links to visualization and simulation software for SDFGs

- advanced MP-SoC binding and scheduling functions for SDFGs

SDF3 functionality is available as

- command-line tools

- C/C++ API

#### **3** SDFG-based MP-SoC design-flow (SDF<sup>3</sup>)

TU/e

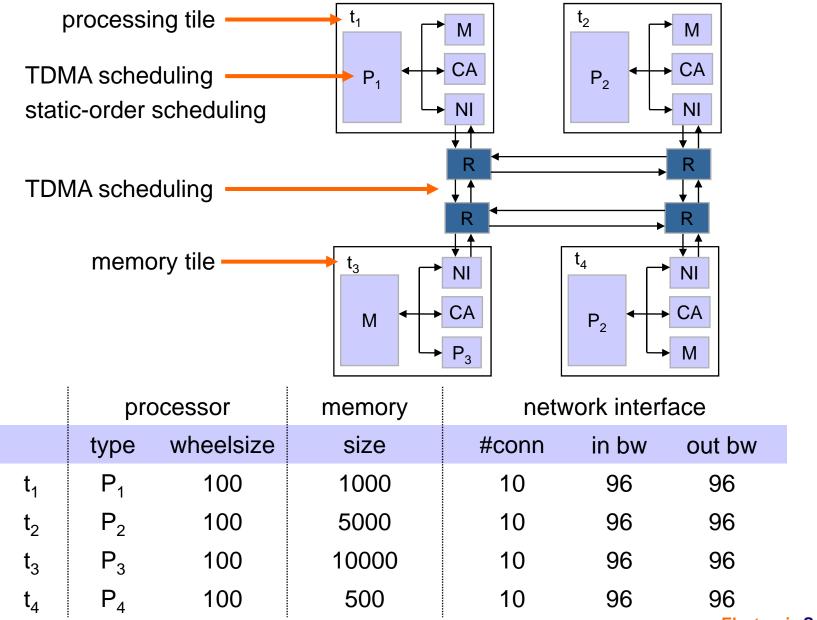

4 Predictable platform

**Electronic Systems**

#### TU/e

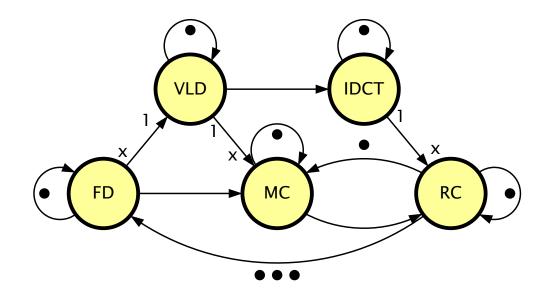

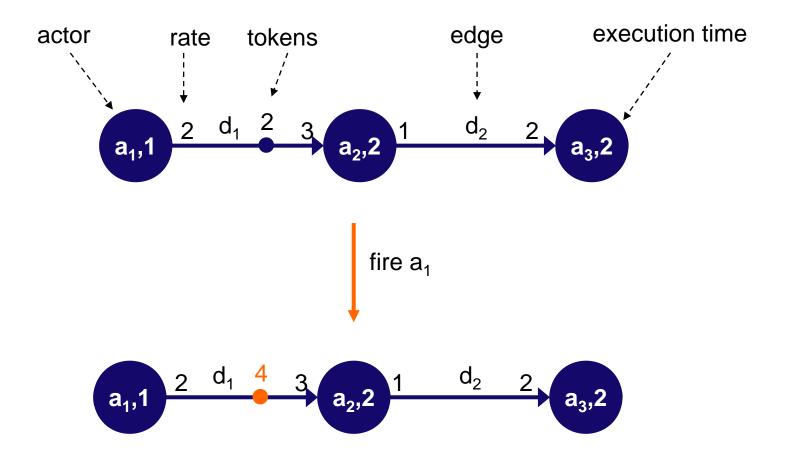

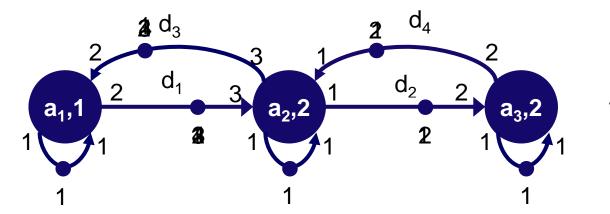

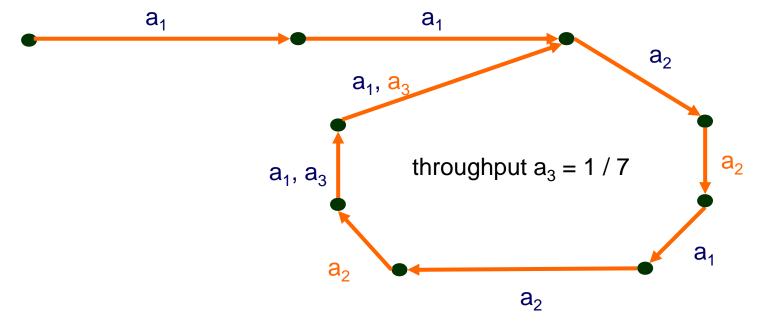

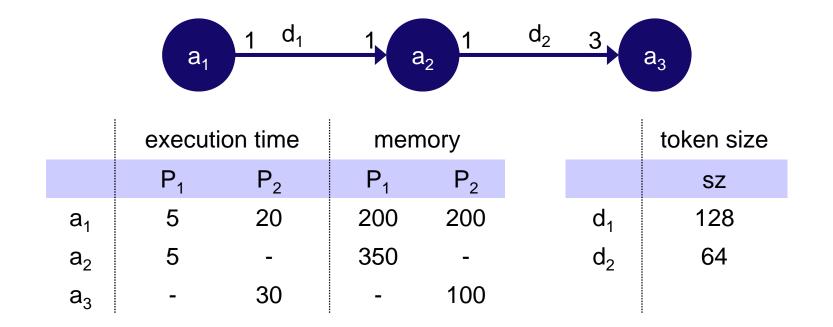

#### **6** Synchronous Dataflow Graphs

TU/e

#### 7 Timed SDF state space

$\langle d_1, d_2 \rangle \rightarrow \langle 4, 2 \rangle$

State: ((d<sub>1</sub>, d<sub>2</sub>, d<sub>3</sub>, d<sub>4</sub>), ({a<sub>1</sub>}, {a<sub>2</sub>}, {a<sub>3</sub>}))

**Electronic Systems**

#### TU/e

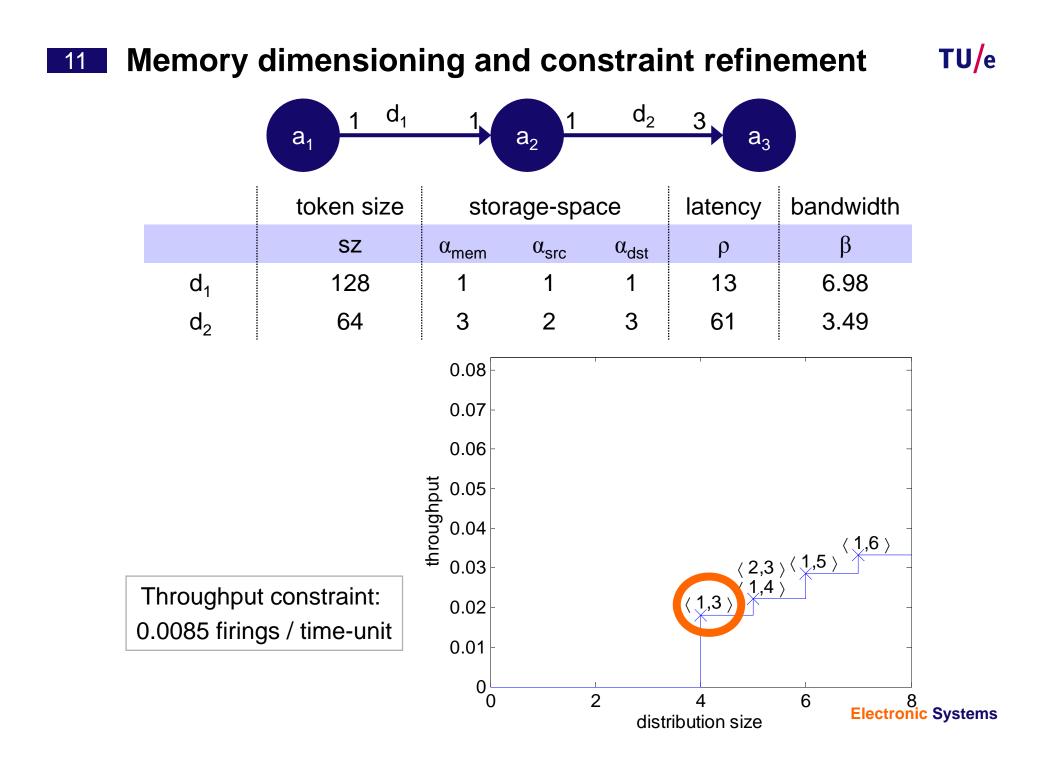

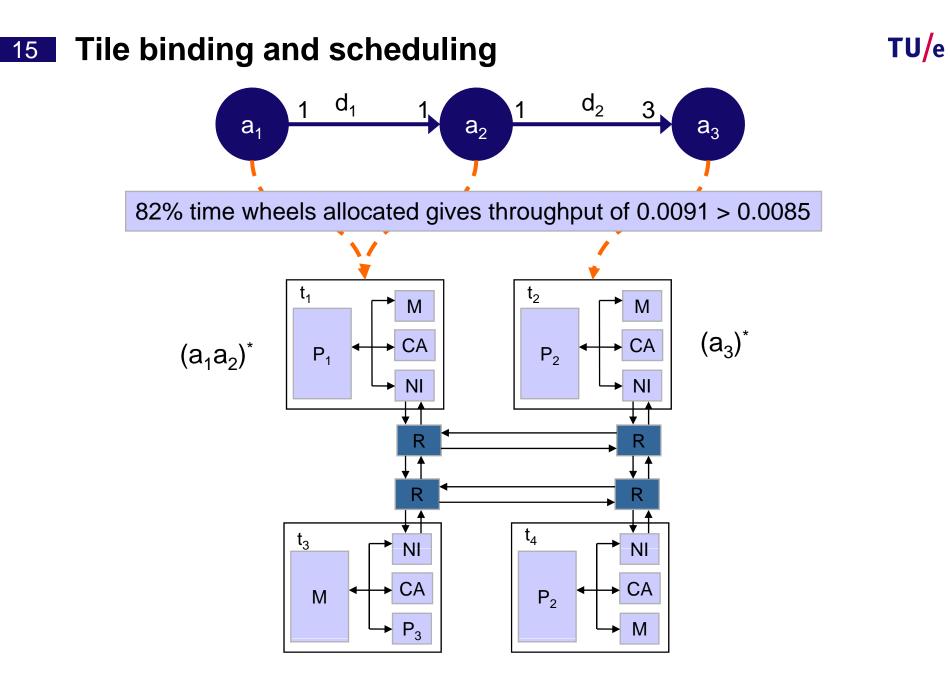

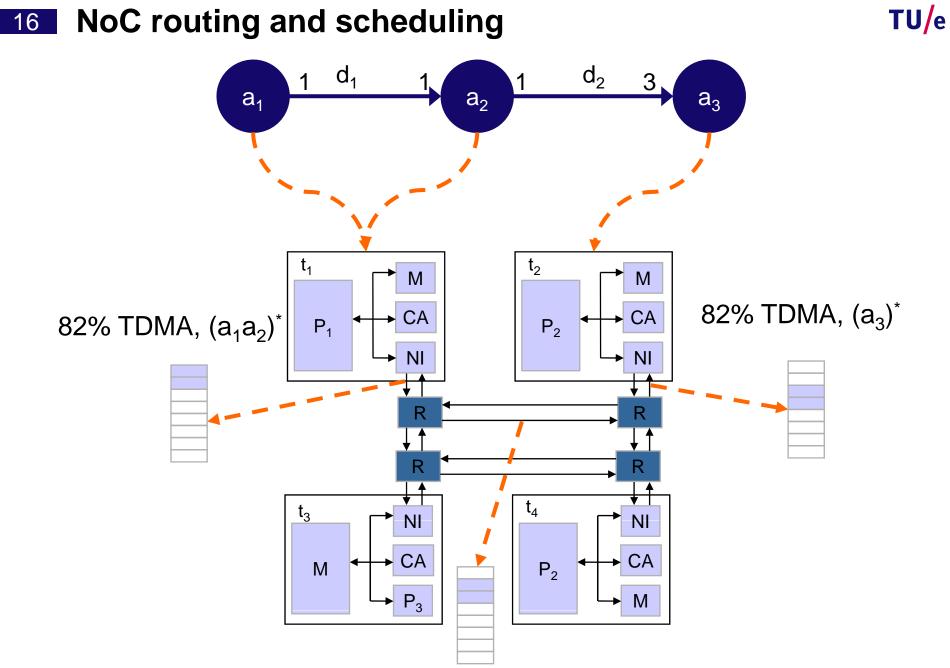

#### 8 Streaming application SDFG

Throughput constraint: 0.0085 firings / time-unit

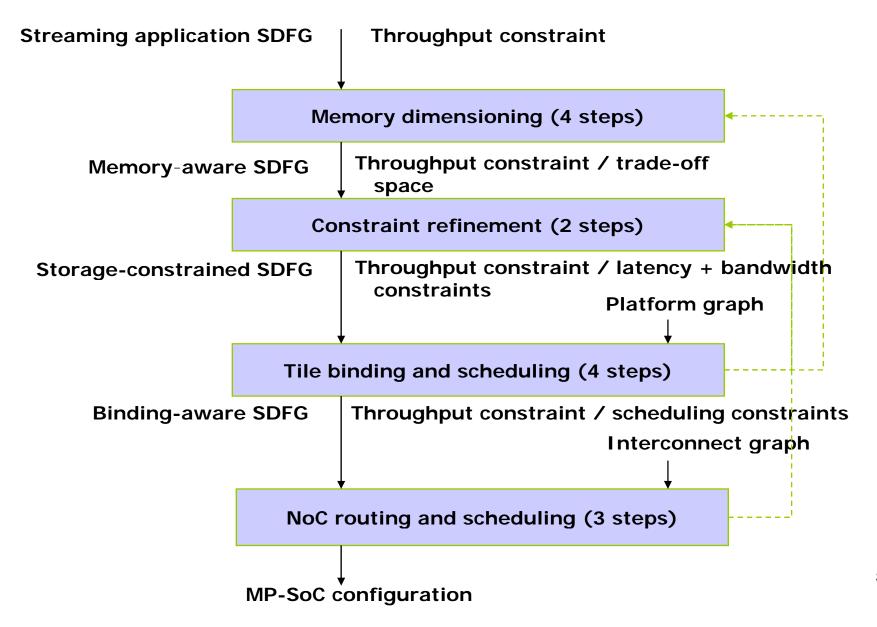

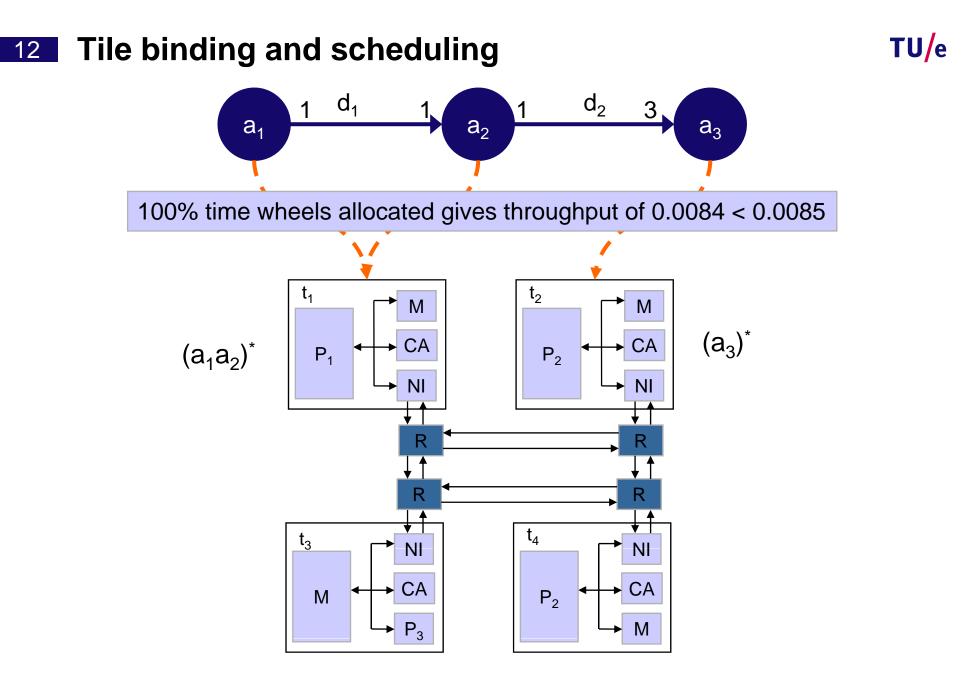

#### 9 SDFG-based MP-SoC design-flow

TU/e

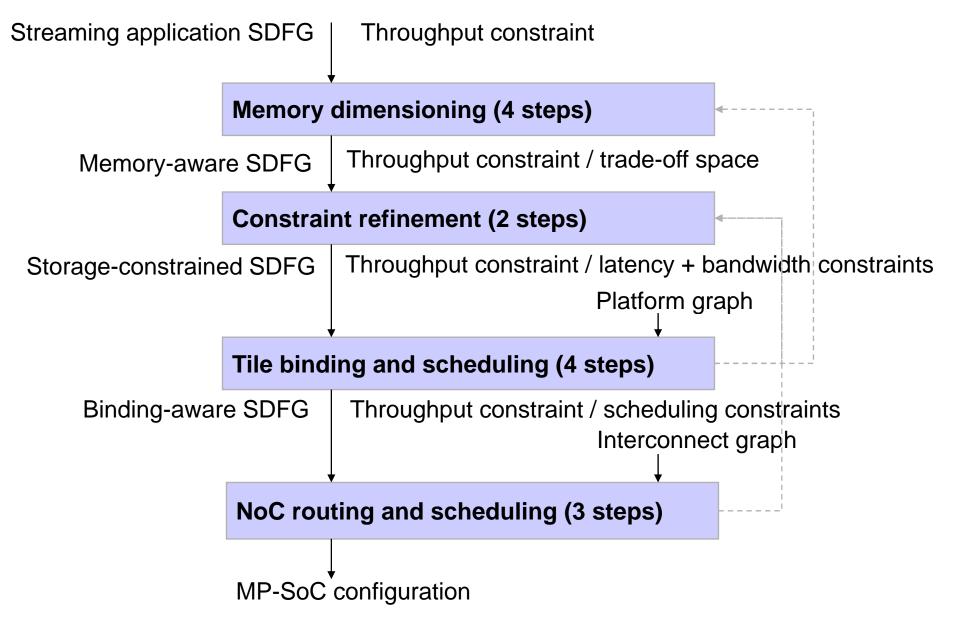

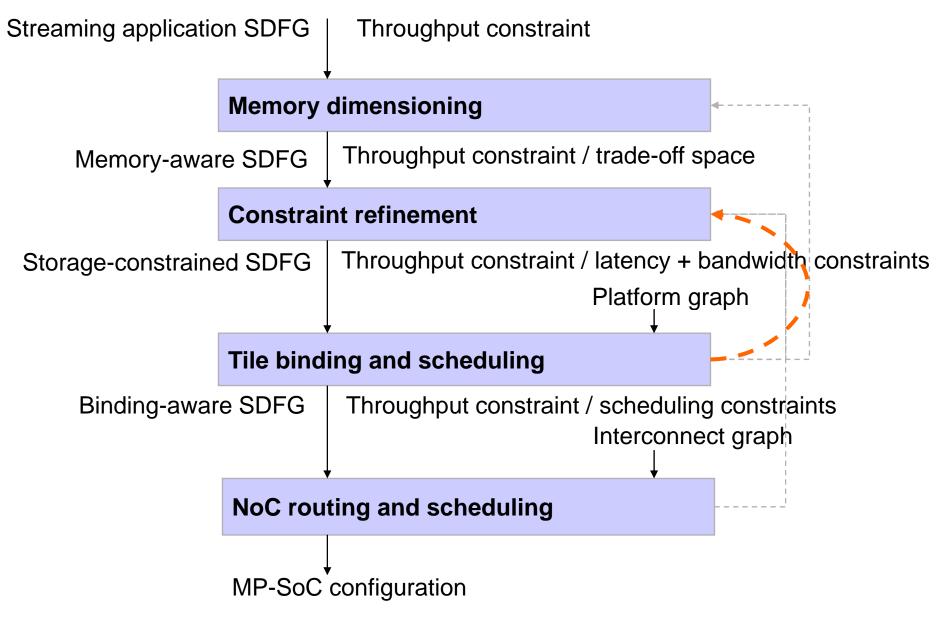

### **10** SDFG-based MP-SoC design-flow

TU/e

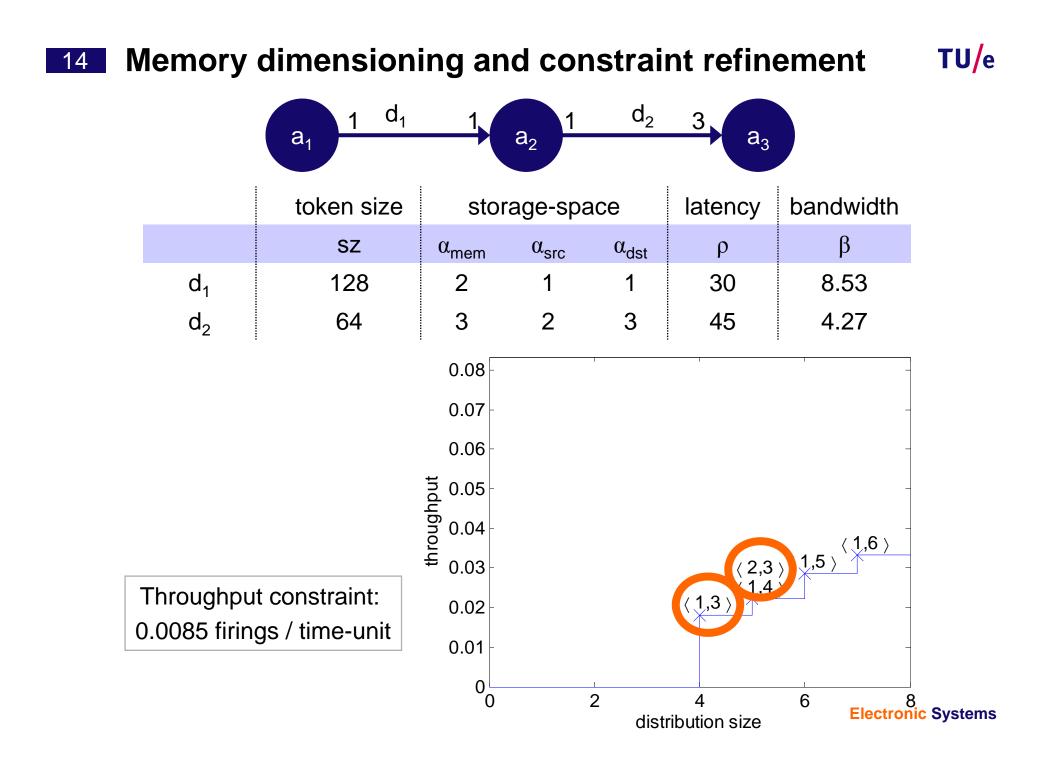

### **13** SDFG-based MP-SoC design-flow

TU/e

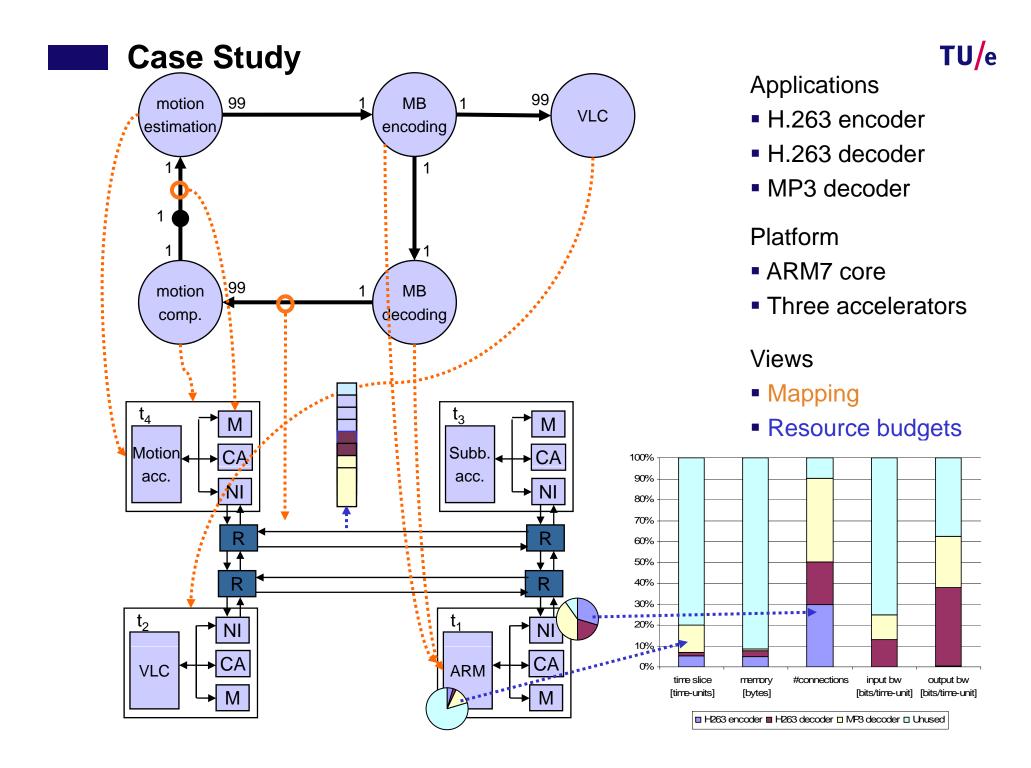

#### **17** SDFG-based MP-SoC design-flow

#### Case study

| H.263 encoder | H.263 decoder | MP3 decoder |

|---------------|---------------|-------------|

| 2ms           | 1611ms        | 143ms       |

| 1ms           | 0ms           | 1ms         |

| 287ms         | 816ms         | 55ms        |

| 125ms         | 261ms         | 5ms         |

| 415ms         | 2688ms        | 203ms       |

TU/e

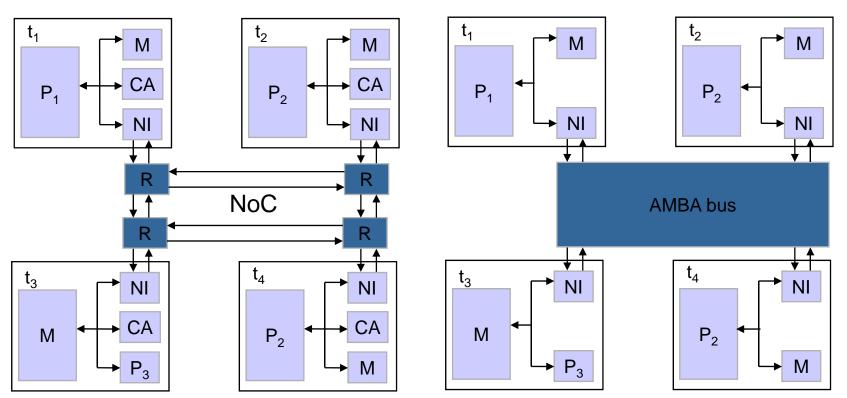

Design-flow supports two platforms:

- Network-on-Chip

- AMBA bus in combination with MP-Flow

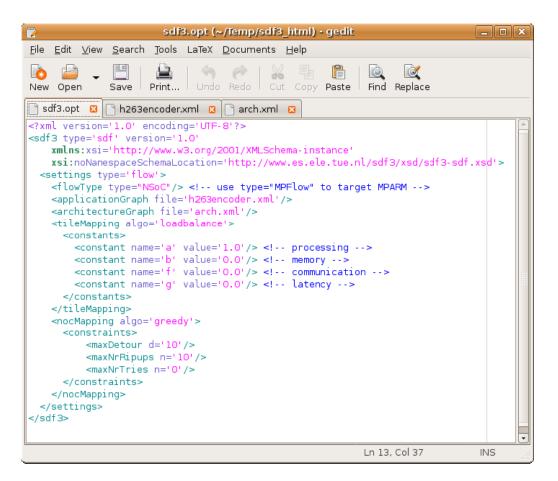

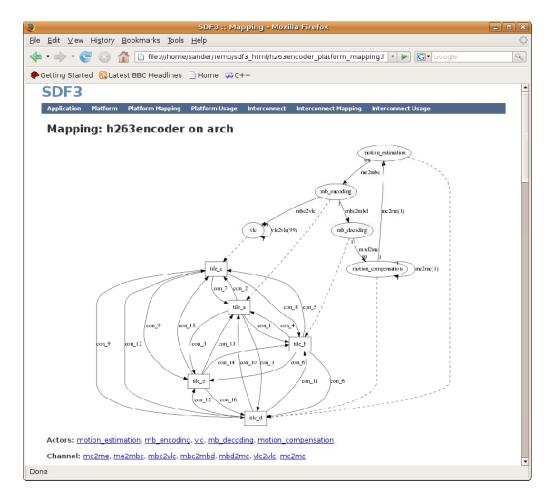

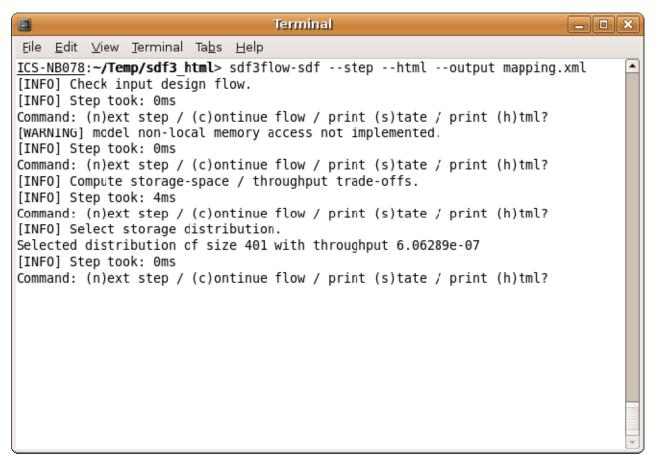

#### 21 SDF<sup>3</sup> interface

- Input/output of each step is described in XML

- XML can be transformed to HTML

- Command-line tool and C/C++ API available

#### TU/e

#### 22 SDF<sup>3</sup> interface

- Input/output of each step is described in XML

- XML can be transformed to HTML

- Command-line tool and C/C++ API available

#### TU/e

#### 23 SDF<sup>3</sup> interface

- Input/output of each step is described in XML

- XML can be transformed to HTML

- Command-line tool and C/C++ API available

#### 24 Concluding remarks

- MP-SoC design-flow and SDF<sup>3</sup> toolkit available at www.es.ele.tue.nl/sdf3

- First design-flow which maps SDFG to NoC-based MP-SoC

- Considers scheduling on processing, storage and communication resources

- Flow based on trade-offs between storage space, latency and bandwidth

- Most of the steps in the design-flow require milliseconds to complete for realistic applications