#### Verification of Redundant Architectures in AADL

UML & AADL Workshop 2009 June 2, 2009

Dio de Niz & Peter Feiler

Software Engineering Institute | Carnegie Mellon

© 2008 Carnegie Mellon University

## Problem

Redundant Architectures Used for Fault-Tolerance, but... Assume replicas "reactions" to faults/commands are synchronous

• E.g. primary switches to backup when backup to primary What effects do we want to tolerate

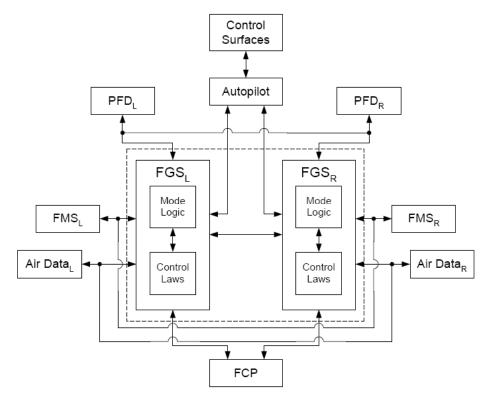

## **Dual Flight Guidance Systems**

#### Property 1

At least one FGS shall always be active

#### Property 2

• Exactly one side shall be the pilot flying side

#### Property 3

• If the system is in independent mode, both FGS shall be active

NASA/CR-2005-213912. S.P. Miller et al. "A Methodology for the Design and Verification of Globally Asynchronous / Locally Synchronous Architectures

**Carnegie Mellon**

# **NASA's Incremental Approach**

## Fully synchronous

## Asynchronous

- Mode-switching signal loss: previous active does not switch to inactive

- Fix: model acknowledgement & relaxing properties

- During mode transition : 2 pilots flying

## Asynchronous with failures

- Failure modeled as a signal to the still-active component

- Properties needed to relax to account for "failure discovery" time

- Issues:

- The introduction of a failure as a signal is unnatural to model

Software Engineering Institute

# **Suggestions on NASA Approach**

Use "proven" asynchronous / fault-tolerant constructs

• E.g. ack in a fault-tolerant communication

Better asynchrony modeling to avoid unbounded clocks

• Known period and drift

Modeling of mode synchronization should be part of system architecture and not component

Not include logic of component failure

Use patterns of common architectural features

## **Architectural Abstraction Approach using AADL**

Modality model at architectural level Evaluate expected synchrony between distributed modes Develop synchronous "expected" model Create new distributed architecture Evaluate all potential failures

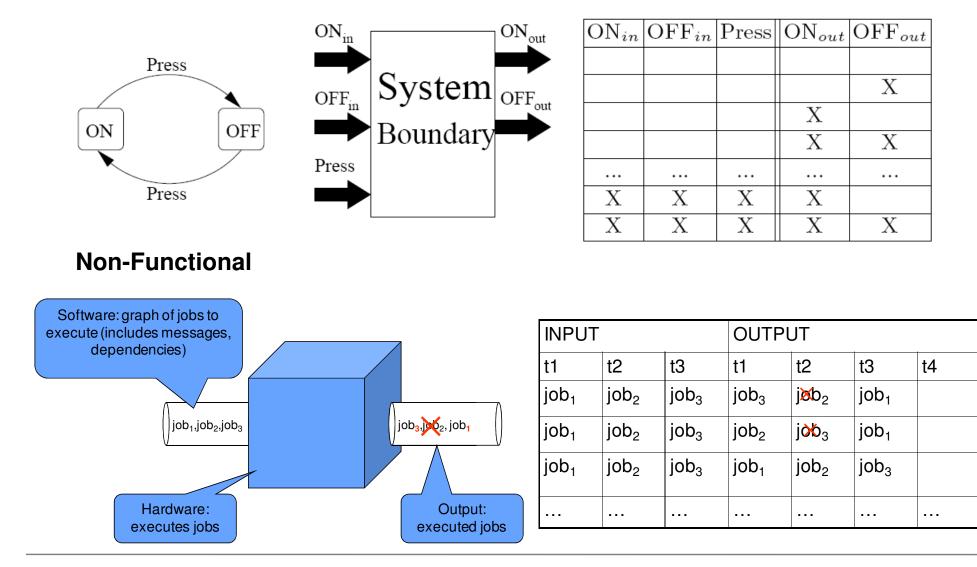

## From Chaos to Order

Non Functional Properties

## Systems modeled with two chaotic components

- Execution Platform (Executor)

- Software (Executable) Model all possible faults

- Executor

- Faulty execution

- Execution Reorder

- Executable: fault intolerant

Software Engineering Institute | CarnegieMellon

## Chaotic Model (Ormeier et al.)

Software Engineering Institute | Carnegie Mellon

# **Reducing Behaviors**

#### Hardware (Chaos)

- Rule out impossible behaviors

- Add hardware properties

- A single processor cannot execute two jobs at a time

- Add software structure

- E.g. Component does not execute until message delivered

## Software (Intolerance)

- Order of execution just need to honor precedence

- Some jobs may be optional

- Some messages can be lost

# AADL Model

Default model: all behaviors

**Reduce Software Intolerance**

flows:

f1: end to end flow t1.p1->t2.p1 {tolerate=>loss;};

#### Reduce Hardware Chaos

- bus: Bus {ensures => no\_loss;};

- Analysis of Architectural Differences in Alloy

- Base model assumed to be correct

- Modified model that can introduce problems

- New model with requirements from previous model

- Discover new not tolerated behaviors

Software Engineering Institute Ca

## **Consequences to Modes**

Redundant Architecture can mean synchronous modes

• E.g. when node1 in primary, node2 in backup

Loss of transition signal means modes out of sync Delayed transition means out of sync for a some time

- Out-of-sync modes

- Connections not active

- Duplicated connections

#### Synchronous Model (control flow)

thread implementation single.i

calls

s1:{

- cf: subprogram controller\_function;

- pf: subprogram primary\_function ;

- bf: subprogram backup\_function;

- p\_pbw: subprogram primary\_to\_backup\_waiting;

- b\_bpw: subprogram backup\_to\_primary\_waiting;

- p\_bpw: subprogram backup\_to\_primary\_waiting;

- b\_pbw: subprogram primary\_to\_backup\_waiting; auto: subprogram auto\_pilot;

};

#### end single.i;

#### Asynchronous Left (Primary) / Right (Backup)

thread implementation primary.i thread implementation backup.i calls calls s1: { s1: { pf: subprogram primary function; bf: subprogram backup function; } in modes (primary mode, backup mode); } in modes (backup mode, primary mode); s2: { s2: { p pbw: subprogram primary to backup waiting; b bpw: subprogram backup to primary waiting; } in modes (primary to backup synchronizing); } in modes (backup to primary synchronizing); s3: { s3: { p bpw: subprogram backup to primary waiting; b pbw: subprogram primary to backup waiting; } in modes (backup to primary synchronizing); } in modes (primary to backup synchronizing); connections connections c1: event port p pbw.switched mode -> out switched mode; c1: event port b bpw.switched mode -> out switched mode; c2: event port p bpw.switched mode -> out switched mode: c2: event port b pbw.switched mode -> out switched mode; c3: event port pf.outNav->outNav in modes (primary mode): c3: event port bf.outNav -> outNav in modes (backup mode); modes modes primary mod initial mode : primary mode: mode; primary to kup synchronizing: mode; primary to backup synchronizing: mode; hary synchronizing: mode; backup to primary synchronizing: mode; backup to backup mode: initial mode; backup mode : -[ transfer ]-> primary\_to\_backup\_synchronizing; primary backup mode - [transfer]-> backup to primary synchronizing; ckup synchronizing -[ in switched mode]-> backup mode; backup to primary synchronizing -[ in switched mode ]-> primary mode; primar -[ transfer]-> backup to primary synchronizing; back primary mode -[ transfer]-> primary to backup synchronizing; mary synchronizing - in switched mode -> primary mode; primary to backup synchronizing -[in switched mode]-> backup mode; bac end end backup.i; Modal connections Mode transition triggers

Software Engineering Institute

**Carnegie Mellon**

## **AADL Annotations**

#### Hardware

system implementation final.i

subcomponents

- cpu1: processor cpu {chaotic::Lossless => true;};

- cpu2: processor cpu {chaotic::Lossless => true;};

- cpu3: processor cpu {chaotic::Lossless => true;};

- cpu4: processor cpu {chaotic::Lossless => true;};

crnet1: bus net {chaotic::Lossless => true;};

crnet2: bus net {chaotic::Lossless => true;};

crnet3: bus net {chaotic::Lossless => true;};

crnet4: bus net {chaotic::Lossless => true;};

crnet5: bus net {chaotic::Lossless => true;};

## Software

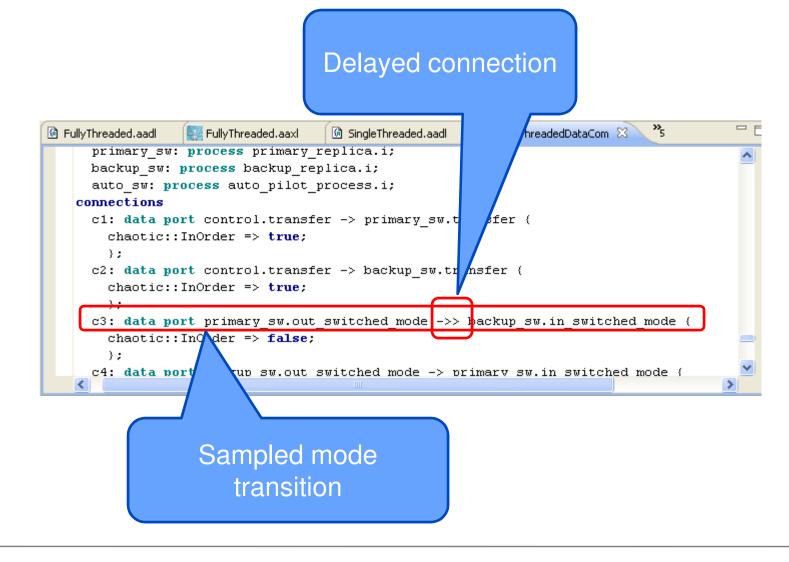

connections c1: event port control.transfer -> primary sw.transfer {chaotic::InOrder => true;}: c2: event port control.transfer -> backup sw.transfer {chaotic::ReorderTolerant => true; chaotic::LossTolerant => true;}; c3: event port primary sw.out switched mode-> backup\_sw.in\_switched\_mode

{chaotic::ReorderTolerance => 10 ms;}; c4: event port backup sw.out switched\_mode -> primary\_sw.in\_switched\_mode

{chaotic::InOrder => true;}; c5: event port backup sw.outNav-> auto sw.inNav {chaotic::InOrder => true;}; c6: event port primary sw.outNav->

auto\_sw.inNav {chaotic::InOrder => true;};

Software Engineering Institute

**Carnegie Mellon**

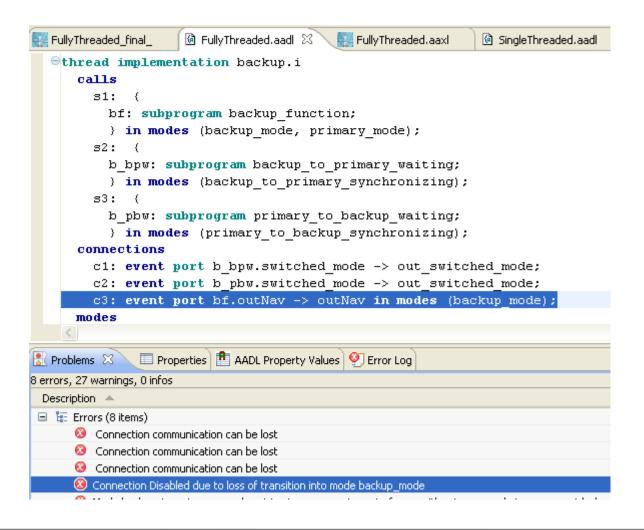

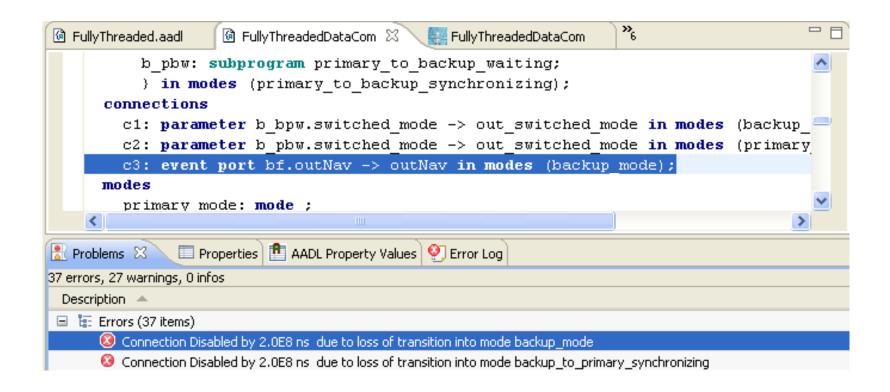

## **Mode Transition Loss**

Built-in acknowledge of mode transition

Mode loss due to network message loss

Automatically discovered "out-of-sync" modes

Automatically discovered connection loss due to "inactive" mode

• No output to autopilot

Software Engineering Institute

#### Loss of communication due to mode transition failure

**Software Engineering Institute** Carnegie Mellon

## **Out-of-sync modes**

| 🔛 FullyThreaded_final_ 🛛 🔞 FullyThreaded.aadl 🛛 🔛 FullyThreaded.aaxl       | 🙆 SingleThreaded.aadl         | » <sub>1</sub> |

|----------------------------------------------------------------------------|-------------------------------|----------------|

| end primary_replica;                                                       |                               |                |

|                                                                            |                               |                |

| <pre></pre>                                                                |                               |                |

| p: thread primary.i;                                                       |                               |                |

| connections                                                                |                               |                |

| c1: event port transfer -> p.transfer;                                     |                               |                |

| c2: event port in switched mode -> p.in switched mode;                     |                               |                |

| c3: event port p.out_switched_mode -> out_switched_mode;                   |                               |                |

| c4: event port p.outNav->outNav;                                           |                               |                |

| end primary replica.i;                                                     |                               |                |

| one prindry_repriod.ry                                                     |                               |                |

| ⊖ <b>process</b> backup replica                                            |                               |                |

| features                                                                   |                               |                |

| transfer: in event port;                                                   |                               |                |

| in switched mode: in event port;                                           |                               |                |

|                                                                            |                               |                |

| 🖹 Problems 🛛 🔲 Properties 🏥 AADL Property Values 🥺 Error Log               |                               |                |

| 8 errors, 27 warnings, 0 infos                                             |                               |                |

| Description 🔺                                                              |                               |                |

| 🖃 🔚 Errors (8 items)                                                       |                               |                |

| 😣 Connection communication can be lost                                     |                               |                |

| Onnection communication can be lost                                        |                               |                |

| 8 Connection communication can be lost                                     |                               |                |

| Onnection Disabled due to loss of transition into mode backup_mode         |                               |                |

| Mode backup_to_primary_synchronizing in component p out of sync with prima | ry_mode in component b due to | o message loss |

**Software Engineering Institute** Carnegie Mellon

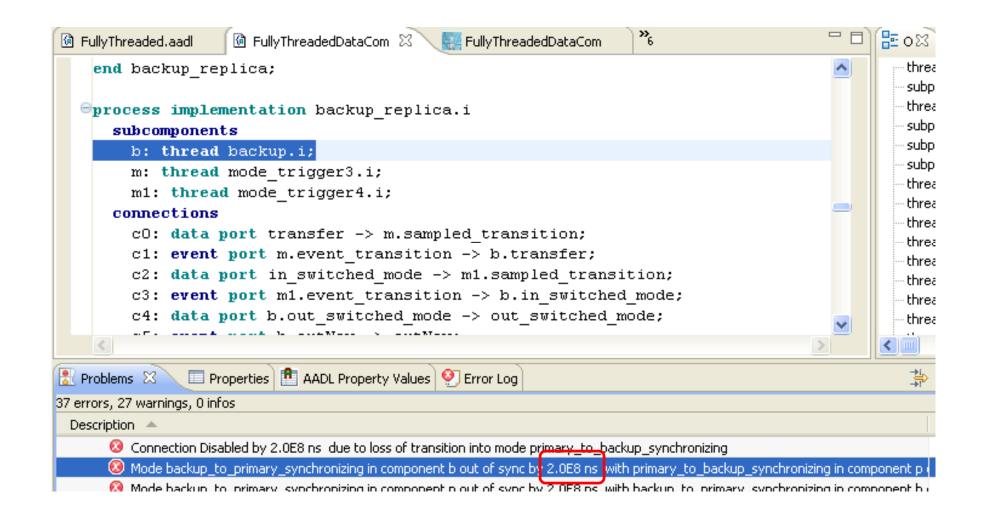

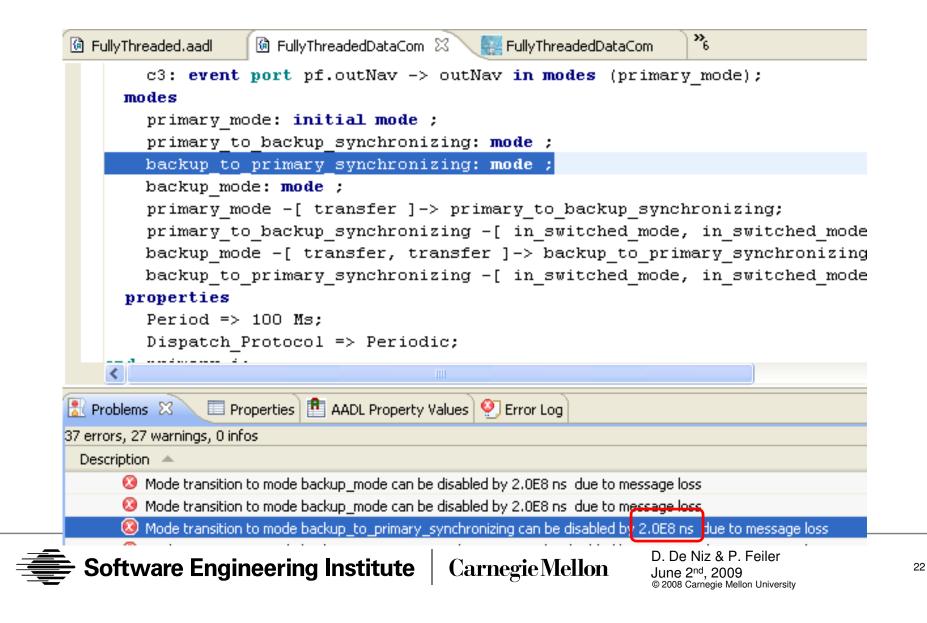

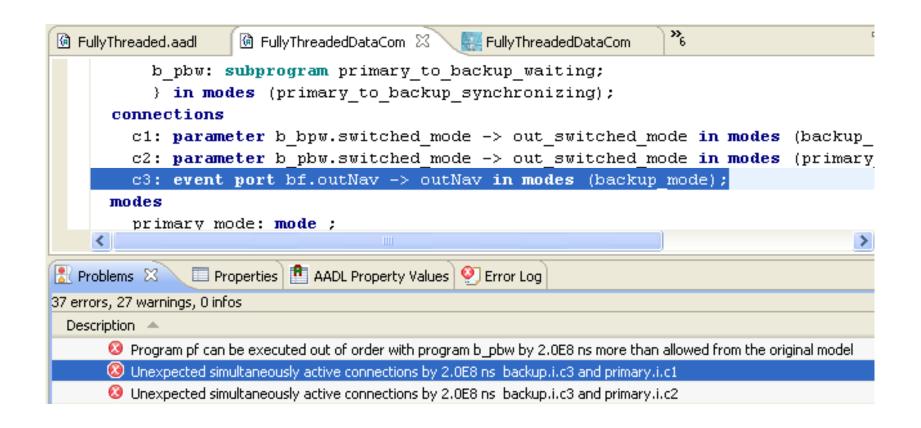

## Quantifying out-of-sync errors

Separate loss from out of sync

Out of sync modes happens due out of sync communication/execution

Sampled communication

Modeled in AADL as sampled data communication

Software Engineering Institute

# **Sampled Data Communication**

## **Quantified Out-of-sync Modes**

Software Engineering Institute Carnegie Mellon

## Mode Transition Disable Period

Quantified delay (instead of "communication step")

Bounded due to periodicity of threads

# Precise worst-case calculation of communication interruption / duplication

Software Engineering Institute | C

## **Mode Transition Delay**

## **Worst-Case Communication Interruptions**

## **Worst-Case Communication Duplication**

Software Engineering Institute Carnegie Mellon

# **Concluding Remarks**

Analysis of Concurrency in AADL model leverages semantics of AADL

- Processor bindings, failing processors,

- Duration of errors

Keeps analysis at architectural level

Focuses on problems introduced by the runtime architecture