Year 2 (Jan-Dec 2009) D16-(7.3)-Y2

IST-214373 ArtistDesign Network of Excellence on Design for Embedded Systems

Transversal Activity Progress Report for Year 2

# Transversal Activity: Industrial Integration

Transversal Activity Leader: Professor Alberto Sangiovanni Vincentelli, Trento

http://www.eecs.berkeley.edu/~alberto/

Policy Objective (abstract)

Each of the ArtistDesign Thematic Clusters (WP3-WP6) is important *per se* for advancing the state-of-the-art in embedded system design. However, if we wish to have a strong impact on industry and society at large, the results of the thematic clusters have to be harmonized in an overall design flow that can sustain the industrial embedded design chain from conception of the product to its implementation. This transversal activity is intended to define design flows and methodologies for two or three industrial segments leveraging the research carried out in the Thematic Clusters. This deliverable summarizes the achievements of the activity during Y2 of ArtistDesign.

# Versions

| number | comment                                  | date                           |

|--------|------------------------------------------|--------------------------------|

| 1.0    | First version delivered to the reviewers | December 18 <sup>th</sup> 2009 |

# **Table of Contents**

| 1. Ov | verview                                                                | 4  |

|-------|------------------------------------------------------------------------|----|

| 1.1   | High-Level Objectives                                                  | 4  |

| 1.2   | Industrial Sectors                                                     | 6  |

| 1.3   | Main Research Trends                                                   | 6  |

| 2. St | ate of the Integration in Europe                                       | 9  |

| 2.1   | Brief State of the Art                                                 | 9  |

| 2.2   | Main Aims for Integration and Building Excellence through ArtistDesign |    |

| 2.3   | Other Research Teams                                                   | 11 |

| 2.4   | Interaction and Building Excellence between Partners                   | 11 |

| 2.5   | Interaction of the Transversal Activity with Other Communities         | 12 |

| 3. Sı | ummary of Activity Progress                                            | 13 |

| 3.1   | Technical Achievements                                                 |    |

| 3.    | 1.1 General Frameworks for System Level Design                         | 13 |

| 3.    | 1.2 Automotive Applications                                            | 14 |

| 3.    | 1.3 Applications to Chip Design                                        |    |

| 3.    | 1.4 Application to Smart Energy Efficient Buildings                    | 22 |

| 3.    | 1.5 Application to Wireless Communication                              | 23 |

| 3.    | 1.6 Timing Analysis/Predictability                                     | 24 |

| 3.    | 1.7 Other System Applications                                          | 24 |

| 3.2   | Individual Publications Resulting from these Achievements              | 27 |

| 3.3   | Joint Publications Resulting from these Achievements                   |    |

| 3.4   | Keynotes, Workshops, Tutorials                                         | 31 |

| 4. Ov | verall Assessment and Vision for the Transversal Activity              |    |

| 4.1   | Assessment for Year 2                                                  |    |

| 4.2   | Overall Assesment since the start of the ArtistDesign NoE              |    |

| 4.3   | Indicators for Integration                                             |    |

| 4.4   | Long-Term Vision                                                       |    |

| 5. W  | ork Related to the Joint Programme of Integration Activities (JPIA)    | 40 |

| 5.1   | Joint Technical Meetings                                               |    |

| Meeting: Workshop: Smart and Efficient Energy Council SEEC-09, | 41 |  |

|----------------------------------------------------------------|----|--|

| Trento, October 8-9, 2009                                      | 41 |  |

| Meeting: Workshop: Workshop on Software Synthesis - WSS'09     |    |  |

| 5.2 Staff Mobility and Exchanges                               |    |  |

| 5.3 Tools and Platforms                                        |    |  |

| 5.3.1 Tool or Platform: SymTA/S                                | 49 |  |

| 5.3.2 COS/                                                     | 50 |  |

| 5.3.3 Metropolis and Metro II                                  | 53 |  |

| 6. Transversal Activity Participants55                         |    |  |

| 6.1 Core Partners                                              |    |  |

| 7. Internal Reviewers for this Deliverable                     |    |  |

# 1. Overview

# 1.1 High-Level Objectives

Each of the ArtistDesign Thematic Clusters (WP3-WP6) is important *per se* for advancing the state-of-the-art in embedded system design. However, if we wish to have a strong impact on industry and society at large, the results of the thematic clusters have to be harmonized in an overall design flow that can sustain the industrial embedded design chain from conception of the product to its implementation.

The chains vary in length and players according to the industrial segment addressed: for example, the design chain in automotive electronics starts with the car maker (e.g., BMW, Daimler Chrysler, Peugeot, Fiat), goes through the Tier 1 suppliers (e.g., Contiteves, Bosch, Magneti Marelli) and connects to the Tier 2 suppliers (e.g., FreeScale, ST, Infineon, Hitachi). It often includes IP providers such as programmable cores, RTOS and software development tool providers and design service companies. In the mobile communication domain, the chain starts with the application developers (e.g., gaming and video content), includes the telecommunication operators (e.g., Telecom Italia and Telefonica), the device makers (e.g., Nokia and Ericsson), the silicon makers (e.g., TI, Qualcomm and ST) and outsourcing manufacturing companies (e.g., Flextronics).

Today, there is stress in the chain as the technology advances may create opportunities to redefine the roles of the various players. In addition, the system integrators are often faced with an almost impossible task of composing their design out of parts supplied by companies whose design methods and standards are widely different and about which they have limited or no information. There is a need for an all-encompassing approach to system design that can make an entire industrial segment work as a virtual vertically integrated company. The benefits of these flows and methods are obvious as they provide shorter time to market and better quality designs but require a will of the industrial segment to work together towards this goal. In the automotive domain, Autosar is an excellent step in that direction. Other industrial segments are less cohesive in searching for a unified approach to design. In addition, society concerns such as energy, health and environment conservation, are offering new business opportunities for emerging technologies such as wireless sensor networks. The difficulty in these new opportunities resides in lack of standards and of experience with new communication concepts and, last but not least, in security.

We believe that all the thematic clusters bring something important to all industrial segments, but we need to pay attention to the way the results obtained by the clusters are formulated. Integration is a matter of modelling and providing interfaces that guarantee that the properties of the components are maintained after integration. Integration takes two forms: an horizontal one where different IPs coming from different companies or from different design groups in the same company have to be assembled; a vertical one, where the requirements are clearly and possibly formally communicated from a higher level player to a lower level one and where the information about the capabilities and limitations of the IPs are unambiguously communicated from the lower level to the higher level. The ultimate goal of this activity is to provide the "meta rules" according to which the design transformations are carried out and interfaces are built and hence to provide strong guidance to the clusters to make their results more relevant and applicable. Understanding the roles and dynamics of an existing, well-established, vertical industrial segment is a complex task. We could only imagine the complexity of industrial segments that are coming together in these years. While we do target some industrial domain to be the driver for this activity, we understand that our research is going to be more relevant

and better quality if we can distil some common traits of these domains and work with those to choose at a later date which particular chains to address.

The transversal activity hence has two prongs:

- to dive into particular vertical industrial segments and package design methods out of the thematic cluster results for the segments;

- to identify some important common features among verticals and work towards developing methods to address these topics.

We note that the two concerns objects of the Transversal JPRAs (**predictability** and **adaptability**) are common to almost all industrial concerns: For this reason, they provide a framework to start the work on integration driven by industrial applications. Predictability has been a goal since the beginning of the modern industry: predicting the capabilities of existing components allows to come to market faster with new products and prevents taking dead ends, predicting the effort needed to develop parts of the design and to integrate it correctly prevents early recalls and associated costs. The faster is the dynamics of the industry, the more important is to have predictability in design.

Adaptability is the property of a design to be adapted to changing environments and working conditions. Reconfigurability, programmability, dynamic restructuring are all facets of adaptability. Novel approaches to communication could benefit greatly from adaptability. In fact, much research is being carried out to design devices that could sense available bandwidth and adapt the communication protocol to the most convenient band at the time.

We believe that it will be eventually easier to compose the vertical design industrial flows once these two sub-flows have been examined and results obtained. In addition, being generic concerns they do not require effort from the academic partners to understand the *modus operandi* of entire industrial segments and offer a shorter time to results.

The vertical industrial segment motivated prong will begin by bringing up-to-speed the largest possible number of participants to the logic of the design chain by organizing workshops for discussion with the participants to the chain.

We proposed at the onset of the activity to target Automotive, Nomadic and Health Applications as potential vertical segments where we have a range of maturity from well-established (automotive) to emerging (health). At the 2008 meeting in Rome of the ArtistDesign partners, the three vertical markets of interest were identified as:

- 1. Automotive/avionics since we noted a strong similarity in the overarching issues faced by these two industrial segments that are driven by safety concerns and have to consider distributed implementations;

- 2. Health applications with particular emphasis on equipment design and manufacturing;

- 3. Energy efficient buildings, a novel field of great interest to the European Community as well as to the rest of the world as 30% of energy consumption is considered to be in commercial buildings.

These applications address an established area of excellence of European Industry where international competition is fierce, an area of growth where again European Industry has a strong position but where the dynamics are fast and new applications are envisioned in strategic areas such as elderly care, and a new area with great potential where energy conservation concerns are going to place a great political emphasis. Given the nature of this work, the main participants in the cluster are the groups that have industrial vocation such as ESI, OFFIS, and IMEC.

### -- Changes wrt Y1 deliverable --

No changes with respect to Year 1.

# 1.2 Industrial Sectors

This transversal activity is intended to funnel the results of the thematic clusters and of the other two transversal activities towards industry, thus maximizing the impact of DesignArtist findings. We expect the impact to be above and beyond the industrial segments identified above (automotive/avionics, health care and energy efficient buildings). In particular, we expect that the nomadic and consumer sectors be also impacted albeit some of the issues typical of these two vertical domains are substantially different from the others.

-- Changes wrt Y1 deliverable --

No changes with respect to Year 1.

# 1.3 Main Research Trends

The advancement of the embedded system research activities in Academia and research institutions has been gaining momentum over the past few years. Some industrial segments, typically avionics and automotive, have been also progressing in the use of tools and methodologies that have improved productivity and design quality albeit the advancements have not been uniform across companies and divisions inside the same company. In particular, model-driven design is becoming a standard. In this methodology, the design is captured and analyzed at the functional level with simulation tools and in some limited cases, with formal analysis techniques. The most used flow especially in the avionics/automotive domain is the Simulink Mathworks flow that uses Real Time Workshop (or dSpace, TargetLink) to generate implementation code on the most used single-processor platforms. Other industrial approaches are based on UML and the associated tools provided by IBM (Telelogic and Rational). There has been strong interest in defining UML profiles that are dedicated to real time embedded systems: in particular, SysML is gaining a broad attention. However, in both cases (but more visibly in the UML design flow), the semantics of the design has not been captured well enough to allow for formal analysis. The SPEEDS IP aims at improving substantially the quality of the embedded system design process by providing formal contract-based models that capture not only the functional aspects of the design but also the non functional ones such as power and timing with the Hierarchical Rich Component modelling approach. In this approach, the model can be mapped into the format accepted by advanced academic tools such as BIP so that formal analysis and simulation of the design can be carried out in a rigorous way. To capture the non functional aspects of the design novel timing analysis tools that are commercially available and that have been originally developed by ArtistDesign partners such as SymTA (Rolf Ernst) and AbsInt (Rheinhard Wilhelm), are being integrated into tool chains comprising model-based design tools, compilers, timing-analysis and schedulability tools. This tool integration will guarantee highest precision and thus avoid the need for over-commissioning.

We believe that the main issue is not one of modelling and tool usage but one of adopting and enforcing an appropriate methodology that could embrace advanced modelling and could use new generation tools. The aim of the transversal activity is indeed to study and propose to our industrial partners this approach. We do not expect to have an immediate success in having industry adapt the design flows since the tools and approaches are fairly sophisticated and require a quantum leap in the technical background of the designers.

The research trends in this domain is then to identify common layers of abstraction that favor the communication along the supply chain across company boundaries and the design chain inside each company. In addition, industry is pushing towards a better design capture methodology and formal model to allow for stronger verification and validation. In the case of the transportation and military industry, there is increased activity in design for certification. Certification is about design processes and not about the behavior of the artifact. We believe there will be a trend towards making the actual behavior of the artifact be certified which will in turn force companies to adopt rigorous methodologies for modeling and analysis.

Another important research trend to consider is how to accommodate the increased attention to energy efficiency. On October 21st, the US National Science and Technology Council (NSTC) released a report describing R&D activities that could decrease use of natural resources and improve indoor environments while reducing greenhouse gas emissions and other harmful pollutants from the building sector. The report, Federal R&D Agenda for Net-Zero Energy, High-Performance Green Buildings, was produced by the NSTC's Buildings Technology Research and Development Subcommittee under the auspices of the Office of Science and Technology Policy (OSTP) in the Executive Office of the President. Commercial and residential buildings consume about one-third of the world's energy. In particular, U.S. buildings account for more than 40 percent of total U.S. energy consumption, including 72 percent of electricity generation. If current trends continue, by 2025, buildings worldwide will be the largest consumer of global energy, consuming as much energy as the transportation and industry sectors combined. Building systems are characterized by uncertain process dynamics; time-varying behavior; multiple objectives (cost functions) that change over time (water usage for evaporative cooling, peak electrical power); and environmental effects (disturbances) such as ambient temperature and humidity, solar radiation, and user behavior. The challenges posed to the research community are large. The actual situation in bulding management is worrisome. The level of sophistication of building managers, of commissioning personnel and of building management companies is very low. Simple minded control laws are implemented on information systems that are under dimensioned with respect to the needs of a comprehensive design approach. The research agenda here is to the together the various aspects of building management, e;g., Heating, Ventilation and Air Conditions (HVAC), lighting and safety (fire and intrusion alarms, egress systems) into an integrated monitoring and control system. This action must include research on hierarchical multi-objective control, distributed system design, sensor and actuator selection and positioning. The systems must be adaptive, predictable and fault tolerant. The research agenda in the design and operation of energy efficient buildings is fully consistent with the thematic clusters and with the transversal integration activities. The role of industry here is very relevant as the important aspects to take into consideration when developing algorithms and methodology cut across multiple domains and company boundaries. The industrial landscape is moving at an interesting pace: players are repositioning to take advantage of the concerns dictated by the political climate on energy issues. For example, equipment companies are now setting up new system divisions to address the integration problems. This situation offers this transversal activity a unique opportunity to influence the way industry is looking at the problem. There is a new term being used in the research community interested in this area: systems of systems, meaning that the level of integration needed here is one or more levels above what has been done today in other industrial sectors such as automotive. In the October 2009 SEEC meeting, the activities in energy efficiency by the leading industrial concerns and by selected academic groups were reviewed and potential for future collaboration identified. The Workshop was considered to be a success by the participants and we had a strong mandate to continue organizing similar workshops in the future.

# -- Changes wrt Y1 deliverable --

The topic of energy efficiency and cyber-physical systems are coming rapidly to the center stage of the international research agenda and this is reflected in the activity that we have chosen to invest on.

# 2. State of the Integration in Europe

# 2.1 Brief State of the Art

As in the other transversal activities, it is almost impossible to provide a BRIEF state of the art of integration in Europe since this activity involves many different aspects in many different industrial segments. This transversal activity not only feeds from the thematic clusters but also from the other two transversal activities. Hence, the state of the art in each of the thematic clusters and transversal activities are propedeutic to this section and will not be repeated here.

In general, research activities tend to focus on specific problems and to develop techniques that are aimed at solving well defined aspects of these problems. This transversal activity is about integration at the industrial segment level transcending companies' boundaries and actually helping to integrate better the activities across the supply chain. In addition, the activity aims at providing inputs to the ArtistDesign community on how to interface methods and tools so that an overall methodology can be assembled. Today, integration at this level is vigorously pursued in Europe in some industrial segments (most notably the automotive domain) but it still needs years to come up with an agreed upon solution. In the energy efficient building domain achieving integration even inside single company boundaries is a difficult proposition. The potential impact of a research aimed at developing this overarching vision cannot be overemphasized. The objective is ambitious and it needs attention at the community level: a single research group does not have the breadth or the muscles to develop this vision.

The automotive industrial segment with the Autosar initiative has an important message about the integration of the design chain and advocates the adoption of standards in interfaces and operating systems. We actually believe that much more work needs to be done at the semantics level and at the non functional aspects of design. The work carried out in SPEEDS is an example of how to address these problems not only in the automotive domain but also in the avionics domain albeit limited to higher levels of abstraction. The CESAR Artemis project is about taking the work of SPEEDS to a new level of sophistication and to extend its reach to implementation issues. The large participation of industrial concerns in CESAR and SPEEDS that involve OEMs, Tier 1 suppliers and tool providers bodes well for the activity of this transversal activity.

The solidification of the Artemis JTI has been instrumental in driving the industrial interest in embedded systems. In particular, as quoted by the Artemis Web-site: "The European Union recognises the strategic importance of Embedded Computing Systems and has launched the Artemis Joint Technology Initiative (JTI). The ARTEMIS JTI is implemented as a Joint Undertaking (JU) which is a public-private partnership between:

- The European Commission

- Member States

- ARTEMISIA, a non-profit Industrial Association

ARTEMISIA is the ARTEMIS Industrial Association which represents the research community including Industry (large, small and medium sized companies), universities and research institutes. The ARTEMIS JU is an organisation based in Brussels that was legally established in February 2008 and it is managed by an Executive Director."

Hence the links of the ArtistDesign community to Artemis and Artemisia are of paramount importance for the development of the deliverables of the Industrial Integration Transversal Activity. In particular, the steering Board of Artemisia counts three of the ArtistDesign Partners (Joseph Sifakis (CEA), Luca Benini (U. Bologna) and Rudi Lauwereins (IMEC)) among the 5 research representatives. Alberto Sangiovanni Vincentelli is a member of the Public Authority

Board and the Governing Board of Artemis. We expect the ties with Artemis and Artemisia to grow stronger in the future

The German competence cluster SafeTRANS (Safety in Transportation Systems,) including ArtistDesign members TU Braunschweig and OFFIS, concentrates research and development expertise in Germany in the area of the design of complex embedded systems for transport systems, to develop in cooperation with leading companies in the transport industry methodologies and processes for the development of safety critical embedded systems within the framework of a mutual research strategy. SafeTRANS and the French Pôles de Compétitivité SYSTEM@TIC-PARIS-REGION and Aerospace Valley allied to form the European institute EICOSE (European Institute for Complex and Safety Critical Embedded Systems Engineering). In the meantime EICOSE has become the first »Innovation Cluster« within the technology platform ARTEMIS.

In September 2008, the new KTH Centre in Embedded systems - ICES, joining forces from several research groups at KTH and industry (ABB, Enea, Ericsson, Scania, Stoneridge and ÅF) was founded. Key goals of the centre include acting as a catalyst for improved interactions between academia and industry, and between the member companies. The centre has a focus on embedded systems engineering and science, emphasizing system design, architecture and methodology. For this reason, KTH has been added to the core team for the Transversal Activity. We expect major contributions from this team.

#### -- Changes wrt Y1 deliverable --

More emphasis has been given to the relationship with Artemis and Artemisia.

# 2.2 Main Aims for Integration and Building Excellence through ArtistDesign

This transversal activity is intrinsically about integration. Integration is across the various partners who are active in it as well as across the different thematic clusters and other transversal activities. Since our aim is about integration of other groups in ArtistDesign we are depending on the delivery of their findings to build an effective approach to the design integration across industrial segments. We also aim at integrating our work with the work in other industrial and academic communities. The interaction with US companies and research organizations is documented in the activity report about the Forum on CyberPhysical Systems where industry, academia, and government agencies came together to discuss how to approach the new generation challenges posed by the closer interaction between the physical world and computing. Also the topical event in Trento saw the participation of companies that are not (yet) in the ArtistDesign community as well as US companies who are interested in exchanging notes and results with our community.

The industrial integration activity is intented to last beyond the period in which ArtistDesign will be funded. It does have important links with large European projects (SPEEDS and CESAR) and with industry independently. Partners OFFIS, ESI, IMEC and Trento are directly connected with industry in deep ways. They will provide the backbone of the activity of industrial integration during the years.

#### -- Changes wrt Y1 deliverable --

No changes with respect to Year 1.

# 2.3 Other Research Teams

The main teams in Europe who are active in industrial flows are all included in ArtistDesign. Of course, the teams do not cover all industrial domains with the same intensity as automotive. The historical Artist group had had their main focus placed on embedded software. In ArtistDesign the periphery has been augmented to include some teams that have architecture, SoC and control expertise that are a necessary complement to the core strength to address the industrial integration issues. Connections to the HYCON NoE (<u>http://www.ist-hycon.org/</u>) were present via PARADES who coordinated the industrial integration of this NoE. However, people involved in industrial integration activities based on control such ETH's Morari and Lygeros are not present in ArtistDesign. HYCON ended its operation last year and in 2009 it has been transformed into HYCON II with similar group of partners. We do have strong relations with Manfred Morari and John Lygeros of ETH who are instrumental in defining the next generation distributed architecture for control applications including wireless sensor networks and we have leveraged this contact.

The communication field is a main focus of parallel groups in the US especially in the area of military applications sponsored by DARPA (e.g., UCLA (Estrin), Berkeley (Culler, Pister, Rabaey), Washington (Borriello)). In Europe, research in wireless sensor networks and their applications is carried out in several academic and industrial research groups. In particular, University of L'Aquila, Politecnico di Torino and TU Berlin

Research groups in the US that work on the issue of industrial integration among others are CHESS (Berkeley), GSRC (multi-university program sponsored by the Semiconductor Industry Association and DARPA), MUSYC (MultiScale System Center, a new MARCO Focus Research Center Program headquartered in Berkeley) and ISIS (Vanderbilt). Teams at CMU have strong industrial program that culminated with the victory of the DARPA Urban Challenge of the GM-CMU team. The double appointment of Alberto Sangiovanni Vincentelli with Berkeley offers an opportunity to link tightly with these groups. In addition, the COMBEST project whose partners are for the large part participating to ArtistDesign has an international collaboration also at the industrial level (for example, UTC, GM, Intel, National Instruments, Mathworks, and Cadence) so that proficuous interactions are guaranteed.

#### -- Changes wrt Y1 deliverable --

The HYCON NOE has ended its operation and will be replaced by HYCON II NOE that will remain in close contact with us.

# 2.4 Interaction and Building Excellence between Partners

The core groups are internationally renowned in their area of industrial interest. A change with respect to the original proposal occurred in January 2009 when PARADES withdrew from the ArtistDesign Consortium and it has been replaced by Trento. Alberto Sangiovanni Vincentelli transitioned from the PARADES to the Trento team to provide the continuity in the management of the JPRA.

All have multiple industrial segment contacts (transportation, IC, printing, health care, entertainment, consumer, nomadic, security, buildings). They act as agents of change and of

spread of excellence in the ArtistDesign community with respect to relation with industry. The interactions with the other clusters and transversal activities are at their inception. Since we selected the final focus area recently, we expect to engage the cluster partners with additional impetus. The active collaboration within this project has also led to the identification of common problems and goals between the partners and national and European companies. This leads to new joint undertakings e.g. within the Artemis framework.

# - Changes wrt Y1 deliverable --

A change with respect to Year 1 occurred in January 2009 when PARADES withdrew from the ArtistDesign Consortium and it has been replaced by Trento. Alberto Sangiovanni Vincentelli transitioned from the PARADES to the Trento team to provide the continuity in the management of the JPRA.

# 2.5 Interaction of the Transversal Activity with Other Communities

The partners for this activity are the majority of the partners in ArtistDesign. Their interactions with the communities are massive. Most of these interactions have been documented in the reports for the other sections. However, we would like to stress here the connection with HYCON that has not been reported elsewhere. The research communities that are connected with this activity include artificial intelligence, high-performance computing, wireless sensor networks, building optimization, IC design, and mechanical engineering. We are connected UC Berkeley, CMU, UCLA, Vanderbilt, University of Pennsylvania, Columbia University, Cadence, General Motors, Xilinx, Qualcomm, UTC and Stevens Institute in the US. In Asia, we are connected with Kyushu University, Hitachi, Toshiba, Panasonic, Samsung and Centre for Embedded Software Technology (CEST).

-- Changes wrt Y1 deliverable --

No changes with respect to Year 1.

# 3. Summary of Activity Progress

# 3.1 Technical Achievements

The technical achievements are collected under four major subheadings reflecting the nature of the contribution and the industrial sector being impacted: General Frameworks for systemlevel design; Applications to the Automotive Sector, Applications to Chip Design; Applications to Buildings; Applications to Wireless communication technology.

# 3.1.1 General Frameworks for System Level Design

# Platform-Based Design and Frameworks: Metropolis and Metro II

**Participants:** Cadence, Trento, UC Berkeley, Sun Microsystems, UTC, National Instruments and Intel.

System-Level Design (SLD) means many different things to many different people. In our view, system-level design is about the design of a whole that consists of several components where specifications are given in terms of functionality with additional:

- constraints on the properties the design has to satisfy and on the components that are available for implementation and

- objective functions that express the desirable features of the design when completed.

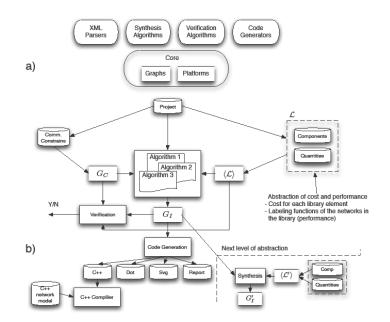

This definition is general since it relates to many different application domains, from semiconductors to systems such as cars and airplanes, buildings, telecommunication and biological systems. To deal with system-level problems, our view is that the issue to address is not developing new tools, albeit they are essential to advance the state of the art in design. rather it is the understanding of the principles of system design, the necessary change to design methodologies and the dynamics of the supply chain. Developing this understanding is necessary to define a sound approach to the needs of the system and component industry as they try to serve their customers better, to develop their products faster and with higher quality. This contribution was about principles and how a unified methodology together with a supporting software framework, as challenging as it may seem, can be developed to bring the embedded electronics industry to a new level of efficiency. To demonstrate this view, we first presented the challenges in design for the system of the future and a manifesto for the need of a unified methodology. We then summarized a methodology, Platform-Based Design (PBD), that has been developed over the past decade and that we believe can fulfil the needs. Further, we presented Metropolis, a software framework supporting the methodology and Metro II, a second generation framework built to alleviate the problems we encountered when applying Metropolis to industrial test cases. We concluded the paper with two test cases in two diverse domains: semiconductor chips (a UMTS single-chip design) and energy efficient buildings (an indoor air quality control system).

# Embedded systems challenges and focus areas

# Participants: KTH, ABB, Scania, Ericsson, ÅF, Enea, Stoneridge

During its first year of operation, the KTH Innovative Centre for Embedded Systems (ICES) has directed an effort to define the key focus of its activities. The Embedded systems area is wide, and there are also many possible activities which could be pursued by an embedded systems centre (ranging from continued education to research). In this first ICES Vision and Goals document, key challenges as perceived by the participating industries (telecom, automotive

and automation) and related scientific challenges are discussed. The guiding vision for ICES is established in the document: To achieve a flourishing eco-system for industry and academia excelling in embedded systems education, research and innovation. To reach this vision, ICES adopts the role of networker and catalyst with industry, KTH students and KTH faculty as the main stakeholders. The focal technical areas to be addressed by ICES are embedded systems architecture, software, verification and methodology. The Vision and goals document also defines concrete goals and activities for ICES the forthcoming years.

# 3.1.2 Automotive Applications

#### Dependable and Flexible Electrical Architecture 2020

#### Participants: Volvo car, KnowlT, Semcon, Mecel, Chalmers, Saab and KTH

This is a new automotive project, funded by the Swedish state, with the overall goals to suggest new embedded systems architectures that enable functional growth, are energy efficient and facilitate system verification. Topics of special concern include architecture evaluation methods, developing a reference architecture, model-based development methods, design for safety, and compliance with the upcoming safety standard ISO-26262. KTH has an industrial PhD student funded as part of the project, which connects well to KTH's ongoing research on architectural design, model-based development and design methodology.

#### Special Issue of the IEEE Trans on CAD on Automotive Applications

**Participants**: Trento, UC Berkeley, GM, TU Brauschweig, TU Vienna, Pirelli-Telecom Italia Berkeley Labs, Universitat des Saarlandes

Automotive systems are today the epitome of distributed complex embedded systems and, as such, offer an ideal domain to inspire research in methodologies and tools, as well as a rich test case for embedded system developers. The overall size of the software that is embedded in automobiles today is in the millions of lines of code, and it is forecast to significantly increase to accommodate additional functional content, from power train and chassis control, to infotainment. In addition to sheer software size, the complexity of automotive systems is constantly growing due to tight requirements for increased safety and performance, reduced pollution, and overall efficiency. Cost and time-to-market pressure pose additional burden to the designers for achieving an efficient use of system resources. Alongside the appetite for consumer electronics and communication devices that the car buyers are demonstrating, there is also a growing concern about the number of lives that are lost in our roads due to accidents. Both in the U.S. and Europe, regulatory pressures on safety are evident. Safety concerns are a major driving force for automakers. To cope with these problems, major advances are required at all levels in the architecture stack of automotive systems, from innovative chip architectures and sensors, to new standards for communications, to methods, tools, and standards for the development of middle-ware and application-level software components. One such advance is a fundamental shift in architecture design that is taking place. Today's automobile electronic systems are based on the concept of federated architecture, where each function is deployed to an autonomous electronic control unit (ECU), which is developed as a black-box integrated subsystem by Tier-1 suppliers. Because of the increased complexity and distribution of activesafety and future safety-critical functions, including by-wire systems, and the interdependence of these functions that gives rise to unexpected and undesired emerging behaviors, systems are becoming very difficult to test and validate. Furthermore, there is limited understanding of how to control the nonfunctional behavior of interacting modules, including timing and reliability properties emerging from the composition. Last but not least, the number of ECUs and busses is growing to unreasonable levels due to the need of accommodating new functionalities in the

federated architecture paradigm, causing cost and reliability problems. This situation has interested the automotive industrial sector to look at integrated architectures, in which software components can be supplied from multiple sources, integrated on the same hardware platform or physically distributed and possibly moved from one CPU to another without loss of functional and time correctness and providing a guaranteed level of reliability. This shift decouples software design from the hardware platform and provides opportunities for the optimization of architecture configuration, increased extensibility, flexibility, and modularity. ECUs can physically be integrated, with significant cost and dependability benefits and a reduction in the number of communication wires and connection harnesses. The possibility of defining components (subsystems) at higher levels of abstraction and with well-defined interfaces also allows separation of concerns and improves modularity and reusability. Methods and tools are needed for the design-time analysis of the result of the system-level integration, including the verification of safety constraints and, in general, the capability of predicting system-level functional, reliability, and timing properties. To discuss these trends and to provide a glimpse at the future of automotive systems, we organized with the support of ArtistDesign a full special day at the DATE 08 Conference as shown in last year report for WP4. This Special Section on Automotive Systems collects some of the presentations given at the special day [SVD09]. The papers in this Special Section address several problems in the architecture stack, from physical (sensor device) designs, to software architectures, to methods and tools for timing and performance analysis.

PAPER LIST

- 1. Sinem Coleri Ergen, Alberto Sangiovanni-Vincentelli, Xuening Sun, Riccardo Tebano, Sayf Alalusi, Giorgio Audisio, and Marco Sabatini, *The Tire as an Intelligent Sensor*

- 2. Roman Obermaisser, Christian El Salloum, Bernhard Huber, and Hermann Kopetz, *From a Federated to an Integrated Automotive Architecture*

- 3. Reinhard Wilhelm, Daniel Grund, Jan Reineke, Marc Schlickling, Markus Pister, and Christian Ferdinand, *Memory Hierarchies, Pipelines, and Buses for Future Architectures in Time-Critical Embedded Systems*

- 4. Simon Schliecker, Jonas Rox, Mircea Negrean, Kai Richter, Marek Jersak, and Rolf Ernst, System Level Performance Analysis for Real-Time Automotive Multi-Core and Network Architectures

# Model based engineering of automotive embedded systems, beyond Autosar

Participants: KTH, CEA, Volvo, CFR, TUB, Continental, Mentor, Univ. Hull, Mecel

As part of the FP7 ATESST2 project, technologies that complement Autosar - the automotive industry effort on software architecture - are being developed. The paper describes the EAST-ADL approach and how it complements Autosar. Autosar, is a large investment towards standardized automotive software platforms. An important role of Autosar is the strengthening the position of software development in the automotive industry. Autosar defines a complete software architecture and middleware that supports integration of third party software components into automotive electronic control units. While the standardization of software architecture is important, this does not however, solve the problems of dealing with requirements, product lines, mapping functions to software/hardware, and in meeting the needs of the upcoming safety standard, ISO26262. These goals correspond to the focal points in the ATESST2 project, where the EAST-ADL architecture description language, provides additional abstraction layers on top of Autosar and capabilities to reason about variability (product lines), and safety related issues. In addition, the TIMMO ITEA2 project, which has worked to establish complementary timing description techniques for Autosar, and ATESST2 have been carried out in close cooperation, such that results on timing descriptions for timing analysis are now fully integrated into the EAST-ADL.

# Optimizing the implementation of communication in synchronous reactive models with time constraints

# Participants: UC Berkeley, Trento, National Instruments

Model-based design methodologies are gaining attention in the industrial community because of the possibility of early and efficient functional validation and formal verification of properties at high levels of abstraction. The advantages of validating the design using high-level models can be lost entirely if errors and modifications that are not back-annotated to the higher abstraction levels are introduced when refining the design to lower levels of abstraction. To overcome this problem and to reduce design time, automatic synthesis has been used for the refinement process from Register Transfer Languages to logic gates for digital circuit design. This approach guarantees (assuming that the synthesis algorithms are correctly implemented) that the semantics of the RTL description are semantically equivalent to the semantics of the logic circuit. Automatic code generation is similar in intent and applicability. However, the software implementation of the abstract model must make efficient use of the platform resources that may not reflect all the assumptions of the code generation algorithms. The implementation of communication in a synchronous reactive model requires buffering and access procedures at the kernel level. In previous work, we obtained tight bounds on the size of communication buffers to maintain semantics equivalence. In real-time systems, however, because of the longer execution times of access procedures, an implementation with minimum buffer size may lead to the violation of deadlines. To solve this problem, we proposed a Mixed Integer Linear Programming (MILP)-based optimization approach that provides the minimum memory implementation of a set of communication channels while guaranteeing that the task deadline constraints are met [WDSV09]. The analysis is validated by an OSEK/VDX-compliant implementation that provides an estimate of actual run-time overheads. The approach is applied to a set of task graphs and an automotive case study.

# Automatic Code Generation for Synchronous Reactive Communication

Participants: National Instruments, UC Berkeley, Trento, The Mathworks

Synchronous Reactive models are used in Model-Based Design to define embedded control applications. The advantage of Model-Based Design is that system properties can be verified on the model and apply to its software implementation if the translation of the model into code preserves its semantics. In this paper, we presented an automatic code generation framework for the semantics-preserving implementation of communication in multi-rate systems. The proposed solution applies to the widely used MATLAB and Simulink products. It leveraged the Target Language Compiler template language of Real-Time Workshop and extended the applicability of available commercial code generators. The overhead in memory of the presented solution was analyzed and compared with other implementations.

# Optimizing Extensibility in Hard Real-Time Distributed Systems

# Participants: Intel, UC Berkeley, Trento, UTC

Some applications such as the design of a car typically require upgrading an implementation platform to accommodate new functionality or to fix errors over a product life-time that may extend over a five year horizon. In this case, being able to adjust the design without undergoing a major re-design cycle is imperative for competitive advantage. We addressed the problem of defining the initial solution to the design problem so that it is as robust as possible with respect to addition of new tasks or modifications to existing ones. To do so, we introduce a robustness measure, the extensibility metric, and then develop an efficient algorithm that

optimizes this metric. In this paper, we focused on hard real-time distributed systems that collect data from a set of sensors, perform computations in a distributed fashion and based on the results, send commands to a set of actuators. The tasks must satisfy tight end-to-end deadline constraints. Extensibility is defined as the amount by which the execution time of tasks can be increased without changing the system configuration while meeting the deadline constraints. With this definition, a design that is optimized for extensibility not only allows adding future functionality with minimum changes, but is more robust with respect to the variance of task execution times. We considered systems based on run-time priority-based scheduling of tasks and messages. In particular, we assumed that input data (generated by a sensor, for instance) are available at one of the system's computational nodes. A periodically activated task on this node reads the input data, computes intermediate results, and writes them to the output buffer from where they can be read by another task or used for assembling the data content of a message. Messages - also periodically activated - transfer the data from the output buffer on the current node over the bus to an input buffer on a remote node. Local clocks on different nodes are not synchronized. Tasks may have multiple fan-ins and messages can be multi-cast. Eventually, task outputs are sent to the system's output devices or actuators. The extensibility optimization problem can be considered as part of the mapping stage in the Platform-Based Design (PBD) design flow, where the functionality of the design (what the system is supposed to do) and its architecture (how the system does it) are captured separately, and then "joined" together, i.e., the functionality is "mapped" onto the architecture. In the application, function blocks communicate through signals, which represent the data dependencies. The architectural description is a topology of computational nodes connected by buses. In this paper, buses and nodes can have different transmission and computation speeds. Mapping allocates functional blocks to tasks and tasks to nodes. Correspondingly, signals can be mapped into local communication or packed into messages that are exchanged over the buses. Task and message priorities are assigned and the mapping is performed in such a way that the end-to-end latency constraints are satisfied in the worst-case. Task allocation, signal to message packing, message allocation and priority assignment are the design variables considered in this paper that are chosen with the objective of optimizing task extensibility.

The first stage of the proposed algorithm is based on MILP programming, where task placement (the most important variable with respect to extensibility) is optimized within deadline and utilization constraints. The second phase features two heuristic algorithms, which iteratively optimize signal-to- message packing and priority assignment. This algorithm runs much faster than randomized optimization approaches (a 20x reduction with respect to simulated annealing in our case studies). Hence, it is applicable to industrial systems as the case studies, which are of size comparable with the typical case of deployment of a set of additional functionalities in a commercial car, demonstrate in the experimental section. The first case study is a set of active safety functions deployed on a vehicle bus-architecture, with 9 ECUs, 41 tasks, and 83 CAN signals. In this case, optimization takes less than 1800 seconds, compared to more than 12 hours needed by the randomized optimization method, with results of comparable quality. The second test case is a safety-critical distributed control system deployed within a small truck. The key features of this system are the integration of slow and very fast (power electronics) control loops using the same communication network. In this example, we are interested in redesigning an existing system to understand the effects of adding communication and computational resources to the system. The shorter running time of the proposed algorithm allows using the method not only for the optimization of a given system configuration, but also for architecture exploration, where the number of system configurations to be evaluated and subject to optimization can be large. A further advantage of an MILP formulation (even if used only for the first stage) with respect to randomized optimization, is the possibility of leveraging mature technology in solvers, the capability of detecting the actual optimum (when found in reasonable time), or, when the running time is excessive, to compute

at any time a lower bound on the cost of the optimum solution, which allows evaluating the quality of the best solution obtained up to that point.

# Statistical Analysis of Controller Area Network Message Response Times

#### Participants: UC Berkeley, GM, Trento

Modern automobile architectures are composed by tens of Electronics Control Units (ECUs) connected by several buses, most of which are Controller Area Networks (CAN). The availability of multiple ECUs can be exploited by distributing control tasks of one domain (for example, power train) to several ECUs. In this case, a number of distributed functions are assigned to multiple tasks executing concurrently on different modules and communicating via messages transmitted on CAN. Distributed functions include time-critical controls, but most often, also functions that are characterized by requirements for average performance together with hard deadline constraints (as for most active-safety functions) and functions with soft realtime requirements (controls for enhanced driver comfort). The definition of a new architecture framework for one or more car product families is an extremely important step: ECUs, networks and the topology of connections must be defined and frozen years in advance of production. Later, during the architecture lifespan, functions are placed on ECUs and communication scheduled on the bus. This paper [ZDGSV09] presented a statistical approach to the early evaluation and selection of distributed embedded architectures for next-generation automotive controls, where the application performance depends on the end-to-end latencies of activesafety functions. Automobile architecture must be evaluated and selected having in mind that they will have a lifespan of 5 to 10 years and that during this lifespan the communication and computation load is partly unknown because new functions are still being decided on and have not been designed as yet. Hence, when verifying that the architecture is sufficiently robust with respect to constraints on latency and performance targets of present and future functionalities. loads can only be roughly estimated by looking at past trends or by exploiting early indications of designers. In this paper, we considered an application model that is currently deployed in GeneralMotors E/E architectures and is supported by the AUTOSAR standard. We described the use of statistical analysis to compute the probability distribution of Controller Area Network (CAN) message response times when only partial information is available about the electrical architecture of a vehicle as well as about its functionality. We provided results that showed our statistical inference allows predicting accurately the distribution of the response time of a CAN message, once its priority has been assigned, from limited information such as the bus utilization of higher priority messages.

This publication obtained the best paper award at the IEEE Symposium on Industrial Embedded Systems.

#### Optimizations of an application-level protocol for enhanced dependability in FlexRay

#### Participants: Trento, UC Berkeley, GM

FlexRay is an automotive standard for high-speed and reliable communication that is being widely deployed for next generation cars. The protocol has powerful error detection mechanisms, but its error-management scheme forces a corrupted frame to be dropped without any notification to the transmitter. In this paper, we analyzed the feasibility of and proposed an optimization approach for an application-level acknowledgment and retransmission scheme for which transmission time is allocated on top of an existing schedule. We formulated the problem as a Mixed Integer Linear Programming one. The optimization is comprised of two stages. The first stage optimizes a fault tolerance metric; the second improves scheduling by minimizing the latencies of the acknowledgment and retransmission messages. We demonstrated the effectiveness of our approach on a case study based on an experimental vehicle designed at General Motors.

# 3.1.3 Applications to Chip Design

# UMTS MPSoC Design Evaluation Using Metro II

#### Participants: Trento, UC Berkeley, Intel

In the race for higher performance computing, multi-processor platforms offer flexibility and a wide range of alternative design solutions that are able to optimally trade-off the design metrics of interest. This is especially true for embedded applications, often faced with hard to satisfy real-time and energy requirements which are best addressed by a distributed implementation. This trend is also apparent in the design of modern microprocessors, where the use of multithreaded cores is favored over faster clocks to speed up the software execution. The design of multi-core architectures is, however, made complex by a large design space, the difficulty of integrating heterogeneous components, and time-to-market pressures. We argued that only with a coherent and general design methodology can we address all these challenges. The methodology should be applicable during all phases of the design process from specification to implementation, it should support the design chain across divisional and company boundaries. it should favor re-use at all levels of abstraction and should be based on rigorous semantics foundations. Platform-based design (PBD) was developed with these goals in mind. A methodology can be applied even in the absence of supporting tools and flows. However, there is no question that the full leverage of the principles can be achieved only with appropriate design software. In this contribution [DSDP09], we discuss the use of a new event-based design framework. Metro II as presented above, for the simulation and design of multiprocessor platforms and present a non-trivial UMTS case study to show the results that can be obtained from architecture exploration. In particular, we show that this approach may be used to carry out quick design space exploration with accurate, low-overhead simulation.

# A Methodology for Constraint-Driven Synthesis of On-Chip Communications

#### Participants: Trento, UC Berkeley, University of Columbia, UTC

With the advances of IC technology, global interconnects have become the dominant factor in determining chip performance: they are not only becoming responsible for a larger fraction of the overall delay and power dissipation but exacerbate also design problems such as noise coupling, routing congestion, and timing closure, thereby imposing severe limitations on design productivity. Because of these characteristics, most VLSI circuits can be considered distributed systems, a fact that challenges traditional design methodologies and the electronic design automation tools that are based on them. Systems-on-Chip (SoCs) are typically designed by assembling intellectual property (IP) components from different vendors and/or different divisions of the same company in the attempt of reducing time-to-market by reusing pre-designed and pre-verified elements. However, since these components are designed independently, the assembly step is often a challenging problem that requires the design of communication interfaces to match different protocols and data parallelism, and the routing of global interconnect wires to meet the constraints imposed by the target clock period. Borrowing from the communication networks literature, an NoC can be built through the combination of heterogeneous elements such as interfaces, routers, and links. The NoC design is a challenging problem because there are many degrees of freedom (e.g. network topologies, routing protocols, flow-control mechanisms, positions of the communication components and core interfaces) as well as multiple optimization goals (e.g. performance, power, area occupation and reliability). Hence, the problem had been simplified by limiting the number and types of components considered, by focusing on a subset of the relevant objectives, by constraining NoC topology and components positions, and by dividing the optimization process in successive stages. Limiting the degrees of freedom has also the important side effect of reducing implementation and layout complexity. While a rich set of interesting results exists in the literature, few are the examples of practical applications of NoCs. In fact, the debate

between those who favor standard bus architectures or variations thereof and those who advocate the adoption of NoC approaches ranging from constrained architectures to custom ones is vibrant. We do not take sides even though the NoC approach has undisputable fundamental merits that may make it successful in the long run. Instead, we propose a general methodology for the design of on-chip communication that can explore a large number of alternatives including as special cases NoCs, bus architectures and hybrid ones. Thanks to its generality our approach can be used to build a framework where different constrained solutions are compared using a number of evaluation factors. We addressed the synthesis of optimal heterogeneous networks by assembling components from a fine-grained library without enforcing any constraint on their topology other than the ones formally captured in the library. In particular, the network that we obtained need not be direct and not even connected if these constraints are not captured in the composition rules of the communication components.

# Reliability Analysis with mixed-criticality workloads (see also Activity Report Hardware And MpSoC Design

#### Participants: TU Braunschweig, Toyota-ITC, Symtavision

In 2008 a research trilateral cooperation between TU Braunschweig, Toyota Information Technology Center (T-ITC), and Symtavision GmbH has been initiated, investigating the effects of errors on reliability and safety of real-time networks. Some of the results have been published in 2009 [SE09a], [SE09b].

A follow-up project has been started in 2009. In this context special focus has been put on reliability analysis for the CAN protocol, with special emphasis on the design of mixed criticality bus configurations. In this context several extensions of the analysis methodology have been developed. While the original approach addresses the occurrence of single bit errors only without any consideration of error correlations, in 2009 models have been proposed to describe interdependencies between errors, especially the occurrence of burst errors. Additionally analysis algorithms have been developed to integrate the burst error models into the original analysis approach.

Another subject of interest in this project is the extension of the message release model, which has been restricted to strictly periodic activations so far. The inclusion of release jitter enables the approach to be applicable to a wider variety of systems. For that purpose the analysis has been extended such that activation patterns with jitter can be incorporated.

#### Methods, Tools, and Platforms for cost-efficient certification of safety-critical multicore systems

**Participants:** TU Braunschweig, Intel, Infineon, Sysgo, Elektrobit, EADS IW, Delphi, TÜV Nord, and others

RECOMP is an ongoing project proposal submitted in response to the second call for proposals of the European JU Artemis. The goal of RECOMP is to develop methods, tools and platforms for enabling cost-efficient certification and re-certification of safety-critical multi-core systems, with special emphasis on the design of mixed-criticality systems. Additionally the integration of the developed techniques should be integrated into certification processes for different domains such as avionics, automotive or industrial automation. Commonly used safety standards for single-core systems like IEC 61508, ISO 26262 or DO 178B will provide the base for the certification of mixed-criticality multi-core systems. To enable the coverage of the complete safety-related development process a large consortium has been established to address most of the upcoming challenges. For example the consortium contains hardware (e.g. Intel, Infineon) and software (e.g. Sysgo, Elektrobit) vendors, system integrators (e.g. EADS IW, Delphi), certification authorities (TÜV Süd) and several research institutions.

# Multi-processor design technology

Participants: IMEC, Toshiba

IMEC has extended in 2009 the research collaboration with Toshiba in the field of MPSoC mapping tools and flexible, energy efficient processors for MPSoC.

http://www2.imec.be/imec\_com/adres-reconfigurable-processor-template.php

http://www2.imec.be/imec\_com/imec\_\_08217\_s-multi-threaded-adres-processor-architectureready-for-licensing.php?year=2009&month=10

#### Component-based service model

# Participants: DTU, B&O ICEpower

DTU and B&O ICEpower have continued the development of a modelling framework for system level performance estimation of embedded systems including Multi-Processor System on Chip (MPSoC) based configurations. The overall goal is to provide a framework which supports models described at multiple levels of abstraction which will allow designers to perform design space exploration at the various design stages ranging from initial high level specifications to detailed, bit true cycle accurate models.

During year 2, several refinements of the framework has been carried out resulting in minor changes of the modelling methodology. Substantial time and effort has been spent on this refinement implementing the changes in the current implementation of the framework. Also, a lot of time and effort has been put into the definition of a language used to specify models and automatically synthesize fast simulation models based on the specification. This shows promising results but is still work in progress. During year 2 DTU and B&O ICEpower has worked on an elaborate case-study, which has resulted in two publications [THM09a,THM09b].

# 3D Stacked IC Design using Through Silicon Vias - TSVs

#### Participants: IMEC, Qualcomm, Javelin

IMEC and Javelin developed in close collaboration with Qualcomm, a partner in IMEC's 3D integration program, 3D PathFinding toolflows, which extend the Javelin PathFinding methodology and j360 Silicon PathFinder platform to support virtual chip design for cooptimization of system design and 3D interconnect-packaging technologies. Designers of 3D ICs can use it to rapidly explore many potential 3D design implementations for their technical value propositions, and to identify and mitigate risks-benefits and optimize value.

http://www2.imec.be/imec\_com/javelin-design-automation-and-imec-extend-javelin-pathfindingdesign-technology-for-3d-stacked-ics.php?year=2009&month=02

# Memory Aware Variability Modeling (VAM) for embedded SRAMs

# Participants: IMEC, Samsung

IMEC successfully transferred MemoryVAM (Memory Variability Aware Modeling), the first EDA tool for statistical memory analysis, to Samsung Electronics. The tool predicts yield loss of SRAMs caused by the process variations of deep-submicron IC technologies. IMEC's MemoryVAM is an essential tool to avoid already at design time the most likely reasons for failure, anticipating and correcting weak design spots before tape-out, and hence avoiding redesign spins after processing. The tool also provides key help to memory and system designers to estimate yield loss due to changes of for example cycle time, access time and power consumption (static/dynamic) caused by process variations.

http://www2.imec.be/imec\_com/imec-transferred-design-for-manufacturing-tool-for-embeddedsrams-to-samsung-electronics.php?year=2009&month=04

#### **RF** Transceivers

# Participants: IMEC, Renesas

Renesas continued in 2009 the strategic research collaboration with IMEC in the field of nanoelectronics, to perform research on 45nm RF transceivers targeting Gbit/s cognitive radios. To this end, Renesas has joined IMEC's software-defined radio (SDR) front-end program. This research program includes reconfigurable RF solutions, high-speed/low-power analog-to-digital converters (ADCs) and new approaches to digitize future RF architectures.

http://www2.imec.be/imec\_com/renesas-collaborates-with-imec-on-reconfigurable-rftransceivers.php?year=2008&month=04

# 3.1.4 Application to Smart Energy Efficient Buildings

#### Energy-neutral distributed sensing for proactive energy management in buildings and plants

#### Participant: University of Bologna, Telecom Italia

University of Bologna has designed the Energy Harvesting circuit which is the core of the power supply unit of the wireless sensor nodes of the Kaleidos framework developed by Telecom Italia (the main telephone company in Italy). The collaboration deeply exploits wireless sensor networks and wireless actuators to improve and simplify industrial and service operations. To this goal Kaleidos is a middleware platform to collect data and provide anf efficient management of electricity consumption in telecommunication switching plants. University of Bologna provided technology for powering the sensors and recharging the batteries exploiting the electromagnetic fields in the cable grid and using the same AC current sensors used for measurements and data logging.

#### Warehouse of the future

#### Participant: ESI, Vanderlande Industries

The Falcon project, set up by the Embedded Systems Institute and Vanderlande Industries, aims at overcoming the weaknesses of the existing centralized warehouse control systems. This so-called "warehouse of the future" can be achieved by defining appropriate (software) architecture for warehouse and (quantitatively) showing that such architecture eliminates the weaknesses of the centralized warehouse control system. Existing warehouses are controlled by centralized control systems, which are typically built around a centralized database containing all knowledge of the warehouse status. These warehouse control systems allow a high system performance, because all optimization information is available in one place. An additional strength of these systems is the persistency of information, which is handled automatically by the database. On the other hand, the scalability of such warehouse control systems is limited, because all event handling involves accessing a central database. Moreover, these centralized control systems are difficult to maintain, because it requires detailed knowledge of warehouse status in order to achieve the desired performance. Similarly, it is difficult to reuse warehouse controller functionality for other warehouses.

A main result of the project is a framework that allows holonic warehouse control systems to be set up from a description of the available warehouse equipment and a library of agent behaviors. This framework has been applied to the Compact Picking System (CPS) of the Plus Retail warehouse in Middenbeemster, the Netherlands. Moreover, a holonic prototype of a

High-Density Storage (HDS) system is being developed. Results of this work been published in [MCV09].

# 3.1.5 Application to Wireless Communication

#### Ambient Living with Embedded Networks

#### **Participants**: ESI, Free University Amsterdam, Devlab (Eindhoven)

ESI has started to work in the ALwEN project (Ambient Living with Embedded Networks) on the combination of Body Sensors, Ambient Sensors, Wireless Networks and Telemedicine. The ultimate goal is a set of concepts and methods for a novel care approach that will be implanted in a new generation low-cost integrated circuit (IC) with embedded computation and wireless communication. Key to the success of Wireless Sensor Network applications is the right balance between overall system-level properties such as dependability, power consumption, network and application performance, and robustness to adverse operating conditions. ESI focuses on improving, understanding and predicting capabilities of these system level properties. ESI intends to develop system-level, multi-disciplinary models to predict overall-system level properties, with high fidelity in typical home, office, and care environments. These models will be used also by project partners in support for system design evaluation methods, and system configuration methods to be developed in this project. The results of this work so far have been published in [BNH09], [NBB09a], [NBB09b].

#### Future wireless communications

#### Participants: IMEC, Panasonic

IMEC has extended in 2009 the research collaboration with Panasonic in the field of green radios.

http://www2.imec.be/imec\_com/imec\_and\_panasonic\_sign\_comprehensive\_joint\_research\_co\_ntract.php?year=2008&month=11

# Green radio technology

#### Participants: IMEC, Samsung

IMEC collaborates in 2009 on technologies for green radios with Samsung. The research collaboration topics include cognitive reconfigurable radio baseband and millimeter-wave wireless communications technologies. Building on expertise in software-defined radios that support the major standards for wireless communications, IMEC pushes its research one step further towards cognitive radios (ICs with a radio that adapts itself to the changing environment, not only to the communication standard, but also to the available communication frequencies and conditions such as indoor/outdoor, signal strength, movement). IMEC is working on the control algorithms that take into account these changing environment parameters and user needs. As another cornerstone of its research into wireless communication, IMEC develops radio ICs for the wireless communication of massive data streams, for example for uncompressed high-definition television streams. Such data streams require a high throughput, in the order of Gbits per second. A suitable bandwidth for that communication is available around 60GHz. Therefore, IMEC works on cost-effective, low-power 60GHz radio ICs in standard CMOS, targeted at the consumer market,

http://www2.imec.be/imec\_com/samsung-electronics-joins-imec-research-program-on-greenradios\_\_\_\_php?year=2009&month=05

# 3.1.6 Timing Analysis/Predictability

#### Static Analysis of Synthesized Code

#### Participants: Universität des Saarlandes, AbsInt, Daimler

The analysis of code synthesised from high-level models often can be improved by utilising model information. For example, code synthesized from the automata component of models often has complex control flow, not easily amenable to existing static analysis tools. The control logic implemented in automata also governs the control flow through the surrounding parts of the model. Information about the reachable states can be used to exclude infeasible paths in the model, potentially reducing the computed worst-case execution time.

#### Identification of Operating Modes

#### Participants: Universität des Saarlandes, AbsInt, Bosch

Embedded control often works in different operating modes with different timing constraints. Determining the overall worst-case execution time would be pessimistic for some of the modes. One goal of the cooperation between Universität des Saarlandes, AbsInt and Bosch is the development of a mode-specific timing analysis. This would determine a worst-case execution time for each mode. However, operating modes currently are not explicitly specified and therefore neither visible on the model level nor on the code level. Designers of components typically know them, but have no way to declare them. Upon composition of the components, this information is completely lost for the integrated system. A first step therefore consists of an analysis of the system on the model and/or the code level to identify operating modes.

# 3.1.7 Autonomous systems - Generation of Correct-by-construction Code

#### Project: Goal-Oriented Autonomous Controller (GOAC)

#### Participants: UJF/Verimag, GMV, LAAS, ISTC-CNR

<u>Industrial Partner</u>: GMV is a CMMI 3 certified company that has more than 20 years of experience in the aerospace field. for the space and ground segment, and has developed very different types of systems (safety/mission critical/aid tools/simulators/web systems/robotics) using a number of technologies (Linux/Unix, Win-dows, C++, .NET, Java, Matlab, Fortran, C, Multi-agent systems) in developments of varying size (ei-ther large, medium or small) and complexity. GMV, as the prime contractor for the proposal, will be in charge of the integration of the software, and it will design, develop and implement the executive layer, and the global framework for the GOAC. GMV will also develop the second use case, and will perform the testing of GOAC. GMV is already involved EXOMARS as well as in the EUROBOT Ground Prototype projects.

<u>Application</u>: The Goal Oriented Autonomous Controller (GOAC) is an autonomous controller using a sense-plan-act paradigm to provide increasing levels of autonomy for robotic task achievement. GOAC will generate plans in-situ, will deterministically dispatch activities for execution and will recover from off-nominal conditions. Underlying GOAC is a rich representation that deals with metric time and resources necessary for dealing with planning and execution time uncertainty in dynamic environments. It comes with a lower-level functional layer that is tightly integrated with an abstract decisional level all of which have a rich operational legacy with deployments in real-world environments. The system's higher levels of abstraction deal with long-term mission plans that are deliberative; lower levels of abstraction are increasingly reactive. The functional layer is purely reactive with fast reaction times necessary for failure recovery and command dispatch. Additionally a Verification and Validation

system ensures compositional correctness by guaranteeing global system properties of system components.