# IST-214373 ArtistDesign Network of Excellence on Design for Embedded Systems

Workpackage Progress Report for Year 2

# Jointly-executed Programme of Integrating Activities (JPIA) Report

With input from all clusters.

Workpackage Leader:

Bruno Bouyssounouse (UJF/VERIMAG) http://www-verimag.imag.fr/~bouyssou/

#### Policy Objective (abstract)

Each ArtistDesign research activity has work within both the JPIA and the JPRA workpackages. The JPIA activities are carried out on a global, NoE level, transcending the clusters. They form the supporting background for integration of the NoE, and are executed in phase and in interplay with the JPRA research activities. For instance, funds for staff mobility will be allocated taking into account the needs for research.

The activities listed here will promote integration of geographically dispersed teams. All these activities will have long-lasting effects, well beyond the duration of the initial EC funding.

These activities include Joint Technical Meetings, Staff Mobility and Exchanges, Tools and Platforms.

### **Versions**

| number | comment                                  | date                           |

|--------|------------------------------------------|--------------------------------|

| 1.0    | First version delivered to the reviewers | December 18 <sup>th</sup> 2009 |

### **Table of Contents**

| 1. | Οv  | rerview of the Workpackage                                                 | 4  |

|----|-----|----------------------------------------------------------------------------|----|

| 1  | 1.1 | ArtistDesign Participants and Affiliated Partners                          | 4  |

| 1  | 1.2 | Starting Date, and Expected Ending Date                                    | 4  |

| 1  | 1.3 | Policy Objective                                                           | 4  |

| 2. | Joi | int Technical Meetings                                                     | 5  |

| 2  | 2.1 | Modelling and Validation Cluster                                           | 5  |

| 2  | 2.2 | Software Synthesis, Code Generation and Timing Analysis cluster            | 8  |

| 2  | 2.3 | Operating Systems and Networks Cluster                                     | 14 |

| 2  | 2.4 | Hardware Platforms and MPSoC Cluster                                       | 16 |

| 2  | 2.5 | Design for Adaptivity in Embedded Systems (Transversal Integration WP)     | 17 |

| 2  | 2.6 | Design for Predictability (Transversal Integration WP)                     | 19 |

| 2  | 2.7 | Integration Driven by Industrial Applications (Transversal Integration WP) | 20 |

| 3. | Sta | aff Mobility and Exchanges                                                 | 28 |

| 3  | 3.1 | Modelling and Validation Cluster                                           | 28 |

| 3  | 3.2 | Software Synthesis, Code Generation and Timing Analysis cluster            | 29 |

| 3  | 3.3 | Operating Systems and Networks Cluster                                     | 31 |

| 3  | 3.4 | Hardware Platforms and MPSoC Cluster                                       | 31 |

| 3  | 3.5 | Design for Adaptivity in Embedded Systems (Transversal Integration WP)     | 33 |

| 3  | 3.6 | Design for Predictability (Transversal Integration WP)                     | 34 |

| 3  | 3.7 | Integration Driven by Industrial Applications (Transversal Integration WP) | 34 |

| 4. | То  | ols and Platforms                                                          | 35 |

| 2  | 1.1 | Modelling and Validation Cluster                                           | 35 |

| 4  | 1.2 | Software Synthesis, Code Generation and Timing Analysis cluster            | 40 |

|    | 4.2 | 2.1 Tool or Platform: WCC                                                  | 40 |

|    | 4.2 | 2.2 MAPS                                                                   | 41 |

|    | 4.2 | 2.3 CoSy                                                                   | 42 |

|    | 4.2 | 2.4 ICD-C                                                                  | 43 |

| 4.2.5                  | MP-MH MPSoC parallelization assistant and memory hierarchy assignment for MPSo        | C44  |

|------------------------|---------------------------------------------------------------------------------------|------|

| 4.2.6                  | aiT                                                                                   | 45   |

| 4.2.7                  | Bound-T                                                                               | 45   |

| 4.2.8                  | SWEET                                                                                 | 46   |

| 4.3 Op                 | perating Systems and Networks Cluster                                                 | 47   |

| 4.3.1                  | Platform: Educational kit for Real-Time Embedded Systems                              | 47   |

| 4.3.2                  | Platform: RTNS simulation package                                                     | 48   |

| 4.4 Ha                 | ardware Platforms and MPSoC Cluster                                                   | 49   |

| 4.4.1                  | Tool: SymTA/S                                                                         | 49   |

| 4.4.2                  | Tool: Analysis and optimisation framework for fault tolerant distributed embedded sys | tems |

| 4.4.3                  | Tool: IMEC MPA + MH MPSoC mapping framework                                           | 51   |

| 4.4.4                  | Tool: MoVES - Modelling and Verification of Embedded Systems                          | 53   |

| 4.4.5                  | Tool: MPA (Modular Performance Analysis)                                              | 54   |

| 4.4.6                  | Tool: DOL (Distributed Operation Layer)                                               | 55   |

| 4.5 De                 | esign for Adaptivity in Embedded Systems (Transversal Integration WP)                 | 56   |

| 4.5.1                  | SWEET (SWEdish Execution Time tool)                                                   | 56   |

| 4.5.2                  | Multicore Partitioni                                                                  | 57   |

| <b>4.5.3</b><br>Syster | Hardware setup to demonstrate self-protection and adaptability of embedded Real-Tin   |      |

| 4.5.4                  | TrueTime                                                                              | 58   |

| 4.6 De                 | esign for Predictability (Transversal Integration WP)                                 | 60   |

| 4.6.1                  | Tool or Platform: aiT                                                                 | 60   |

| 4.6.2                  | Tool or Platform: aiT / WCC                                                           | 60   |

| 4.6.3                  | Tool: MPA (Modular Performance Analysis)                                              | 62   |

| 4.6.4                  | Tool or Platform : MPARM                                                              | 63   |

| 4.7 Int                | egration Driven by Industrial Applications (Transversal Integration WP)               | 63   |

| 4.7.1                  | Tool or Platform: SymTA/S                                                             | 63   |

| 4.7.2                  | COSI                                                                                  | 65   |

| 4.7.3                  | Metropolis and Metro II                                                               | 67   |

| 5. Asses               | sment of the Workpackage at the end of Y2                                             | 69   |

### 1. Overview of the Workpackage

-- Changes wrt Y1 deliverable --

No changes with respect to Year 1.

#### 1.1 ArtistDesign Participants and Affiliated Partners

Each ArtistDesign research activity contributes to achieving both research and integration goals. Thus, each has work within both the JPIA and the JPRA workpackages, and all partners and affiliated partners participate in the Joint Programme of Integration Activities.

#### 1.2 Starting Date, and Expected Ending Date

These activities are intimately related to the JPRA (Joint Programme of Research Activities) and run for the entire duration of the NoE.

#### 1.3 Policy Objective

The JPIA activities are carried out on a global, NoE level, transcending the clusters. They form the supporting background for integration of the NoE, and are executed in phase and in interplay with the JPRA research activities. For instance, funds for staff mobility will be allocated taking into account the needs for research.

The activities listed here will promote integration of geographically dispersed teams. All these activities will have long-lasting effects, well beyond the duration of the initial EC funding.

These activities include Joint Technical Meetings, Staff Mobility and Exchanges, Tools and Platforms.

### 2. Joint Technical Meetings

Joint Technical meetings aim to present, discuss and integrate the ongoing work, and exchange points of view with other teams. They also serve to identify future work directions.

They are often organized around the annual General Assembly and Review, or around some of the main conferences in the area (most of which are piloted by a majority of ArtistDesign partners).

Depending on the context and in particular on the maturity of the topics under discussion, these Joint Technical Meetings may be open to the public, or by invitation (which implicitly includes all interested ArtistDesign partners).

#### -- Changes wrt Y1 deliverable --

All new text: this entire chapter pertains only to activity in Year 2.

#### 2.1 Modelling and Validation Cluster

Workshop: ArtistDesign Workshop on Embedded Systems in Healthcare 2009 *Eindhoven, The Netherlands, 7 December 2009.*

The goal of the Workshop on Embedded Systems in Healthcare is to strengthen the connections between academic research and industry, or to be more precise, to increase the understanding in the academic world of industrial issues in embedded systems engineering and together come to a shared agreement on research directions that seem worthwhile to pursue. The speakers at the workshop work at different medical companies or are participants in the ArtistDesign network with extensive experience in healthcare. The topics include "How to design long lasting devices for a fast changing world?", "Cochlear Implant Systems: today's challenges in embedded firmware design", and "Embedded Contributions to an Intensive Care Safety Concept".

http://www.artist-embedded.org/artist/WESH-2009.html

Workshop: 2nd International Workshop on Model Based Architecting and Construction of Embedded Systems (ACES<sup>MB</sup> 2009)

ACM/IEEE 12<sup>th</sup> Int. Conf. on Model Driven Engineering Languages and Systems Denver, Colorado, USA – October 6<sup>th</sup>, 2009

The development of embedded systems with real-time and other critical constraints raises distinctive problems. In particular, development teams have to make very specific architectural choices and handle key non-functional constraints related to, for example, real-time deadlines and to platform parameters like energy consumption or memory footprint. In this context, the last few years have seen an increased interest in using model-based engineering (MBE) techniques. MBE techniques are interesting and promising for the following reasons: They allow to capture dedicated architectural and non-functional information in precise (and even formal) domain-specific models, and they support a layered construction of systems, in which the (platform independent) functional aspects are kept separate from architectural and non-functional (platform specific) aspects, where the final system is obtained by combining these aspects later using model transformations. The topics handled in the workshop were:

Architecture description languages (ADLs); Domain specific design and implementation languages; Languages for capturing non-functional constraints; Component languages and system description languages.

http://www.artist-embedded.org/artist/Overview,1706.html

#### Workshop: Second IEEE International workshop UML and Formal Methods 11<sup>th</sup> International Conference on Formal Engineering Methods

Rio de Janeiro, Brasil – December 8<sup>th</sup>, 2009

Many interest groups from a research perspective are in favour of the creation of this workshop. For more than a decade now, the two communities of UML and formal methods have been working together to produce a simultaneously practical (via UML) and rigorous (via formal methods) approach to software engineering. UML is the de facto standard for modelling various aspects of software systems in both industry and academia, despite the inconvenience that its current specification is complex and its syntax imprecise. The fact that the UML semantics is too informal have led many researchers to formalize it with all kinds of existing formal languages, like OCL, Z, B, CSP, VDM, Petri Nets, UPPAAL, HOL, Coq, PVS etc. This second workshop will be open to various subjects as the main objective is to encourage new initiatives of building bridges between informal, semi-formal and formal notations.

http://www.artist-embedded.org/artist/Overview,1663.html

#### Workshop: Fourth IEEE International workshop UML and AADL 14th International International Conference on Engineering of Complex Computer **Systems**

Potsdam, Germany – June 2<sup>nd</sup>, 2009

New real-time systems have increasingly complex architectures because of the intricacy of the multiple interdependent features they have to manage. They must meet new requirements of reusability, interoperability, flexibility and portability. These new dimensions favour the use of an architecture description language that offers a global vision of the system, and which is particularly suitable for handling real-time characteristics. Due to the even more increased complexity of distributed, real-time and embedded systems (DRE), the need for a model-driven approach is more obvious in this domain than in monolithic RT systems. The purpose of this workshop is to provide an opportunity to gather researchers and industrial practitioners to survey existing efforts related to behaviour modelling and model-based analysis of DRE systems.

http://www.artist-embedded.org/artist/Overview,1579.html

#### Workshop: Dagstuhl Seminar "Design and Validation of Embedded Systems"

Dagstuhl -- September 30 - October 4, 2009

The aim of this seminar was to discuss topics related to systems with concurrency in a broad set of application domains. We had a broad participation reflecting the various approaches to the problem, including language design, compiler construction, program analysis, formal methods, and testing. To focus the discussions, the seminar also included participants from application areas (embedded reactive systems, robotics, middleware, operating systems, and virtual machines) who have strong interests in verification. We hope these discussions inspired researchers to come up with long-term and practical solutions for the design and verification of concurrent systems. The seminar gathered almost 50 participants.

http://www.dagstuhl.de/de/programm/kalender/semhp/?semnr=09361

#### Workshop: 2<sup>nd</sup> International Workshop on Verification and Validation of Planning and **Scheduling Systems**

Toulouse -- September 29th, 2009

This ARTIST workshop is held in conjunction with ICAPS 2009. Verification techniques, such as model checking, and planning techniques have many commonalities. Planning and scheduling (P&S) systems are finding increased application in safety- and mission-critical systems that require a high level of assurance. Experience has shown that most errors are in domain models, which can be inconsistent, incomplete or inaccurate models of the target domains. However tools and methodologies for verification and validation (V&V) of P&S systems have received relatively little attention. The objective of this workshop is to maintain an interaction between the V&V and P&S communities, to identify specialized and innovative V&V tools and methodologies that can be applied to P&S. Topics of interest include: V&V of domain models, using technologies such as static analysis, theorem proving, and model checking; consistency and completeness of domain models; domain model coverage metrics; regression, stress and boundary testing; runtime verification of plan executions; generation of robust plans; compositional verification of domain models; how to structure domain models which are more amenable to static analysis; inspection methods; the relationship between timed automata and domain models; investigations of the impact wrt. V&V of procedural versus declarative plan models; etc...

http://www-vvps09.imag.fr/

#### Workshop: 9<sup>th</sup> International Workshop on Runtime Verification

Grenoble – June 26th- June 28th, 2009

This ARTIST workshop is held in conjunction with CAV 2009, the objective of RV'09 is to bring scientists from both academia and industry together to debate on how to monitor and analyze the execution of programs, for example by checking conformance with a formal specification written in temporal logic or some other form of history tracking logic. The purpose might be testing a piece of software before deployment, detecting errors after deployment in the field and potentially triggering subsequent fault protection actions, or the purpose can be to augment the software with new capabilities in an aspect oriented style. The longer-term goal is to investigate whether the use of lightweight formal methods applied during the execution of programs is a viable complement to the current heavyweight methods proving programs correct always before their execution, such as model checking and theorem proving. This year's workshop is organized as a satellite event of CAV.

http://www-rv2009.imag.fr/

Automatic test generation of Reactive and timed systems, T. Jéron MSR'09 (http://msr09.irccvn.ec-nantes.fr/), Nantes, France French colloquium on modelling, analysis and command of reactive and real-time systems.

Automatic test generation of Reactive and timed systems, T. Jéron ETR'09 summer school (Ecole d'été Temps réel, http://etr09.telecom-paristech.fr/), Paris, France, 31/08-04/09. Summer school on methods, techniques and tools for real-time systems.

EJCP (Ecole Jeunes Chercheurs en Programmation, http://ejcp2009.inria.fr/) Rennes, France, June 2009. Summer school organized by V. Rusu on modelling, analysis of computer systems.

GASICS Workshop on Games for Design, Verification and Synthesis. Co-located with CAV'09, Grenoble, June 28, 2009. www.lsv.ens-cachan.fr/Events/gasics09/

GASICS is an ESF project of the EUROCORES programme LogICCC (Modeling intelligent interaction - Logic in the Humanities, Social and Computational Sciences). It studies game theoretic formalizations of interactive computational systems and algorithms for their analysis

and synthesis. Our aim is to extend the existing notions of games played on graphs introduced by computer scientists. Currently, most of the games played on graphs are of the sort "two-player zero-sum", we aim to extend them to "multiple-player non-zero-sum", and show the applicability of the new theory to the analysis and synthesis of interactive computational systems. The aim of this workshop is to bring together researchers working on game-related subjects, and to discuss on various aspects of game theory in the fields where it is applied.

**QUANTLOG** Workshop on Quantitative Logics July 11, 2009, Rhodes, Greece Satelite event of ICALP 2009 *quantlog09.web.auth.grl*

The Workshop on Quantitative Logics (QUANTLOG 2009) will take place in Rhodes, Greece, July 11, 2009 as a satellite event of the 36th International Colloquium on Automata, Languages and Programming (ICALP 2009). It is organized under the auspices of the Department of Mathematics of the Aristotle University of Thessaloniki. The aim of the workshop is to provide a forum for researchers interested in the topic of quantitative logics to present their new results and to combine their efforts in the further development of the topic, with emphasis to its connection with automata theory as well as to practical applications.

#### 2.2 Software Synthesis, Code Generation and Timing Analysis cluster

# Tutorial: S. Mamagkakis and P. R. Panda: Memory Architectures and Software Transformations for System Level Design, ASP-DAC 2009

Yokohama, Japan, - January, 2009

In this tutorial a memory-aware system level design flow was presented that can address strict power and performance budgeting problems by customizing both the underlying memory architectures/organizations, as well as by transforming the system-level source code to generate an input for system-level design that is better tuned to the memory architectures and organizations. Such a "memory-aware" system level design flow can result in LSI designs exhibiting superior performance, power and memory footprint characteristics. http://www.aspdac.com/aspdac2009/tutorial/

#### Joint Computer Architecture Seminar (RWTH Aachen and Edinburgh)

Aachen, Germany - Feb. 11, 2009

Objectives for the meeting: During the seminar, different subjects from the research areas of both groups were presented and intensively discussed.

Organizer: This event was organized by RWTH Aachen

Other participants: a research group from the Edinburgh Institute for Computing Systems Architecture (ICSA)

Conclusion: The major focus was on processor customization for embedded applications, fast simulation, advanced profiling, and multi-core programming. Approaches were discussed.

#### **Invited Talk: Predictable Multi-Cores**

Verimag – February 13, 2009

Objective: To explain the PROMPT design principles on predictable multi-core architectures.

Presenter: Reinhard Wilhelm (Saarland U.)

#### **Course: Retargetable Compilation**

Lugano, Switzerland, Feb. 16-19 & Feb 23-25, 2009

Objectives: Spreading excellence in memory-architecture aware compilation and processor retargetability beyond ArtistDesign partners.

Jointly-executed Programme of Integrating Activities

D3-1.0-Y2

Presenters: Peter Marwedel (TU Dortmund), Rainer Leupers (RWTH Aachen)

Other participants: about 20 students

Conclusion: The new, extended format turned out to be very useful.

http://www.alari.ch

# Invited talk: From Embedded Systems to Cyber-Physical Systems: Does the Name Change Matter? – Inauguration of the Uppsala Programming for Multicore Architectures Research Center (UPMARC)

Uppsala, Sweden, March 26, 2009

Objectives: Providing an overview over Embedded Systems Research at Dortmund

Speaker: Peter Marwedel (TU Dortmund)

http://www.it.uu.se/research/upmarc/inauguration

# SPECIAL SESSION - Programming MPSoC Platforms: Roadworks Ahead! (Multi-core Applications Special Day) DATE 2009

Nice, France, - April 23, 2009

Objectives for the meeting: To consolidate today's different MPSoC programming approaches, and to provide focus for future R&D activities.

Organizer: This panel session was organized by R. Leupers (RWTH Aachen) and moderated by M. de Lange (ACE).

Other participants: M. Bekooij from NXP, regular DATE attendees

http://www.date-conference.com/date09/conference/date09-session-12-1

#### Meeting: Joint TA/MPSoC meeting at DATE

Nice, France, April 23, 2009

Objectives for the meeting: To discuss the problem of timing predictability for MPSoC and multi-core from both an analysis and system design perspective.

Organizer: Björn Lisper (MDH)

Other participants: Peter Puschner (Vienna), Abhik Roychoudhury (N.U. Singapore), Simon Schliecker (TU Braunschweig), Mircea Negrean (TU Braunschweig)

Petru Eles (Linköping), Stylianos Magmakakis (IMEC), Paolo Burgio (Bologna), Paul Pop (TU Denmark), Reinhard Wilhelm (USaar), Niklas Holsti (Tidorum)

Conclusions: A number of presentations were given, reflecting the state of the art for timing models and timing analysis both for the system design level and for the code level. The impact of the design on predictability, for both these levels, was discussed, and some possible solutions were presented. It was decided to have a follow-up meeting in the fall.

#### Workshop: Software & Compilers for Embedded Systems (SCOPES) 2009

Nice, France – April 23-24, 2009

Objectives for the meeting: SCOPES focuses on the software generation process for embedded systems.

Organizer: Heiko Falk (TU Dortmund)

Conclusions: There were many discussions between cluster members at SCOPES (starting already on the eve before the sessions), at DATE, making the entire week the key joint event in spring.

http://www.scopesconf.org/scopes-09

# **Keynote: Reinhard Wilhelm – The PROMPT Design Principles for Predictable Multi-Core Architectures, SCOPES 2009**

Nice, France - April 24, 2009

Objectives: The precision of the results and the efficiency of timing-analysis methods are highly dependent on the predictability of the execution platform. The possibility of proving the safety

of embedded systems is seriously compromised by architectural developments aiming exclusively at improving average-case performance.

Presenter: Reinhard Wilhelm (Saarland University)

Conclusions: We propose design principles for multi-core architectures to provide efficiently predictable good worst-case performance as needed for embedded control in the aeronautics and automotive industries supporting the Integrated Modular Avionics (IMA) and the Automotive Open System Architecture (AUTOSAR) development trends. http://www.scopesconf.org/scopes-09

#### **Meeting: Technical Meeting within Predator**

Pisa, Italy – 23rd June, 2009

Objectives for the meeting: Discussing interferences, in particular regarding memory.

Participants: Researchers from SSSA, ETHZ, USAAR, UDORT and ABSINT

Conclusions: We clarified notions of memory interference models based on the real-time calculus, timing guarantees for pre-emptive schedules, cache-related context switch costs and the status of the ERIKA operating system. This provided the starting point for the cooperation of USAAR with SSSA on cache-aware scheduling.

### Invited Talk: Timing Analysis of Real-Time Software - Workshop on Quantitative Analysis of Software

Grenoble, France – June 28, 2009

Objective: Gaving insights into the principles of worst-case execution time analysis and explained current challenges, including transformation of flow information and hardware modelling in the presence of timing anomalies. Further, research on measurement-based timing analysis was presented.

Presenter: Raimund Kirner.

http://www.eecs.berkeley.edu/~sseshia/qa09/

#### Meeting: 2nd Workshop on Mapping Applications to MPSoCs, 2009

St. Goar, Germany - June 29-30, 2009

Objectives for the meeting: This is the flagship workshop of this cluster. The goal of this workshop is to establish links between leading researchers in the area and to stimulate advanced research.

Organizer: Peter Marwedel (TU Dortmund)

Other participants: About 50

Conclusions: We are reaching out far beyond the ArtistDesign network. The workshop is now a key forum for discussions in this area. Attendees expressed their strong interest to continue this series of informal workshops as a platform for discussions. http://www.artist-embedded.org/artist/-map2mpsoc-2009-.html

#### Meeting: 9th International Workshop on Worst-Case Execution Time Analysis, 2009

Dublin, Ireland - June 30, 2009, in connection with ECRTS 2009

Objectives for the meeting: To present and discuss recent work in WCET analysis of all kinds of systems by static or dynamic methods.

Organizer: Niklas Holsti (Tidorum Ltd)

Other participants: About 35

Conclusions: Most of the reported work still deals with single-processor systems where the growing complexity of programs and processors is a continuing challenge. However, an invited talk by Prof. Petru Eles (Linköping University) addressed MPSoCs and somewhat similar ideas were presented in a workshop paper by Martin Schoeberl and Peter Puschner (Vienna University of Technology).

http://www.artist-embedded.org/artist/-WCET-2009-.html

# Keynote: Emerging multi-core hardware platforms and their software support challenges, ECRTS 2009

Dublin, Ireland, - July 1-3, 2009

Objectives: In this keynote talk, the latest developments and future directions of hardware MPSoC platforms for nomadic embedded applications were presented. This keynote was also relevant for the Scheduling and Resource Management activity.

Speaker: S. Mamagkakis (IMEC)

Conclusions: Next to the hardware perspective, the software related challenges of these emerging MPSoC platforms were discussed and some of the proposed parallelization and memory hierarchy management solutions were evaluated.

http://ecrts09.dsg.cs.tcd.ie/keynote-speaker.php

# Invited Tutorial: WCET Analysis: Problems, Methods and Time-Predictable Architectures - Acaces 2009. Fifth International Summer School on Advanced Computer Architecture and Compilation for Embedded Systems

Terrassa (near Barcelona), Spain – July 12-18, 2009

Objectives: Providing an overview over WCET analysis and time-predictable hardware/software architectures.

Presenter: Peter Puschner (TU Vienna) http://www.hipeac.net/acaces2009/

#### Special Series of presentations: Overview of research results from Dortmund

Samsung and SNU, Seoul (Korea), Kyushu U., Fukuoka (Japan), NTU and NUS, Singapore, IIT, Delhi (India), – Aug. 3-14, 2009

Objectives for the meeting: These talks provided an overview over research activities in the "Design Automation for Embedded Systems" group at TU Dortmund, including results from the ArtistDesign NoE and the work on the WCC compiler.

Presenter: Peter Marwedel (TU Dortmund)

Conclusions: This tour through parts of Asia was a very efficient way of strengthening the ties with top research groups in Asia.

#### Tutorial: Multicore and Hard Real-Time Systems - Swedish Multicore Day

Kista, Sweden – Sept 4, 2009

Objectives: Describing the inherent problems with timing predictability for conventional multicore architectures, and gaving an account for ongoing research in the area to practicioners in industry.

Presenter: Björn Lisper (Mälardalen U.)

http://www.sics.se/multicoredays

### Keynote : From Performance to Time-Predictability

#### 9th Architectures and Compilers for Embedded Systems (ACES) Symposium

Edegem, Belgium – September 7-8, 2009

Objectives: Outlining the problems of building predictable hardware/software systems and discussing strategies for constructing systems that provide both temporal predictability and performance.

Presenter: Peter Puschner (TU Vienna)

http://www.elis.ugent.be/aces/index.php?page=activities

#### **ARTIST Summer School in Europe 2009**

Autrans - Sept. 7-11, 2009

Objectives: Disemination of research results

Presenters: Invited presenters include Jan Beutel, and Lothar Thiele

http://www.artist-embedded.org/artist/Overview,1633.html

#### Invited Talk: 7<sup>th</sup> IEEE East-West Design & Test Symposium – EWDTS'09

Moscow, Russia, - Sept. 19.2009

Objectives for the meeting: This talk provided an overview over research activities in the "Design Automation for Embedded Systems" group at TU Dortmund, including results from the ArtistDesign NoE.

Presenter: Peter Marwedel (TU Dortmund)

Conclusions: There is a huge interest in Russia to stay up-to-date with recent research in Western Europe.

http://www.ewdtest.com/conf/

#### Meeting: Static WCET Analysis of multi-process and Multi-processor systems

Saarbrücken, Germany – 25<sup>th</sup> of September, 2009

Objectives for the meeting: To discuss possible approaches for safe WCET analysis of multitask / multi-core systems, and how to use such possible approaches to do WCET-aware code optimization for such systems.

Organizer: Christian Ferdinand (AbsInt)

Other participants: Reinhard Wilhelm (Saarland U.), Sebastian Altmeyer (Saarland U.), Claire Burguiere (Saarland U.)), Daniel Grund (Saarland U.), Jan Reineke (Saarland U.), Henrik Theiling (AbsInt), Christoph Cullmann (AbsInt), Heiko Falk (TU Dortmund), Jan Kleinsorge (TU Dortmund), Sascha Plazar (TU Dortmund)

#### Workshop: Shape Analysis, Timing Analysis - PUMA Workshop

San Servolo Island, Venice - Oct. 5 and 6, 2009

Objectives: Providing an overview over Shape Analysis and on Timing Analysis at the PUMA workshop. This workshop is an annual event held by the PUMA Graduate School of LMU and TU Munich.

Presenter: Reinhard Wilhelm (Saarland U.) http://puma.in.tum.de/wiki/Venice 2009

#### **Workshop on Reconciling Performance with Predictability (RePP)**

Grenoble, France, - October 15, 2009

Objectives for the meeting: The RePP workshop is concerned with embedded systems that are characterized by efficiency requirements on the one hand and critical constraints on the other. Offline guarantees for the satisfaction of critical constraints have to be derived by appropriate methods.

Organizers: Lothar Thiele (ETH Zürich), Reinhard Wilhelm (Saarland U.), Theo Ungerer (U. of Augsburg), Bengt Jonsson (Uppsala U.), Jian-Jia Chen (ETH Zürich)

Conclusions: The discussion included the abstraction mechanism used for structuring systems, which has to consider resources as first-class citizens.

#### Workshop: 5<sup>th</sup> Workshop on Embedded Systems Education, 2009

Grenoble, France, - October 15, 2009

Objectives for the meeting: Embedded system education is still a very young area and frequently restricted to teaching the details of microcontroller programming. A long-term objective of this workshop is to improve the visibility of work in the area and to stimulate the introduction of broader curricula.

Organizer: Peter Marwedel (TU Dortmund)

Other participants: About 30

Conclusions: Visibility was improved by the inclusion of the proceedings in the ACM digital library. Presenters included top researchers from the US and Asia. Attendees were extremely satisfied with the quality of the presentations.

http://www.artist-embedded.org/artist/-WESE-09-.html

Meeting: Joint TA/MPSoC meeting at ESWEEK

Grenoble, France, October 16, 2009

Objectives for the meeting: to foster the contacts between the MPSoC design and timing analysis communities, and build the ground for future research collaborations, by working together on a concrete design example.

Organizer: Björn Lisper (Mälardalen)

Other participants: Raimund Kirner (Vienna), Peter Puschner (Vienna), Simon Schliecker (TU Braunschweig), Stylianos Magmakakis (IMEC), Praveen Raghavan (IMEC), Iain Bate (York), Claire Burguière (USaar), Daniel Grund (USaar), Francesco Paterna (Bologna)

Conclusions: A concrete design example was presented. The example is a safety-critical avionics system with different parts for control, avionics bus interface, and health monitoring of the system. The different parts of the system have different levels of integrity, and different real-time constraints. Different HW/SW system designs, supporting the requirements on the system, were discussed. It was concluded that the example should be further refined in order to support further joint work in system design for timing predictability.

#### Workshop: 1st Workshop on Software Synthesis, 2009

Grenoble, France, - October 16, 2009

Objectives for the meeting: An increasing amount of software is not written manually any more. Rather, software is synthesized from abstract models of the required functionality. Software synthesis has been implemented in various disperse communities. The workshop aimed at bringing these communities together.

Organizer: Peter Marwedel (TU Dortmund); Alberto Sangiovanni-Vincentelli

Other participants: About 20

Conclusions: Presenters at this workshop presented industrial as well as academic results. Attendees agreed on the necessity of more work in this area.

http://www.artist-embedded.org/artist/-WSS-09-.html

## Keynote: Embedded Systems - Trends, Successes, Challenges 10th Anniversary of the Hasso-Plattner Institute

Potsdam - Nov. 18, 2009

Objectives: To celebrate its 10th anniversary, the Hasso-Plattner-Institute holds a conference "Informatik-Impulse".

Presenter: Reinhard Wilhelm (Saarland University) Conclusions: outlook onto future developments.

#### Invited Talk: P. Marwedel: IP - Embedded Systems Conference,

Grenoble, France, - Dec. 3, 2009

Objectives: The objective of this presentation is to spread the results from the first two Rheinfels workshops on mapping applications to MPSoCs.

Presenter: Peter Marwedel (TU Dortmund)

Other participants: Unknown at the time of writing this deliverable

Conclusions: Unknown at the time of writing this deliverable

http://www.design-reuse.com/ipesc09/program/

#### Keynote: Timing Analysis and Timing Predictability - Tag der Informatik

RWTH Aachen - December 4, 2009

Objectives: Presenting the current challenges and existing algorithms in timing analysis, covering also the additional challenges posed by multi-core systems and approaches to achieve predictability for them.

Presenter: Reinhard Wilhelm (Saarland U.)

http://www.nets.rwth-aachen.de/content/current\_events/tdi/pro/index.html

Jointly-executed Programme of Integrating Activities

#### 2.3 Operating Systems and Networks Cluster

**Meeting: Cluster Meeting**

April 2-3, 2009 – Pisa (Italy)

Objectives for the meeting: Coordinating the future work of the Cluster activities.

Organizer: Giorgio Buttazzo, RETIS Lab, Scuola Superiore Sant'Anna (Pisa).

Participants: Giorgio Buttazzo (SSSA, Italy), Karl-Erik Årzén (Univ. of Lund, Sweden), Alan Burns (Univ. of York, UK), Iain Bate (Univ. of York, UK), Stylianos Mamagkakis (IMEC, Belgium), Luis Almeida (Univ. of Porto, Portugal), Magnus Persson (KTH, Sweden), Tahir Naseer (KTH, Sweden), Pau Marti (Univ. of Catalonia, Spain), Alejandro Alonso (Univ. of Madrid, Spain), Lucia Lo Bello (Univ. of Catania, Italy), Emanuele Toscano (Univ. of Catania, Italy), Michael Gonzalez Harbour (Univ. of Cantabria, Spain), Liesbeth Steffens (NXP, The Netherlands), Stefan Petters (Univ. of Porto, Portugal)

#### Meeting: Cache-aware scheduling

June 22, 2009 – Pisa (Italy)

<u>Objectives for the meeting</u>: Discussing on the effects of preemptive scheduling on cache memories and worst-case execution times, and identifying new research directions and possible collaborations.

Organizer: Giorgio Buttazzo, RETIS Lab, Scuola Superiore Sant'Anna (Pisa).

Other participants: Giorgio Buttazzo (SSSA), Marco Caccamo (UIUC), Marko Bertogna (Pisa), Francesco Esposito (Pisa), Mauro Marinoni (Pisa), Gang Yao (Pisa), Christoph Cullmann (Absint), Sebastian Altmeyer (Saarland), Claire Burguiere (Saarland), Sascha Plazar (TU Dortmund), Jan Kleinsorge (TU Dortmund), Andreas Schranzhofer (ETHZ), Jian-Jia Chen (ETHZ), Luca Benini (Bologna), Martino Ruggiero (Bologna).

### Meeting: Graduate Course on Embedded Control Systems: Theory and Practice June 8-12, 2009 – Pisa (Italy)

Objectives for the meeting: Providing the fundamentals concepts of real-time computing systems, including scheduling, resource management and timing analysis; Introducing the OSEK/VDX standards, taking as a reference implementation the Erika Enterprise kernel; Showing how to apply such concepts in practice, with examples based on the Flex platform and the Microchip dsPIC DSC microcontrollers.

Organizers: Giorgio Buttazzo (Pisa), Karl-Erik Arzen (Lund), Luis Almeida (Porto).

Other participants: Tesnim Abdellatif (Verimag), Simon Aittamaa (LTU), Gaetano Anastasi (Pisa), Claudia Barberis (Torino), Imene Ben Hafaiedh (VERIMAG), Irene Bicchierai (DSI), Torsten Bruns (University Paderborn), Laura Carnevali (Firenze), Jacques Combaz (Verimag), Johan Eriksson (LTU), Francesco Esposito (Pisa), Cyril Faure (IFP), Stefano Fontanelli (Pisa), Nadereh Hatami (Torino), Benjamin Kuch (Pisa), Rom Langerak (U.Twente), Holger Nahrstaedt (TU Berlin), Christian Nastasi (Pisa), Moritz Neukirchner (TU Braunschweig), Simon Perathoner (ETH Zurich), Sophie Quinton (Verimag), Lorenzo Ridi (Firenze), Andreas Schranzhofer (ETH Zurich), Vassiliki Sfyrla (Verimag), Colin Shaw (BCIT), Gang Yao (Pisa).

URL: http://www.artist-embedded.org/artist/ARTIST-Embedded-Control-2009.html

Meeting: OSPERT 2009 - Fifth International Workshop on Operating Systems Platforms for Embedded Real-Time Applications

Dublin, Ireland - June 30th, 2009

Jointly-executed Programme of Integrating Activities

Objectives for the meeting: This workshop was intended as a forum for researchers and practitioners of RTOS to discuss the recent advances in RTOS technology and the challenges that lie ahead. The workshop consisted of submitted papers as well as invited presentations about academic state-of-the-art and industrial state-of-practice within the area of real-time operating systems architectures and services.

#### Organizers:

• Stefan M. Petters, IPP-Hurray, ISEP-IPP, Polytechnic Institute of Porto, Portugal

URL: <a href="http://ospert09.cister-isep.info/">http://ospert09.cister-isep.info/</a>

#### Meeting: WCET 2009: Worst Case Execution Time Analysis

Dublin, Ireland – June 30th, 2009

Objectives for the meeting: The goal of the workshop was to bring together people from academia, tool vendors and users in industry interested in all aspects of timing analysis for real-time systems. The workshop fostered a highly interactive format with ample time for indepth discussions. It provided a relaxed forum to present and discuss new ideas, new research directions, and to review current trends in this area. The presentations were kept short to leave plenty of time for interaction of attendees.

#### Organizers:

Niklas Holsti, Tidorum Ltd., Tiirasaarentie 32, 00200 Finland.

URL: <a href="http://www.artist-embedded.org/artist/WCET-2009.html">http://www.artist-embedded.org/artist/WCET-2009.html</a>

#### Meeting: RTN 2009: Real-Time Networks

Dublin, Ireland - June 30th, 2009

Objectives for the meeting: The Real Time Networks (RTN, formerly RTLIA) workshop was the seventh on the series of workshops that started at the 2002 ECRTS conference. RTN focuses on the current technological challenges of developing communication infrastructures that are real-time, reliable, pervasive and interoperable. The goal of this workshop was to bring together people from industry and academia that are interested in all aspects of real-time communication. The workshop provided a relaxed forum to present and discuss new ideas, new research directions and to review current trends in this area.

#### Organizers:

- Eduardo Tovar, Polytechnic Institute of Porto, Portugal

- Jean-Dominique Decotignie, Swiss Center for Microtechnology CSEM, Switzerland.

URL: http://www.hurray.isep.ipp.pt/rtn09/index.php

#### Meeting between York and Aachen

York, UK – October 26th, 2009

Objectives for the meeting: Meeting with Prof Anke Schmeink, presentation of Aachen's UMIC Cluster (Ultra High-Speed Mobile Information & Communication) and its activities on the systematic design of mobile communication systems, presentation of York's research in evaluating performance and power dissipation of on-chip multiprocessor platforms

Meeting: 4.1.1: STANDRTS 2009 - Workshop on the Definition, Evaluation, and Exploitation of Modelling and Computing Standards for Real-Time Embedded Systems Dublin, Ireland – June 30th, 2009

Objectives for the meeting: The main focus of the workshop is the identification of modelling constructs and usage styles that may lead to the better exploitation and/or evolution of the standards for the RTES domain in general.

#### Organizers:

- Sebastien Gerard, CEA LIST, France

- Henrik Lonn, Volvo Technology, Sweden

- Julio Medina, Universidad de Cantabria, Spain

- Laurent Rioux, THALES Research and Technology, France

- Ramin Tavakoli Kolagari, Volvo Technology, Sweden

URL: http://www.adams-project.org/standrts09/

#### 2.4 Hardware Platforms and MPSoC Cluster

### Meeting: ArtistDesign WP6 Cluster Meeting on Hardware Platforms and MpSoC Braunschweig, Germany – June 25/26 2009

Objectives for the meeting: The main objective of this meeting was a mutual update on the joint research progress of the WP6 cluster participants, but speakers from the relevant industrial domains traditionally join (in tradition to previous years).

Organizer: Rolf Ernst (TUBS)

Other participants: All cluster members were present with several people. Other participants included Matthias Gries, Gregor Stellpflug (Intel Labs), Nico Feiertag, Kai Richter (Symtavision), Fabian Wolf (Volkswagen).

Conclusions: The meeting has highlighted key problems in the design and analysis of upcoming embedded systems and suggested solutions in different stages of maturity. Topics included performance analysis, reliability, adaptivity, and early design space exploration. The industrial speakers have contributed talks about timing analysis in automotive applications. The meeting has shown that formal methods as developed in this project are increasingly adopted in the industrial design practice.

https://webmail.ida.ing.tu-bs.de/twiki/bin/view/Main/ArtistDesignClusterMeeting

#### **Meeting: Cluster meeting**

Nice. France - April 25-26, 2009

Objectives for the meeting: Alignment and planning of cluster activities.

Organizer: Petru Eles (Linkoping)

Other participants: Most of the cluster partners were participating.

Conclusions: Discussions on collaboration and planning of the yearly cluster meeting.

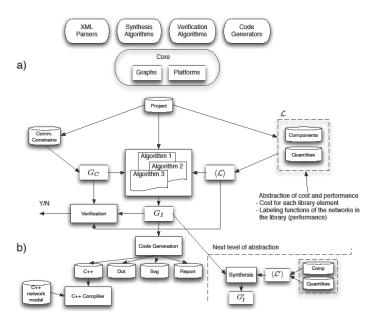

### Meeting : MP-MH MPSoC parallelization assistant and memory hierarchy assignment for MPSoC

Objectives for the meeting: The main objectives of the framework is to offer an automatic source code parallelization (MPA tool) and memory hierarchy management (MH tool) in order to map efficiently embedded software application on MPSoC platforms. This toolsuite is also used in the Software Synthesis, Code Generation and Timing Analysis cluster.

Organizer: IMEC

Other participants: NTUA/ICCS, TUDortmund

Conclusions: After the prototype versions of the MPSoC Parallelization Assistant (MPA) and Memory Hierarchy (MH) management tools were developed and tested, we proceeded in their integration as a single MP-MH tool, thus solving interdependency and exploration optimization issues. Currently, the affiliated partners of IMEC (ie, NTUA/ICCS) and core partners (TUDortmund/ICD) are trying to integrate their tool and design flows with the IMEC MP-MH framework in the memory assignment context of the MNEMEE FP7 project.

http://www.mnemee.org/ <http://www.mnemee.org/>

http://www.imec.be/cleanc <http://www.imec.be/cleanc>

### 2.5 Design for Adaptivity in Embedded Systems (Transversal Integration WP)

Workshop: Fourth International Workshop on Feedback Control Implementation and Design in Computing Systems and Networks (FeBID 2009), Cyber-Physical Systems Week,2009

San Francisco, US - April 16, 2009

Traditional practice in performance modeling focuses on using a variety of techniques including mathematical modeling, simulation, and analysis to understand the behavior of systems for the purpose of better design and evaluation. As IT systems, networks, and services become increasingly complex, this task becomes ever more difficult. In recent years, there has been considerable success in applying feedback control theory to analyzing and designing run-time IT control systems. Feedback control theory complements traditional modeling by providing formal mechanisms to dynamically control behavior of systems at run-time.

The FeBID series of workshops offer a unique opportunity for researchers and practitioners to discuss recent and innovative results in applying control theory to controlling performance of computing systems and networks. It provides a forum to exchange ideas and experiences on practical control system design and implementation and to identify future directions and challenges in aligning feedback control techniques with traditional performance modeling and simulation. The workshop program consisted of one invited plenary talk and 12 submitted papers. The workshop was co-chaired by Karl-Erik Årzén (ULUND) and several of the members of this activity participated in the PC. The workshop was co-funded by Artist.

http://controlofsystems.org/febid2009/

### Workshop: Second Workshop on Adaptive and Reconfigurable Embedded Systems (APRES 09), Embedded Systems Week, 2009

Grenoble, France - October 11, 2009

This was the second workshop in the APRES series which is co-funded by Artist. It aims at discussing new and on-going research in the development and use of adaptive and reconfigurable embedded systems and gathering feedback from the embedded systems community at large. Of particular interest are new concepts and ideas for modeling and analyzing tradeoffs of embedded and real-time systems, novel algorithms and mechanisms to realize adaptation and reconfigurability, and experience reports with practical or industrial case studies. The workshop was co-organized by Luis Almeida, Karl-Erik Årzén (members of the activity), and Sebastian Fischmeister, Insup Lee, and Juilan Proenza (non-members), with several of the Artist partners in the programming committee. The workshop contained 12 submitted paper and Stylianos Mamagkakis of IMEC gave a very appreciated plenary presentation. The number of participants at the workshop was around 25. The papers of the workshop will be published by SIGBED Review.

http://www.artist-embedded.org/artist/Overview,1765.html

#### **Course: ARTIST Graduate Course on Embedded Control Systems**

Pisa, Italy – June 8-12, 2009

The fifth annual ARTIST Graduate Scool on Embedded Control Systems was organized and delivered by Giorgio Buttazzo and Mauro Marinoni (SSSA), Karl-Erik Årzén and Anton Cervin (ULUND), Paolo Gai (Evidence), Luis Almeida (UPorto), and Paulo Pedreiras (UAveiro).

The objectives of the course were to:

- Introduce the most important concepts and methodologies used to develop a real-time embedded system, including fundamentals of real-time scheduling, control and distributed systems;

- Show how to apply these concepts to develop simple real-time control applications using an embedded platform specifically developed for education.

http://www.artist-embedded.org/artist/Overview,1673.html

#### **Meeting: Annual Activity Meeting**

Pisa, Italy - April 2-3, 2009

Objectives for the meeting: Organize the activities during Year 2. Present the adaptive resource management related activities in FRESCOR, ACTORS, DysCAS together with the work at UPC/SSSA, DTU, and IMEC.

Organizer: Karl-Erik Årzén (ULUND) & Giorgio Buttazzo (SSSA)

Participating groups: ULUND, SSSA, TUKL, University of York, IMEC, UPorto, KTH, UPC, UPM, UCatania, DTU, UCantabria, Universidad Carlos III de Madrid, NXP, IPP Conclusions:

- The structure for a wiki-based white paper on embedded system adaptivity was outlined and set up. Initial contents were added.

- It was decided that the activity should take the initiative to an one-day workshop on adaptive resource management to be held in conjunction with the Cyber-Physical Systems Week in Stockholm, Sweden in April 2010. This should also constitute the annual activity meeting for 2010.

Web site: http://www2.control.lth.se/ArtistAdapt/index.php/Main Page/Meetings/Pisa Apr 2009

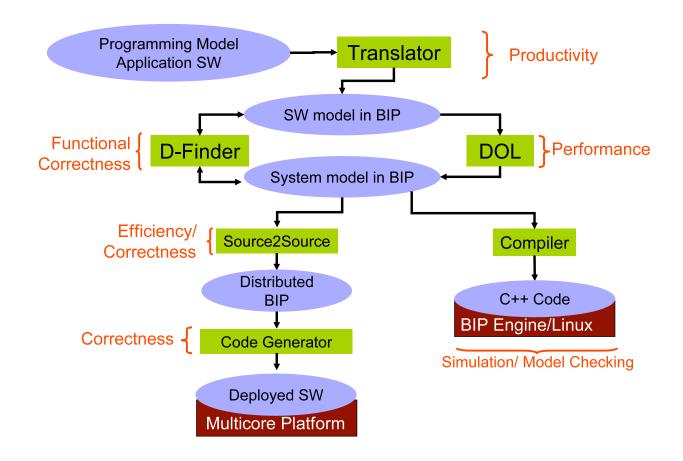

#### Meeting: BIP - DOL, 13th Oct. 2009

Grenoble, France

Objectives for the meeting: The main goal of this meeting was to introduce the available execution platforms of the DOL framework and try to find a suitable one for BIP.

Organizer: Verimag

Other participants: Verimag, ETHZ

Conclusions: There are three execution platforms available from the DOL framework, i.e., the SHAPES platform, the broad band cell engine, and the DOL/MPARM simulator. It was concluded that the DOL/MPARM is suitable for the BIP timed model.

#### Meeting: Real-time Parameters, 1<sup>st</sup> Oct. 2009

Zurich. Switzerland

Objectives for the meeting: Establish a set of server-based resource-reservation strategies and their suitability for dynamic reconfigurations in resource-constraint systems.

Organizer: ETHZ

Other participants: ETHZ, SSSA

Conclusions: The well-known server-based resource-reservation strategies are not designed to be adaptive therefore, new methods and strategies are needed that can guarantee resource-reservations during configuration changes. A new server-based strategy and a mechanism for reconfiguration have been proposed. This is currently investigated jointly by ETHZ and SSSA.

**Meeting**: DySCAS Open Workshop Brussels, Belgium – February 18, 2009

Objectives for the meeting: Dissemination of the results of the "Dynamically Self-configuring"

Automotive Systems" (DySCAS) FP6 project

Organizer: Volvo (coorganised and funded by Artist)

Conclusions: http://www.artist-

embedded.org/docs/Events/2009/DySCAS/DySCAS%20workshop%20February%2018%20-

%20Summary MT.pdf

Web site: http://www.artist-embedded.org/artist/DySCAS-2009,1555.html

In addition KTH has had several meetings within the context of of the Dyscas project with Offis (ArtistDesign partner), Volvo (affiliated ArtistDesign partner), and Bosch, Daimler, Enea and Univ. of Grenwich.

### 2.6 Design for Predictability (Transversal Integration WP)

## Meeting: Static WCET Analysis of multi-process and Multi-processor systems Saarbrücken, Germany – 25<sup>th</sup> of September, 2009

Objectives for the meeting: To discuss possible approaches for safe WCET analysis of multitask / multi-core systems, and how to use such possible approaches to do WCET-aware code optimization for such systems.

Organizer: Christian Ferdinand (AbsInt)

Other participants: Reinhard Wilhelm (Saarbrücken), Sebastian Altmeyer (Saarbrücken), Claire Burguiere (Saarbrücken), Daniel Grund (Saarbrücken), Jan Reineke (Saarbrücken), Henrik Theiling (AbsInt), Christoph Cullmann (AbsInt), Heiko Falk (Dortmund), Jan Kleinsorge (Dortmund), Sascha Plazar (Dortmund)

#### **Meeting: Technical Meeting within Predator**

Pisa, Italy – 23th June, 2009

Objectives for the meeting: Discussing interferences, in particular regarding memory.

Participants: Researchers from SSSA, ETHZ, USAAR, UDORT and ABSINT

Conclusions: We clarified notions of memory interference models based on the real-time calculus, timing guarantees for preemptive schedules, cache-related context switch costs and the status of the ERIKA operating system. This provided the starting point for the cooperation of USAAR with SSSA on cache-aware scheduling.

# 2.7 Integration Driven by Industrial Applications (Transversal Integration WP) Meeting: Workshop: CyberPhysical Systems Forum, CPS Week

San Francisco, April 15, 2009

Objectives for the meeting:

The Cyber-Physical System Forum is the second edition of the event following the successful first edition held in St Louis, MO, in 2008 also co-sponsored by COMBEST. The Forum was held during the CPS week in San Francisco and was organized with the NSF and COMBEST sponsorship joint with the ArtistDesign NoE. The forum was structured into three panels addressing different aspects and challenges related to the design of cyber-physical systems. The objective was to define with more clarity the research agenda and how to set up a sustained, multi-year research program with strong collaboration between the European and the US Community. In particular, for each of the panel, there was one presenter from the European community either from Combest or from ArtistDesign.

Organizers: Bruce Krogh (CMU), Raj Rajikumar (CMU), Alberto Sangiovanni-Vincentelli (Berkeley, Trento).

Other participants: There were about 500 participants and 12 speakers, the European speakers (Alberto Sangiovanni Vincentelli, Christoph Kirsch, Karl Erik Arzen and Albert Benveniste) were all ArtistDesign Partners. In the participant list all or almost all ArtistDesign partners were represented.

Conclusions After the presentations, during the reception following the meeting, there was a a general consensus among the participants about the relevance of the field, research needs and the necessity to form joint teams among industry and academia **in Europe and US** for CyberPhysical Systems that are now a priority of NSF and of the Obama computing program. In particular, issues related to education and use of the results of the technology in novel application spaces were identified as crucial for the future of the field in general. Since then, NSF started a major research program:

http://www.nsf.gov/publications/pub\_summ.jsp?ods\_key=nsf08611

"Congruent with the recommendations in the August 2007 report of the President's Council Scienceand Technology (PCAST), Leadership Under Challenge: Information Technolog Competitive World,NSF's Directorates for Computer and Information Science and Engineeri Engineering (ENG) are spear-heading the Cyber-Physical Systems (CPS) program because and technological importance as well as its potential impact on grand challenges in a num critical to U.S. security and competitiveness, including aerospace, automotive, chemical prinfrastructure, energy, healthcare, manufacturing, materials and transportation. By abstract particulars of specific applications in these domains, the CPS program aims to reveat fundamental scientific and engineering principles that underpin the integration of cyber and phyacross all application sectors."

ArtistDesign partners continue being involved in the initiative with the intent of bridging the two research communities on the fundamental themes outlined in the ArtistDesign research agenda. We expect that in the third edition of the CPS week to be held in Stockholm April 12-16, 2010 (<a href="http://www.cpsweek2010.se/web/page.aspx?pageid=57517">http://www.cpsweek2010.se/web/page.aspx?pageid=57517</a>) the involvement of ArtistDesign partners will be even more visible and we expect to present some of ArtistDesign achievements in that forum.

http://varma.ece.cmu.edu/CPS-Forum/index.html

#### Meeting: Workshop: Smart and Efficient Energy Council SEEC-09,

Trento, October 8-9, 2009.

Objectives for the meeting: The goal of the workshop was to discuss energy efficiency as a major contributor to the green economy. Data shows that alternative sources alone are insufficient to meet the increasing energy demand. Higher efficiency is therefore required to address the energy problem and to reduce the carbon footprint resulting in better environmental conditions. Many new initiatives for energy efficiency are afoot worldwide. The Workshop was intended to provide a forum where various initiatives were presented and discussed, results presented and open problems introduced. Emphasis was on addressing the problem from a system standpoint with deep discussions about the role of embedded systems and embedded control and relationship between Industry, Government and Academia. There was a wide participation from industry (22 out of the 78 participants, and 8 out of 15 presentations were from industry). In particular, there was a continuous interaction among the participants during break time to define follow-up activities in EU projects and continuation of the workshop.

The agenda was based on a two day event where ample time for discussions was allowed.

*Organizers:* Alberto Sangiovanni Vincentelli (UC Berkeley and Trento), Roberto Passerone (Trento)

Other participants: There were 78 participants of whom 27 were representing ArtistDesign partners (CEA, University of Trento, University of Bologna, TU Braunschweig, Politecnico di Milano, Politecnico di Torino, University of Verona, Scuola di Sant'Anna, TU Dortmund, CEA, University of Twente, and TU Denmark). 22 were industrial participants working in international corporations (UTC, Honeywell, Siemens, Fiat, Telecom Italia, ENEL) or in SMEs (Evidence, Optoelettronica, Yogitech, FARSystems, RDSystems, Gruner, Renience, SOFCPower, Fortiss). The participants and the presentations of the meeting are available on the ArtistDesign Web site. The meeting was very well received by the participants. Prof. Morari, Chair of EE of ETH, pointed out that this was probably the best workshop in years he participated to. This point of view expressed in the closing session of the meeting was echoed by most other participants.

#### Conclusions:

After the two-day presentation, there was a a general consensus among the participants about the relevance of the field, research needs and the necessity to form joint teams among industry and academia in Europe and across the Ocean to provide critical mass for a game changing approach to energy efficiency.

Energy-efficient smart buildings in particular were considered to be an area where there is an exponentially growing interest for traditional industry such as construction, HVAC, monitoring and energy optimization as well as ICT industry. During the meeting, it was emphasized that the key to efficiency is the use of advanced embedded system techniques including wireless sensor networks and embedded controllers. The European Community has started a fairly large effort in this area as documented by the November call of ICT in Framework 7 and the US has declare the energy efficiency area as a top priority. There was an agreement among participants to make the conclusions of the meeting widely known via a Press Release and a special issue in a Journal to be determined. There was also an intense discussion about a major collaborative US-European program and a project was drafted to be presented to NSF, the Department of Energy, and the EU community. Several participants are collaborating to present a joint proposal to the EU. There was an explicit request by the participants to have a follow-up meeting in one year time frame. Some of the participants had strong interest in how

to drive legislation, regulations and standards to favour energy efficiency. There was a mandate to organize a workshop/meeting with the same sponsorship involving Government, law, economics and engineering experts to discuss this important point. The European Institute of Technology call in the Energy and ICT fields were discussed and it was hoped that the ArtistDesign community would participate to define the technical agenda of the two Institutes once they will be assigned (January 2010).

http://www.artist-embedded.org/artist/SEEC-09.html

#### Meeting: Workshop: Workshop on Software Synthesis - WSS'09

October 16th, 2009, Grenoble, France (within ES Week)

Objectives for the meeting: An increasing amount of software is not written manually any more. Rather, software is synthesized from abstract models of the required functionality. As a result, the effort of generating software is reduced and software verification typically becomes easier. Software synthesis has been implemented in various disperse communities. The workshop aims at bringing these communities together and at identifying research problems which should be addressed by the scientific community.

Organizers: Peter Marwedel (Tu, Dortmund), Alberto Sangiovanni Vincentelli (Trento and UC Berkeley)

Other Participants: There were about 20 attendants mostly from ArtistDesign partners. The speakers were Ed Lee from UC Berkeley substituting for Alberto Sangiovanni Vincentelli, Karl-Erik Arzen (Lund), Emmanuel Roy (Mathworks), Markus Gros (dSpace), and Paul Caspi (Verimag).

Conclusions: The participants to the final panel discussed the status of the field and its potential directions.

Emmanuel Roy (Mathworks):

- Better bridge gap between algorithmic components and true software

- Mathworks: Better distribution to the processors in the network. e.g. in a car.

Christian Fabe (CEA):

How to make sure that 1000 people can work on the same project?

Peter Marwedel (TU Dortmund)

This is consistent with Markus Gros' (dSpace) view that handling of large scale models is a problem.

Tetsuya Tohdo (Denso):

Look at the future, SOA for automotive? How to guarantee security?

Edward Lee (UCB):

- SOA too much rooted in OO-design, no time, no concurrency

- a single language will not work

Christian Fabe (CEA):

At least a single intermediate representation should be there.

#### Paul Caspi (IMAG):

Faithfulness is important, if you don't have it, you have lost the advantage of model-based design.

#### Edward Lee (UCB):

If you have a way of encapsulating components, you achieve this.

Reinhard von Hanxleden (U. Kiel):

Raise the level at which compiler writers are working.

http://www.artist-embedded.org/artist/Scope.html

## Meeting: Workshop: ArtistDesign WP6 Cluster Meeting (Activity 6.2 Platform and MpSoC Analysis)

Braunschweig, Germany - June 25/26 2009

Objectives for the meeting: While the main objective of this meeting was a mutual update on the joint research progress of the WP6 cluster participants, speakers from the relevant industrial domains traditionally join.

Organizer: Rolf Ernst (TU Braunschweig)

Other participants: Matthias Gries, Gregor Stellpflug (Intel Labs), Nico Feiertag, Kai Richter (Symtavision), Fabian Wolf (Volkswagen)

Conclusions: The meeting has highlighted key problems in the design and analysis of upcoming embedded systems and suggested solutions in different stages of maturity. Topics included performance analysis, reliability, adaptivity, and early design space exploration. The industrial speakers have contributed talks about timing analysis in automotive applications. The meeting has shown that formal methods as developed in this project are increasingly adopted in the industrial design practice.

https://webmail.ida.ing.tu-bs.de/twiki/bin/view/Main/ArtistDesignClusterMeeting

#### Workshop: 2<sup>nd</sup> Annual ICES Conference Stockholm,

Sweden, Sept. 2<sup>nd</sup>, 2009

The conference celebrated the first year anniversary of the KTH based centre for Innovative Embedded Systems – ICES. The overallgoal of the conference was for ICES representatives from industry and KTH to present the drivers for ICES and accomplishments during the first year, as well as ICES vision, goals and concrete activities, including an inventory of Embedded Systems at KTH.

75 people from academia, industry, funding agencies and the press took part in this conference at the Norra Latin Conference Centre in Stockholm. The purpose of this all day conference was to present trends and challenges in embedded systems design, verification, architecting and integration from industrial and scientific viewpoints. The theme was addressed by a program including:

- - Invited presentations from industry and KTH

A keynote talk by Prof. Werner Damm (Offis)

- Presentations of ICES visions, goals, activities and accomplishments.

- addressing these challenges

- An exhibition, presenting ICES-related research projects, education

- and industrial products

- A panel debate discussing how to meet the challenges.

The Keynote Talk described trends and challenges from the viewpoint of the transportation sectors: Automotive, Aerospace and Railway. The three transportation domains share the need to develop advanced embedded systems to meet societal demands for increased mobility and accident reduction while reducing environmental load (CO2 emission and energy consumption) and maintaining high safety levels in spite of increasing traffic density and increased systems complexity. The domains are facing a highly competitive market and faces constraints imposed by (forthcoming) safety standards such as ISO CD 26262, Do178 B/C, CenelecEN 50128/50129, IEC 61508. Achieving continuous cost reduction, performance improvement and efficiently dealing with verification/certification will continue to be a challenge and a key focus in the domains. Werner Damm illustrated research efforts in the area by describing the SPEEDS and CESAR European projects, and their work to develop powerful and efficient supporting methods and tools for the development of safety critical embedded systems.

Invited industrial talks were given by:

- Micronic addressing challenges in introducing model-based engineering into industrial development.

- · Prevas discussing challenges in embedded systems processes and testing with examples taken from the telecom and automotive domains, and

- Stoneridge in developing future human machine interfaces.

The KTH talks included overviews of trends and challenges in electronic computing platforms (multicore, terascale computing), wireless communication and automous robots.

http://www.kth.se/itm/centra/ices/ices-events/previous-events/1.44090?I=en UK

### Meeting: Workshop: ICES Seminar: Platform Based Development in Practice

Stockholm, Sweden, March 31, 2009

The ICES seminar "Platform Based Development in Practice" took place at ABB Corporate Research's facilities in Västerås on Tuesday 31st March. The goal was to present Platform Based Development (PBD) from different angles and share experiences over domains.

About 50 people attended the seminar, around 10 of whom were from companies/institutions which are not (yet) ICES members. The seminar started with a Welcome from ICES Board member Jan-Erik Frey (ABB) and an introduction by ICES Director Martin Törngren (KTH) who discussed among other things the terminology around Platforms, in order to create a common understanding of the different concepts.

Speakers from ABB, ÅF, Enea and Microsoft presented their viewpoints on PBD, and gave the audience a good insight into both domain-specific issues as well as more general aspects such as organizational issues and impact on development time and cost.

After lunch and a demonstration of a new concept for wireless vibration monitoring on oilplatforms, Johannes Helander, a chief architect from Microsoft gave an inspiring presentation and shared his view of future development methods of embedded platforms.

In conclusion, PBD still remains a challenge in many respects. Design of embedded sytems platforms requires considerations over a large range of system variants including both software and hardware. Moreover, PBD poses a great challenge for testing, where the variability of products increase the state space.

http://www.kth.se/itm/centra/ices/ices-events/previous-events/1.36723?I=en UK

#### Meeting: Workshop: ICES Seminar on Testing and verification

Stockholm, Sweden, Feb. 12, 2009

The ICES seminar on testing and verification was hosted by Scania in Södertälje. The seminar had about 55 participants representing a good blend of industrial domains (automotive, telecom, automation) and academic researchers.

The invited talks presented testing from several viewpoints, including safety standards; organizational integration and culture; process integration; and continuous improvement, as well as testing techniques. One of the conclusions from the seminar was that there are needs for improved education and intensified research in the area of testing. For industry, logging their performance and learning, was emphasized as a key point.

http://www.kth.se/itm/centra/ices/ices-events/previous-events/1.33317?I=en UK

#### Meeting: Workshop: ICES-VINNOVA European Research Seminar, 28th January 2009

Stockholm, Sweden, January 28th, 2009

In collaboration with Vinnova (the Swedish governmental Research and Innovation Agency), KTH arranged a seminar on Themes, forms and funding relating to European research. The seminar arouse from the need to better disseminate opportunities for research on the European level, and to discuss similarities and differences among ITEA2, Artemis and FP7.

Around 45 people attended the ICES-VINNOVA open seminar "European Research in Embedded Systems: Themes, Forms and Funding", which took place at KTH on 28th January 2009.

The seminar was very successful, with interesting presentations, questions and discussions. The details of the ITEA2 (invited presentation by Rudolf Haggenmueller), FP7 (invited presentation by Philippe Reynert) and ARTEMIS (invited presentation by Alun Foster) programs were explained, including rationale and the directions for the current calls. Vinnova also presented the Swedish funding and support available.

In addition, industrial experiences and viewpoints were presented. A lot of the discussion focused on the relations between the programs and when to choose which. Among the conclusions, an overview of the current large project portfolios was called for.

http://www.kth.se/itm/centra/ices/ices-events/previous-events/1.32246?l=en UK

#### **Meeting: SMECY Project Proposal Face-to-Face Meeting**

Paris, France - 2009-06-25

Objectives for the meeting: The goal of this meeting was to discuss the SMECY project proposal for "Smart Multicore Embedded Systems", which addresses the ARTEMIS Joint Undertaking Call 2009. The project envisions new programming technologies that enable the exploitation of many-core architectures in embedded systems.

Organizer: Francois Pacull (CEA), Ahmed Jerraya (CEA)

Other participants: Jonas Diemer (TU Braunschweig), Francois Pacull (CEA), Ahmed Jerraya (CEA), Joseph Sifakis (IMAG), Gilbert Edelin (Thales), and others (from over 20 institutions in total).

Conclusions: As a result, the 44 participants from industry and academia submitted the SMECY project proposal to the ARTEMIS JU. The project ranked high and was invited to funding negotiations, which are ongoing.

#### ArtistDesign Workshop on Embedded Systems in Healthcare 2009

Eindhoven, the Netherlands -- December, 7, 2009.

Objectives for the meeting: The goal of the Workshop on Embedded Systems in Healthcare is to strengthen the connections between academic research and industry, or to be more precise, to increase the understanding in the academic world of industrial issues in embedded systems engineering and together come to a shared agreement on research directions that seem worthwhile to pursue.

Organizers: Boudewijn Haverkort (ESI), Pierre America (Philips Research & ESI), Piërre van de Laar (ESI), Miranda Willems (ESI), Roland Mathijssen (ESI).

The speakers at the workshop work at different medical companies or are participants in the ArtistDesign network with extensive experience in healthcare. The topics include "How to design long lasting devices for a fast changing world?", "Cochlear Implant Systems: today's challenges in embedded firmware design", and "Embedded Contributions to an Intensive Care Safety Concept".

http://www.artist-embedded.org/artist/Overview,1831.html

#### **SafeTRANS Industrial Days**

Stuttgart, Germany, May 5, 2009 and Friedrichshafen, Germany, November 19, 2009

Within the context of SafeTRANS (including ArtistDesign members) two Industrial Days were organized in 2009. These workshops provide a platform for discussion and exchange of experiences in industry across application domains.

The first one on "Safety Management along the suppliers chain" was held in May 2009 in Stuttgart at Robert Bosch GmbH. Presentations from different application domains (avionics, automotive, rail) were given covering requirement management, development process in the context of ISO 26262, safety management in the development of safety critical rail systems as well as aspects of systems integration.

The second workshop took place on November 19 in Friedrichshafen at EADS on "Model-based testing and test automation". Presentations from industrial participants (Ford, Daimler, EADS, Siemens Validas) and academic participants cover verification of safety critical automotive applications, deployment of model-based technologies to industrial testing, model-based testing for critical functions on architecture level – vision, concepts and way forwards in aeronautical engineering, Domain specific modeling and generation of test cases, model-based testing, risk oriented testing.

http://www.safetrans-de.org/de\_6\_Industrial\_Day.php http://www.safetrans-de.org/de\_7\_Industrial\_Day.php 214373 ArtistDesign NoE JPRA

Jointly-executed Programme of Integrating Activities

Year 2 (Jan-Dec 2009) D3-1.0-Y2

### 3. Staff Mobility and Exchanges

From the Description of Work:

Staff Mobility and Exchanges between teams are essential for integration within and beyond the NoE, including mobility of students and/or researchers, between core teams, or between core teams and affiliated teams.

Mobility should be justified by and refer to involvement in an activity from the JPRA or JPIA, or one of the following: co-funded scholarships with industry; exchange of students and personnel within the consortium.

#### -- Changes wrt Y1 deliverable --

All new text: this entire chapter pertains only to activity in Year 2.

#### 3.1 Modelling and Validation Cluster

Oded Maler visited ETH Zurich and Aalborg University where he collaborated with Kim Larsen on probabilistic semantics for timed automata.

The collaboration between VERIMAG and EPFL lead to the recruitment of Barabara Jobstmann as a permanent researcher at VERIMAG.

#### Sandeep Shukla, (associate professor at Virginia Tech) )