technische universität dortmund

# **Model-based Embedded Systems** Design

### - Introduction, Motivation and Overview -

Peter Marwedel Informatik 12 **TU Dortmund** Germany

2010/06/25

Graphics: © Alexandra Nolte, Gesine Marwedel, 2003

These slides use Microsoft clip arts. Microsoft copyright restrictions apply.

# Motivation for Course (1)

According to forecasts, the future of IT is characterized by terms such as

- disappearing computers,

- ubiquitous computing,

- pervasive computing,

- ambient intelligence,

- the Post-PC era, and

- cyber-physical systems.

**Basic technologies:**

- Embedded Systems

- Communication technologies

ICD fakultät für

informatik 12, 2010

### Motivation for Course (2)

"Information technology (IT) is on the verge of another revolution. .....

networked systems of embedded computers ... have the potential to change radically the way people interact with their environment by linking together a range of devices and sensors that will allow information to be collected, shared, and processed in unprecedented ways. ...

The use ... throughout society could well dwarf previous milestones in the information revolution."

#### What is an embedded system?

# Embedded Systems & Cyber-Physical Systems

"Dortmund" Definition: [Peter Marwedel]

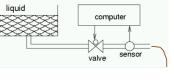

Embedded systems are information processing systems embedded into a larger product

Berkeley: [Edward A. Lee]:

Embedded software is software integrated with physical processes. The technical problem is managing time and concurrency in computational systems.

Definition: Cyber-Physical (cy-phy) Systems (CPS) are integrations of computation with physical processes [Edward A. Lee, 2006].

# Growing importance of embedded systems

the global mobile entertainment industry is now worth some \$32 bln...predicting average revenue growth of 28% for 2010 [www.itfacts.biz, July 8th, 2009]

- ..., the market for remote home health monitoring is expected to generate \$225 mln revenue in 2011, up from less than \$70 mln in 2006, according to Parks Associates. [www.itfacts.biz, Sep. 4th, 2007]

- Funding in the 7th European Framework

- Creation of the ARTEMIS Joint Undertaking in Europe

- Funding of CPS research in the US

- Joint education effort of Taiwanese Universities

technische universität dortmund

# Application areas and examples

These slides use Microsoft clip arts. Microsoft copyright restrictions apply.

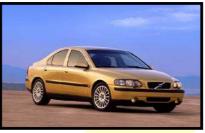

# **Automotive electronics**

Functions by embedded processing:

- ABS: Anti-lock braking systems

- ESP: Electronic stability control

- Airbags

Efficient automatic gearboxes

- Blind-angle alert systems

- ... etc ...

U technische universität dortmund

fi faki

ICD Curve Content of the second secon

Multiple networks

Body, engine, telematics, media, safety, ...

Multiple networked processors

© Jakob Engblom

# **Transportation (continued)**

### **Avionics**

- Flight control systems,

- Pilot information systems,

- . . . .

#### Railways

- Safety features contribute significantly to the total value of trains.

- Integrated systems are required, especially for high speeds.

- Example: European Rail Traffic Management System

Dependability is of outmost importance.

© http://www.moroccohighlights.com

- 9 -

# **Telecommunication & Consumer electronics**

### **Telecommunication:**

- Mobile phones (one of the fastest growing markets in the recent years),

- Geo-positioning systems,

- Closed systems for police, ambulances, rescue staff.

### **Consumer electronics:**

- TV sets.

- Smart personal assistants.

# IT in Healthcare, Biometric systems, security

| <ul> <li><b>IT in Healthcare</b></li> <li>Artificial eyes: <ul> <li>Connection to brain Previously at [www.dobelle.com]</li> <li>Translation into sound; [http://www.seeingwithsound.com/etumble.htm]</li> </ul> </li> <li>Tr</li> </ul> <li><b>Biometric systems</b> <ul> <li>Finger print sensors,</li> <li>Face recognition,</li> <li>Handwriting,</li> </ul></li> | <image/>                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                       | marwedel, - <b>11 -</b><br>natik 12, 2010 |

# Industrial automation & smart buildings

### Industrial automation

Factories, …

# Smart buildings

- Integrated cooling, lightning, room reservation, emergency handling, communication.

- Goal: "Zero-energy building"

- Expected contribution to fight against global warming

technische universität dortmund

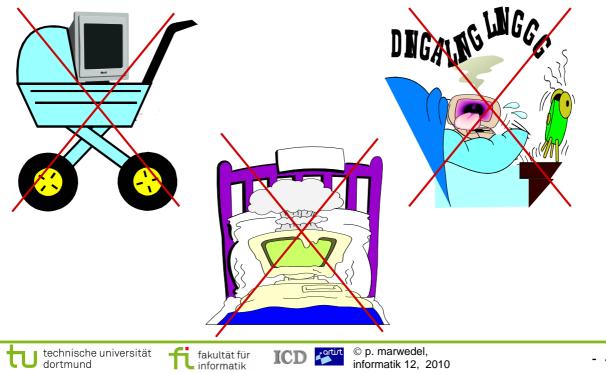

# Common characteristics

These slides use Microsoft clip arts Microsoft copyright restrictions apply.

# Dependability

dortmund

- ES must be dependable,

- **Reliability** *R(t)* = probability of system working correctly provided that is was working at *t*=0

- Maintainability M(d) = probability of system working correctly d time units after error occurred.

- Availability A(t): probability of system working at time t

- Safety: no harm to be caused

- Security: confidential and authentic communication

Even perfectly designed systems can fail if the assumptions about the workload and possible errors turn out to be wrong.

Making the system dependable must not be an afterthought, it must be considered from the very beginning. Kopetz

Graphics: © Alexandra Nolte, Gesine Marwedel, 2003

fakultät für

informatik

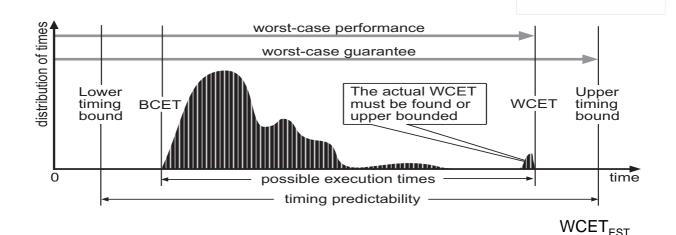

# **Real-time constraints**

- Many ES must meet real-time constraints

- "A real-time system must react to stimuli from the controlled object (or the operator) within the time interval **dictated** by the environment".

- For real-time systems, right answers arriving too late are wrong.

- "A real-time constraint is called hard, if not meeting that constraint could result in a catastrophe" [Kopetz, 1997].

- All other time-constraints are called **soft**.

- A guaranteed system response has to be explained without statistical arguments

### **Reactive & hybrid systems**

- Typically, ES are reactive systems:

*"A reactive system is one which is in continual interaction with is environment and executes at a pace determined by that environment"* [Bergé, 1995]

Behavior depends on input and current state.

*automata model appropriate, model of computable functions inappropriate.*

- Hybrid systems

(analog + digital parts).

### **Dedicated systems**

- 21 -

# It is not sufficient to consider ES just as a special case of software engineering

EE knowledge must be available, Walls between EE and CS must be torn down

The same for walls to other disciplines and more challenges ....

# Specification techniques for embedded systems

Graphics: © Alexandra Nolte, Gesine Marwedel, 2003

These slides use Microsoft clip arts. Microsoft copyright restrictions apply.

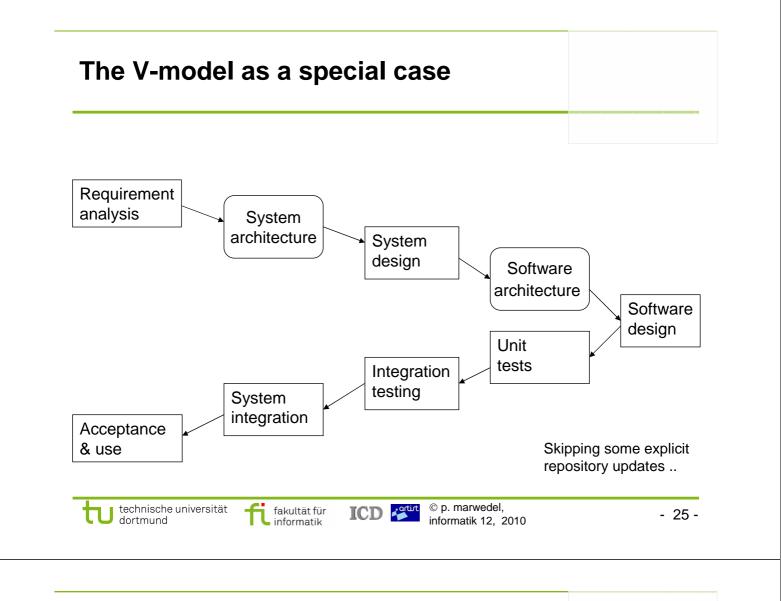

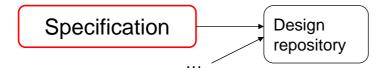

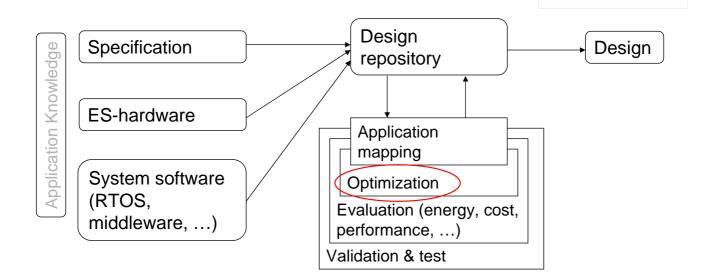

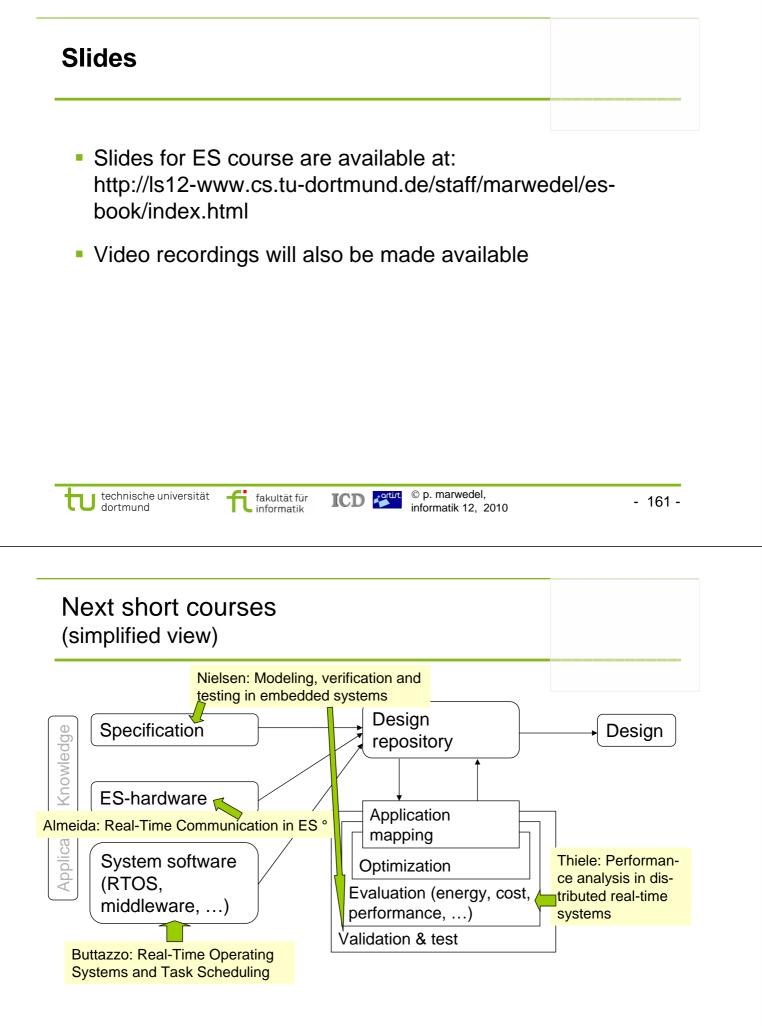

# Hypothetical design flow

Specification

Design repository

ES-hardware

Application mapping

System software (RTOS, middleware, ...)

Optimization Evaluation (energy, cost, performance, ...)

Validation & test

Generic loop: tool chains differ in the number and type of iterations

fakultät für

informatik

# Motivation for considering specs

- Why considering specs?

- If something is wrong with the specs, then it will be difficult to get the design right, potentially wasting a lot of time.

- Typically, we work with models of the system under design (SUD)

What is a model anyway?

### Models

**Definition:** "A model is a simplification of another entity, which can be a physical thing or another model. The model contains exactly those characteristics and properties of the modeled entity that are relevant for a given task. A model is minimal with respect to a task if it does not contain any other characteristics than those relevant for the task."

[Jantsch, 2004]:

Which requirements do we have for our models?

# Requirements for specification techniques (1): Hierarchy

Hierarchy Humans not capable to understand systems containing more than ~5 objects. Most actual systems require more objects Hierarchy (+abstraction)

Behavioral hierarchy Examples: states, processes, procedures.

Structural hierarchy Examples: processors, racks, printed circuit boards

| <ul> <li>Systems must be designed from<br/>components</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| <ul> <li>Must be "easy" to derive behavior from<br/>behavior of subsystems</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| Work of Sifakis, Thiele, Ernst,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| <ul><li>Concurrency</li><li>Synchronization and communication</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | - 29 - |

| <ul> <li>Synchronization and communication</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | - 29 - |

| <ul> <li>Synchronization and communication</li> <li>technische universität dortmund</li> <li>technische universität</li> <li>fakultät für informatik</li> <li>ICD</li> <li>p. marwedel, informatik 12, 2010</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | - 29 - |

| <ul> <li>Synchronization and communication</li> <li>U technische universität dortmund</li> <li>ICD P. marwedel, informatik 12, 2010</li> <li>Communication</li> <li>Communication</li> <li>Communication</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | - 29 - |

| <ul> <li>Synchronization and communication</li> <li>technische universität dortmund</li> <li>technische universität</li> <li>fakultät für informatik</li> <li>ICD</li> <li>p. marwedel, informatik 12, 2010</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | - 29 - |

| <ul> <li>Synchronization and communication</li> <li>U technische universität dortmund</li> <li>ICD P. marwedel, informatik 12, 2010</li> <li>Communication</li> <li>Communication</li> <li>Communication</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| <ul> <li>Synchronization and communication</li> <li>Center of the universität</li> <li>Center of the universit</li> <li< td=""><td>ns!</td></li<></ul> | ns!    |

| <ul> <li>Synchronization and communication</li> <li>U technische universität für dortmund</li> <li>fig fakultät für finformatik</li> <li>CD OP. marwedel, informatik 12, 2010</li> <li>Cequirements for specification schniques (3): Timing</li> <li>Timing behavior Essential for embedded and cy-phy system</li> <li>Additional information (periods, depend</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns!    |

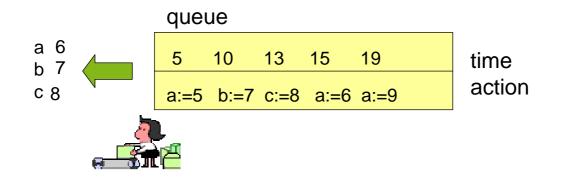

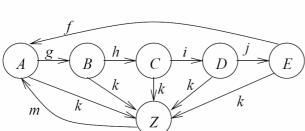

# Requirements for specification techniques (4): Support for reactive systems

- State-oriented behavior Required for reactive systems; classical automata insufficient.

- Event-handling (external or internal events)

- Exception-oriented behavior Not acceptable to describe exceptions for every state

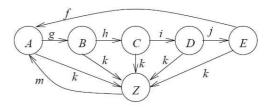

We will see, how all the arrows labeled k can be replaced by a single one.

#### **Requirements for specification** techniques (5) Presence of programming elements Executability (no algebraic specification) Support for the design of large systems (\$ OO) Domain-specific support Readability Portability and flexibility Termination Support for non-standard I/O devices Non-functional properties Support for the design of dependable systems No obstacles for efficient implementation Adequate model of computation What does it mean "to compute"? © p. marwedel, technische universität ICD fakultät für - 32 informatik 12, 2010 dortmund informatik

# Models of computation

#### What does it mean, "to compute"?

#### Models of computation define:

- Components and an execution model for computations for each component

- Communication model for exchange of information between components.

| technische universität<br>dortmund | fi fakultät für<br>informatik | ICD 🎺 | © p. marwedel,<br>informatik 12, 2010 | - 33 - |  |

|------------------------------------|-------------------------------|-------|---------------------------------------|--------|--|

| <br>Communicat                     | ion                           |       |                                       |        |  |

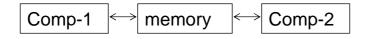

Shared memory

Variables accessible to several components/tasks.

Model mostly restricted to local systems.

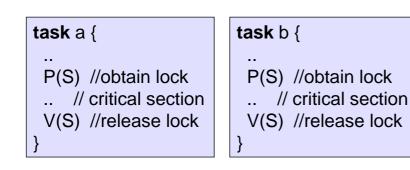

### Shared memory

Potential race conditions ( $\$ inconsistent results possible)  $\$  Critical sections = sections at which exclusive access to resource *r* (e.g. shared memory) must be guaranteed.

Race-free access to shared memory protected by S possible

P(S) and V(S) are **semaphore** operations, allowing at most *n* accesses, n = 1 in this case (mutex, lock)

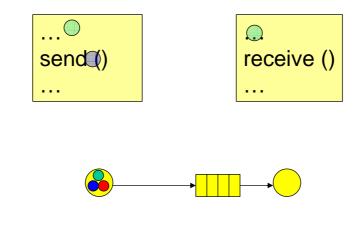

# Non-blocking/asynchronous message passing

Sender does not have to wait until message has arrived;

Potential problem: buffer overflow

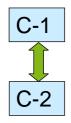

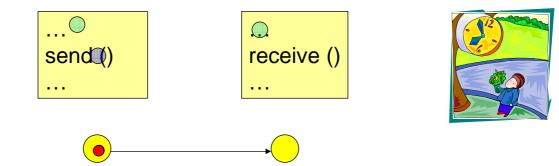

| Blocking/synchronous message<br>passing <i>rendez-vous</i> |  |

|------------------------------------------------------------|--|

|                                                            |  |

Sender will wait until receiver has received message

No buffer overflow, but reduced performance.

# Organization of computations within the components (1)

Finite state machines

- Data flow (models the flow of data in a distributed system)

- Differential equations

$$\frac{\partial^2 x}{\partial t^2} = b$$

# Organization of computations within the components (2)

Discrete event model

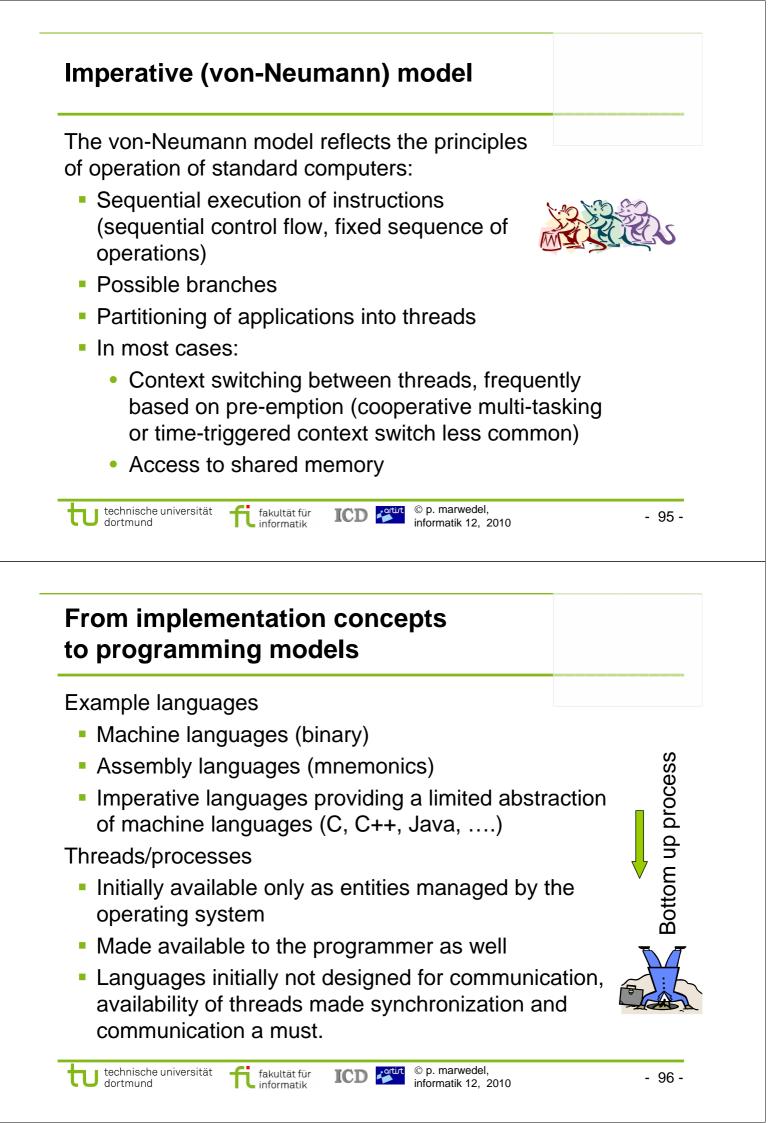

Von Neumann model

Sequential execution, program memory etc.

| technische universität<br>dortmund | fi fakultät für<br>informatik | informatik 12, 2010 | - 39 - |

|------------------------------------|-------------------------------|---------------------|--------|

|------------------------------------|-------------------------------|---------------------|--------|

technische universität dortmund

# Specification techniques for embedded systems

These slides use Microsoft clip arts. Microsoft copyright restrictions apply.

# Models of computation considered in this course

| Communication/<br>local computation | Shared<br>memory            | Mess<br>Synchronous | age passing<br>  Asynchronous          |

|-------------------------------------|-----------------------------|---------------------|----------------------------------------|

| Undefined                           | Plain tex                   | t, use cases        |                                        |

| components                          |                             | (Message) see       | quence charts                          |

| Communic. finite state machines     | StateCharts                 |                     | SDL                                    |

| Data flow                           | (Not useful)                |                     | Kahn networks, SDF                     |

| Petri nets                          |                             | C/E net             | s, P/T nets,                           |

| Discrete event<br>(DE) model        | VHDL*, Verilog,<br>SystemC, |                     | ental systems, e.g.<br>d DE in Ptolemy |

| Von-Neumann                         | C, C++, Java                | C, C++, Ja          | ava with libraries                     |

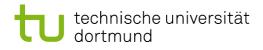

| model                               |                             | CSP, ADA            |                                        |

\* Classification is based on implementation of VHDL, Verilog, SystemC with central queue

Graphics: © Alexandra Nolte, Gesine Marwedel, 2003

#### Support for early design phases Informal text The system must respond to incoming calls. It must play the Uses cases welcome message followed by a Play next message beep and then start recording ... Erase last message User 9 Erase all messages (Message) sequence charts Caller Turn answering machine on :Caller Turn answering machine off :Phone :Answering machine Welcome+beep+voice mail type numbers signal call wait signal pick-up send welcome welcome beep transmit beep Similar to SW specification voice mail trans return hand-set signal end of ca Calling an answering machine © p. marwedel, technische universität fakultät für ICD - 43 informatik 12, 2010 dortmund informatik

# Models of computation considered in this course

|           | Communication/                  | Shared                      | Mess                   | age passing                            |

|-----------|---------------------------------|-----------------------------|------------------------|----------------------------------------|

|           | local computation               | memory                      | Synchronous            | Asynchronous                           |

|           | Undefined                       | Plain tex                   | t, use cases           |                                        |

|           | components                      |                             | (Message) see          | quence charts                          |

| $\langle$ | Communic. finite state machines | StateCharts                 | >                      | SDL                                    |

|           | Data flow                       | (Not useful)                |                        | Kahn networks, SDF                     |

|           | Petri nets                      |                             | C/E net                | s, P/T nets,                           |

|           | Discrete event<br>(DE) model    | VHDL*, Verilog,<br>SystemC, |                        | ental systems, e.g.<br>d DE in Ptolemy |

|           | Von-Neumann<br>model            | C, C++, Java                | C, C++, Ja<br>CSP, ADA | ava with libraries<br>                 |

\* Classification is based on implementation of VHDL, Verilog, SystemC with central queue

# **StateCharts**

Extending classical automata to model ES & CPS

- Adding timing with timed automata (

Friday tutorial)

- Adding hierarchy:

Complex graphs cannot be understood by humans.

Introduction of hierarchy StateCharts [Harel, 1987]

StateChart = the only unused combination of

"flow" or "state" with "diagram" or "chart"

Used here as a (prominent) example of a model of computation based on shared memory communication, appropriate only for local (non-distributed) systems

| tu technische universität fit fakultät für fakultät für dortmund © p. marwedel, informatik 12, 2010 | - 45 - |

|-----------------------------------------------------------------------------------------------------|--------|

|-----------------------------------------------------------------------------------------------------|--------|

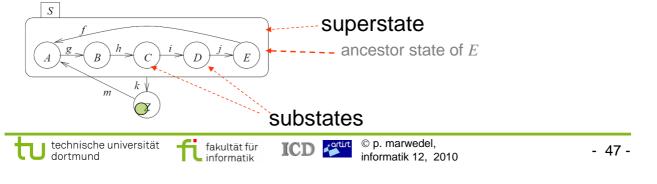

# Introducing hierarchy

FSM will be **in** exactly one of the substates of *S* if *S* is **active** (either in *A* or in *B* or ..)

fakultät für

informatik

technische universität

dortmund

# Definitions

- Current states of FSMs are also called active states.

- States which are not composed of other states are called basic states.

- States containing other states are called super-states.

- For each basic state s, the super-states containing s are called ancestor states.

- Super-states S are called **OR-super-states**, if exactly one of the sub-states of S is active whenever S is active.

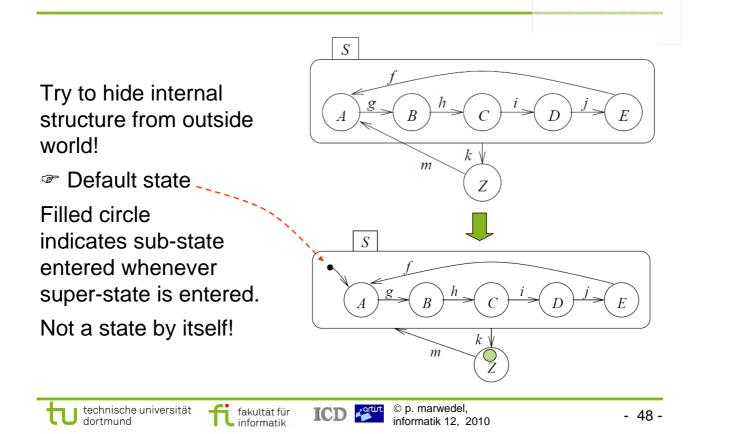

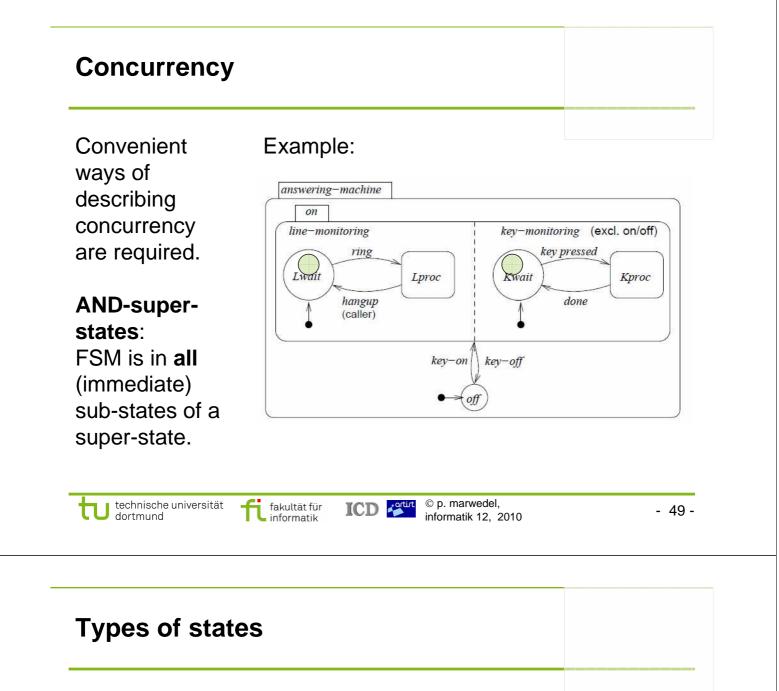

### Default state mechanism

In StateCharts, states are either

- basic states, or

- AND-super-states, or

- OR-super-states.

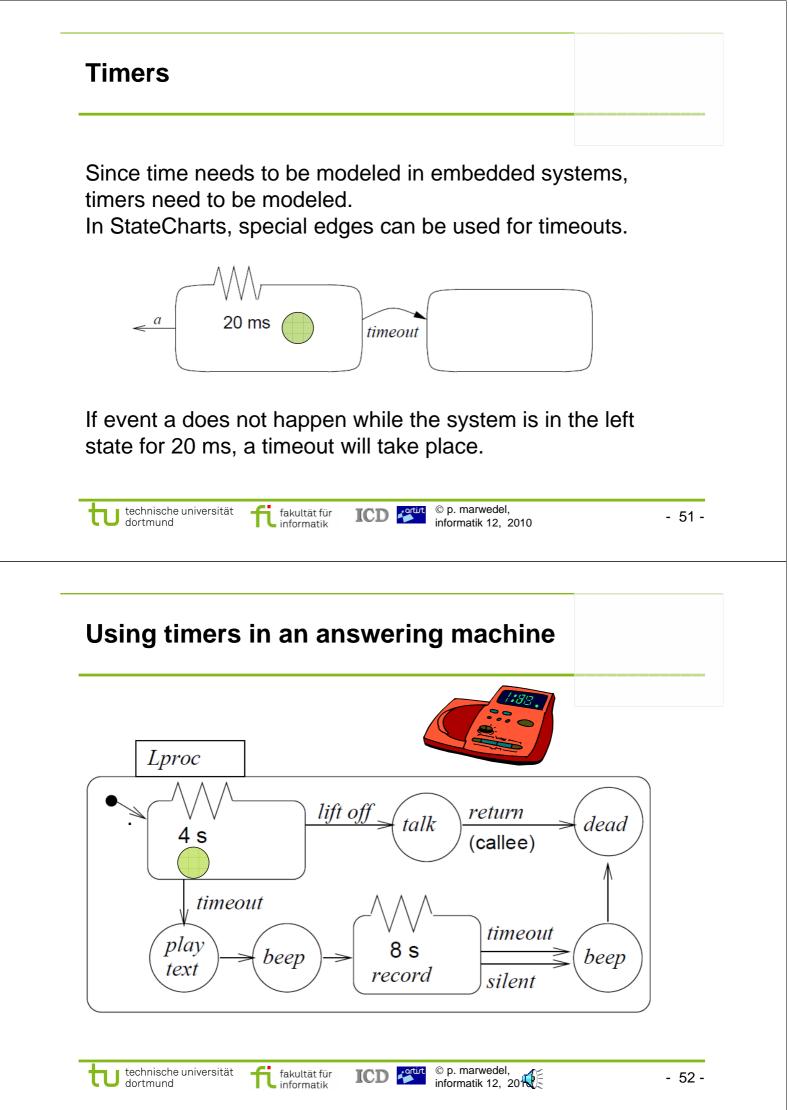

# The StateCharts simulation phases (StateMate Semantics)

How are edge labels evaluated?

Three phases:

- 1. Effect of external changes on events and conditions is evaluated,

- 2. The set of transitions to be made in the current step and right hand sides of assignments are computed,

- 3. Transitions become effective, variables obtain new values.

Separation into phases 2 and 3 guarantees and reproducible behavior.

| technische universität<br>dortmund | fi fakultät für ICD 🕻 | © p. marwedel,<br>informatik 12, 2010 | - 53 - |

|------------------------------------|-----------------------|---------------------------------------|--------|

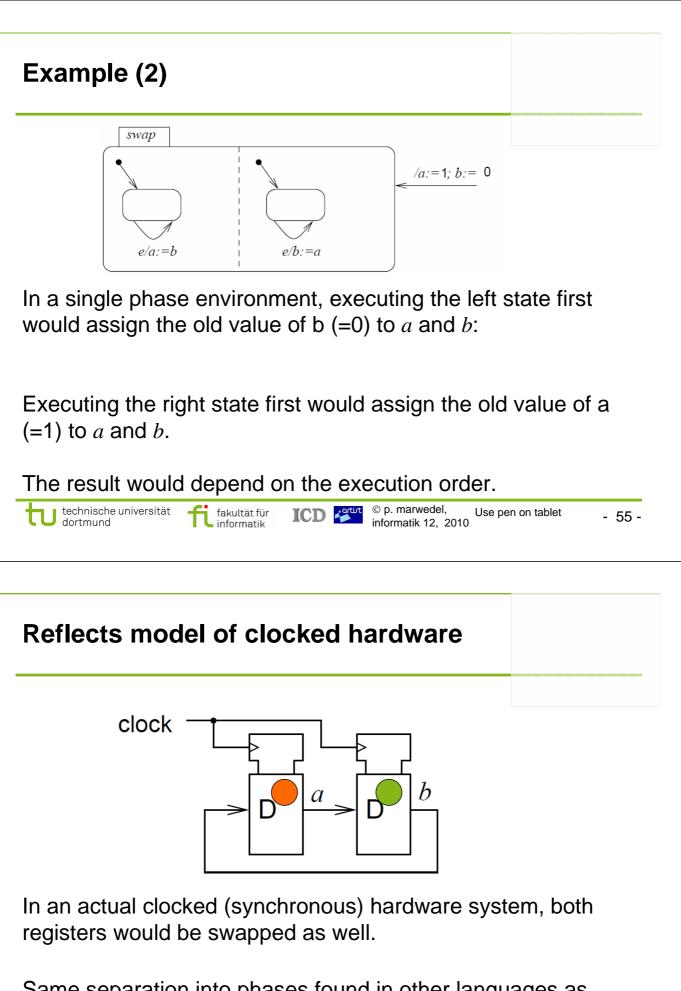

| Example                            |                       |                                       |        |

| swap                               | •                     | / <i>a</i> :=1; <i>b</i> := 0         |        |

| e/a:=b                             | e/b:=a                | /a:-1; b:= 0                          |        |

In phase 2, variables a and b are assigned to temporary variables:

In phase 3, these are assigned to *a* and b.

As a result, variables a and b are swapped.

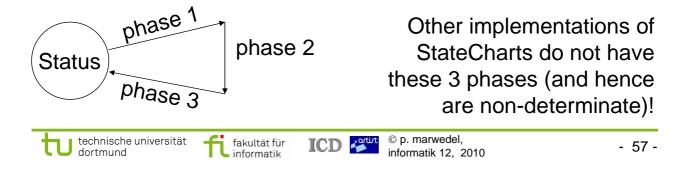

Same separation into phases found in other languages as well, especially those that are intended to model hardware.

technische universität

dortmund

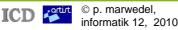

# Steps

Execution of a StateMate model consists of a sequence of (status, step) pairs

Status Step Status Step Status Step Status

Status= values of all variables + set of events + current time Step = execution of the three phases (StateMate semantics)

### **Other semantics**

Several other specification languages for hierarchical state machines (UML, ...) do not include the three simulation phases.

These correspond more to a SW point of view with no synchronous clocks.

Some systems allow turning the multi-phased simulation on and off.

# Broadcast mechanism

Values of variables are visible to all parts of the StateChart model New values become effective in phase 3 of the current step and are obtained by all parts of the model in the following step.

StateCharts implicitly assumes a broadcast mechanism for variables

(→ implicit *shared memory communication*

- -other implementations would be very inefficient -).

- StateCharts is appropriate for local control systems (③), but not for distributed applications for which updating variables might take some time (③).

# **Evaluation of StateCharts**

#### **Pros:**

- Hierarchy allows arbitrary nesting of AND- and OR-super states.

- (StateMate-) Semantics defined in a follow-up paper to original paper.

- Large number of commercial simulation tools available (StateMate, StateFlow, ...)

- Available "back-ends" translate StateCharts into C or VHDL, thus enabling software or hardware implementations.

### Cons:

- Not useful for distributed applications,

- No program constructs,

- No description of non-functional behavior,

- No object-orientation,

- No description of structural hierarchy.

# Models of computation considered in this course

| Communication/                                                                           | Shared                                                                                  | Messa         | ige passing        |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------|--------------------|

| local computation                                                                        | memory                                                                                  | Synchronous   | Asynchronous       |

| Undefined                                                                                | Plain tex                                                                               | t, use cases  |                    |

| components                                                                               |                                                                                         | (Message) seq | uence charts       |

| Communic. finite state machines                                                          | StateCharts                                                                             |               | SDL                |

| Data flow                                                                                | (Not useful)                                                                            |               | Kahn networks, SDF |

| Petri nets                                                                               |                                                                                         | C/E nets      | , P/T nets,        |

| Discrete event<br>(DE) model                                                             | VHDL*, Verilog,<br>SystemC,Only experimental systems, e.g.<br>distributed DE in Ptolemy |               | , U                |

| Von-Neumann                                                                              | C, C++, Java                                                                            | C, C++, Jav   | va with libraries  |

| model                                                                                    |                                                                                         | CSP, ADA      |                    |

| * Classification is based on implementation of VHDL, Verilog, SystemC with central queue |                                                                                         |               |                    |

| technische universität für fakultät für ICD informatik © p. marwedel,<br>dortmund - 61 - |                                                                                         |               |                    |

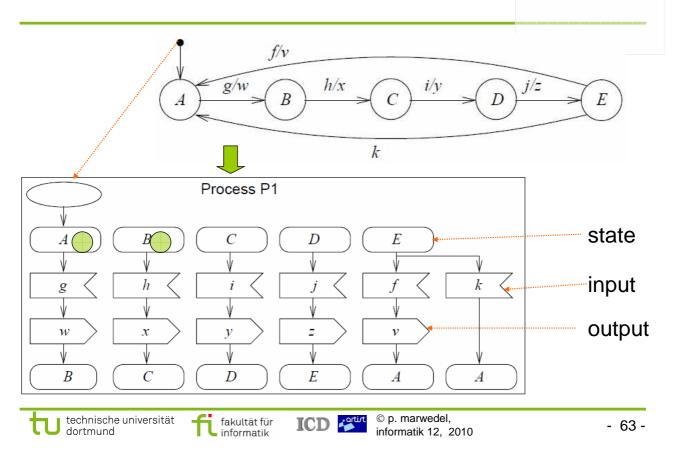

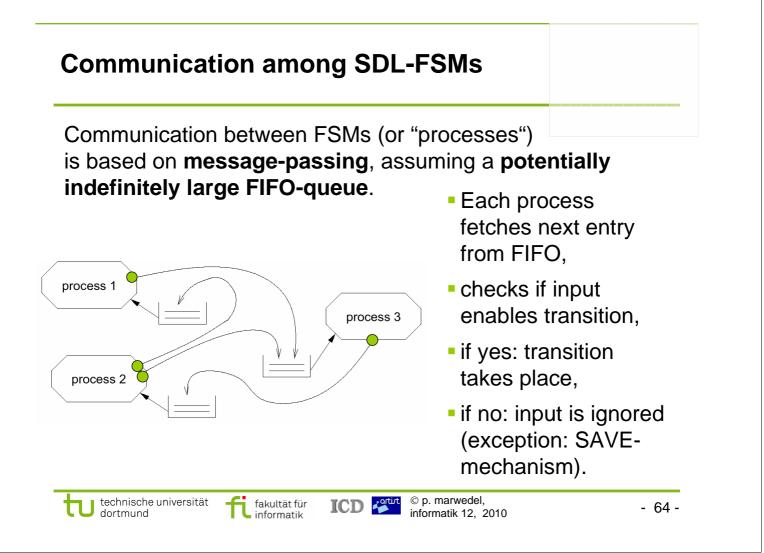

# SDL

Language designed for distributed systems.

- Dates back to early 70s,

- Formal semantics defined in the late 80s,

- Defined by ITU (International Telecommunication Union): Z.100 recommendation in 1980 Updates in 1984, 1988, 1992, 1996 and 1999

- Provides textual and graphical formats to please all users,

- Just like StateCharts, it is based on the CFSM model of computation; each FSM is called a process,

- However, it uses message passing instead of shared memory for communications,

- SDL supports operations on data.

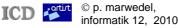

# SDL-representation of FSMs/processes

# **Determinate?**

Let tokens be arriving at FIFO at the same time: <sup>C</sup>Order in which they are stored, is unknown:

All orders are legal: <sup>(27)</sup> simulators can show different behaviors for the same input, all of which are correct.

# Models of computation considered in this course

| Communication/                  | Shared                      | Message passing                                           |  |

|---------------------------------|-----------------------------|-----------------------------------------------------------|--|

| local computation               | memory                      | Synchronous   Asynchronous                                |  |

| Undefined                       | Plain text, use cases       |                                                           |  |

| components                      |                             | (Message) sequence charts                                 |  |

| Communic. finite state machines | StateCharts                 | SDL                                                       |  |

| Data flow                       | (Not useful)                | Kahn networks SDF                                         |  |

| Petri nets                      |                             | C/E nets, P/T nets,                                       |  |

| Discrete event<br>(DE) model    | VHDL*, Verilog,<br>SystemC, | Only experimental systems, e.g. distributed DE in Ptolemy |  |

| Von-Neumann<br>model            | C, C++, Java                | C, C++, Java with libraries<br>CSP, ADA                   |  |

\* Classification is based on implementation of VHDL, Verilog, SystemC with central queue

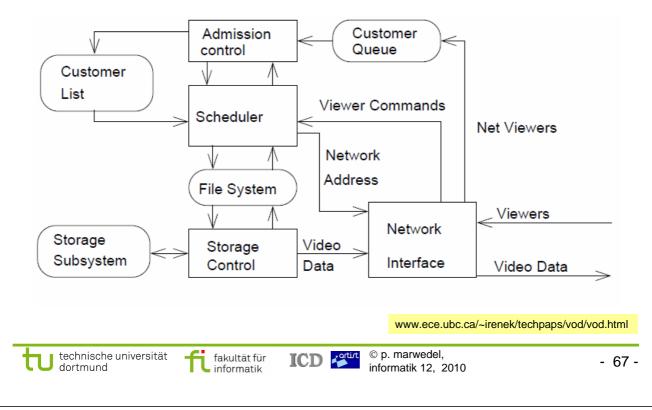

# Data flow as a "natural" model of applications

Example: Video on demand system

# Data flow modeling

Definition: Data flow modeling is ...

"the process of identifying, modeling and documenting how data moves around an information system. Data flow modeling examines

- processes (activities that transform data from one form to another),

- data stores (the holding areas for data),

- external entities (what sends data into a system or receives data from a system, and

- data flows (routes by which data can flow)".

[Wikipedia: Structured systems analysis and design method. http://en.wikipedia.org/wiki/Structured Systems Analysis and Design Methodology, 2010 (formatting added)].

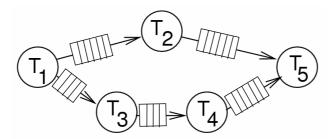

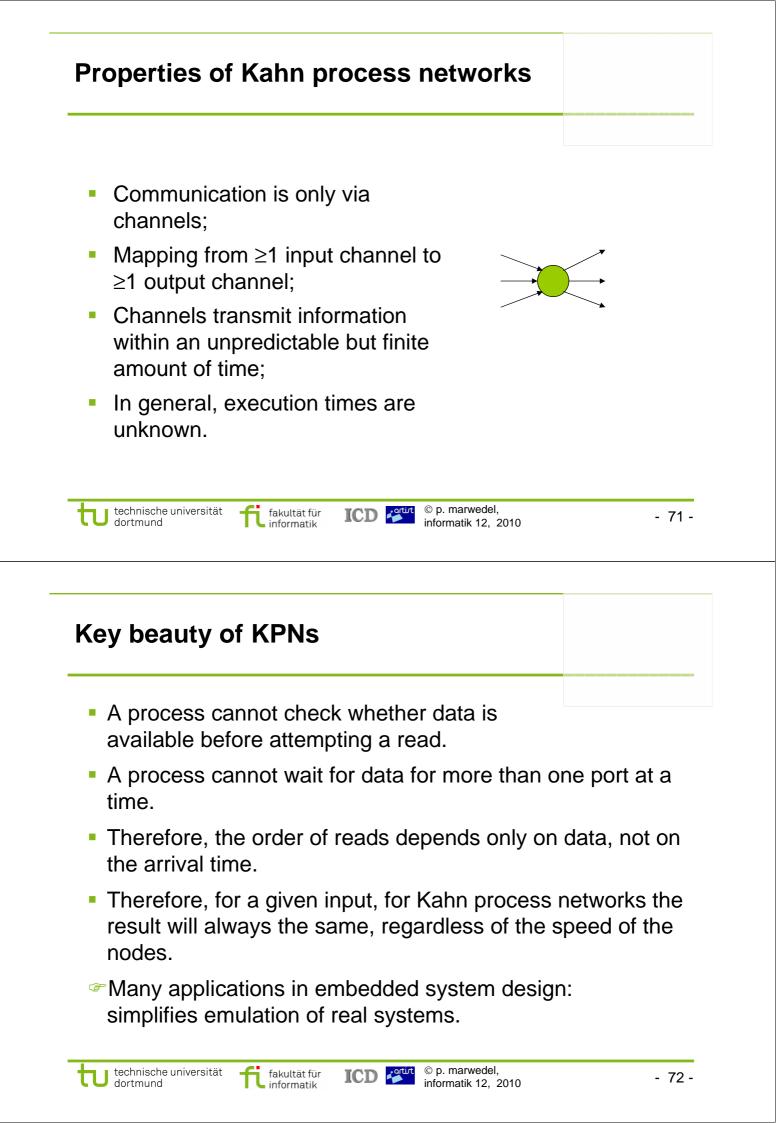

# Kahn process networks

- Each component is a program/task/process, not an FSM

- Communication is by FIFOs; no overflow considered

- *regional writes never have to wait.*

- reads wait if FIFO is empty.

Only one sender and one receiver per FIFO no SDL-like conflicts at FIFOs

| technische universität<br>dortmund | fi fakultät für<br>informatik | ICD | © p. marwedel,<br>informatik 12, 2010 | - 69 - |

|------------------------------------|-------------------------------|-----|---------------------------------------|--------|

|                                    |                               |     |                                       |        |

# **Example**

```

Process f(in int u, in int v, out int w){

int i; bool b = true;

for (;;) {

i= b ? wait(u) : wait(v);

//wait returns next token in FIFO, waits if empty

send (i,w); //writes a token into a FIFO w/o blocking

b = !b;

}

```

© R. Gupta (UCSD), W. Wolf (Princeton), 2003

#### **Models of computation** considered in this course

| Communication/                  | Shared                      | Mess                    | age passing                            |

|---------------------------------|-----------------------------|-------------------------|----------------------------------------|

| local computation               | memory                      | Synchronous             | Asynchronous                           |

| Undefined                       | Plain tex                   | t, use cases            |                                        |

| components                      |                             | (Message) see           | quence charts                          |

| Communic. finite state machines | StateCharts                 |                         | SDL                                    |

| Data flow                       | (Not useful)                |                         | Kahn networks, SDF                     |

| Petri nets                      |                             | C/E net                 | s, P/T nets,                           |

| Discrete event<br>(DE) model    | VHDL*, Verilog,<br>SystemC, |                         | ental systems, e.g.<br>d DE in Ptolemy |

| Von-Neumann                     | C, C++, Java                | C, C++, Ja              | ava with libraries                     |

| model                           |                             | CSP, ADA                |                                        |

| * Classification is based or    | implementation of VHDL,     | Verilog, SystemC with c | entral queue                           |

ICD

fakultät für

informatik

© p. marwedel,

informatik 12, 2010

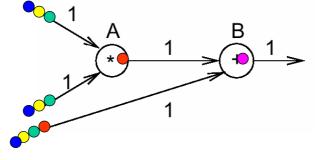

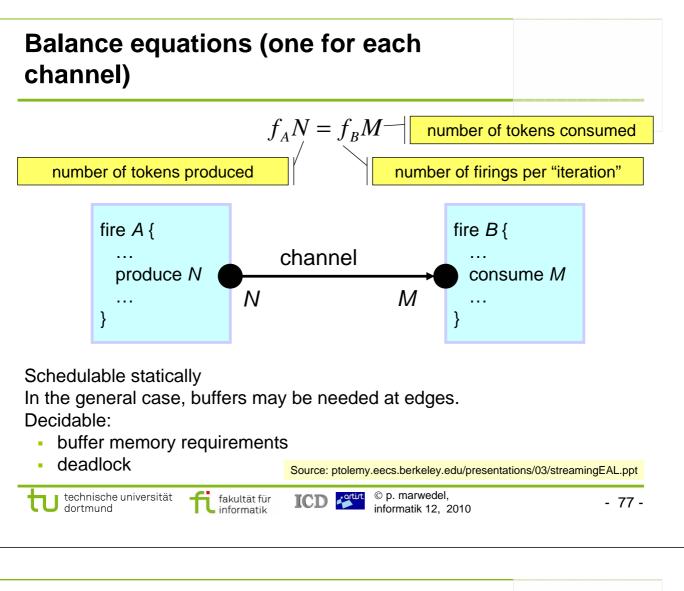

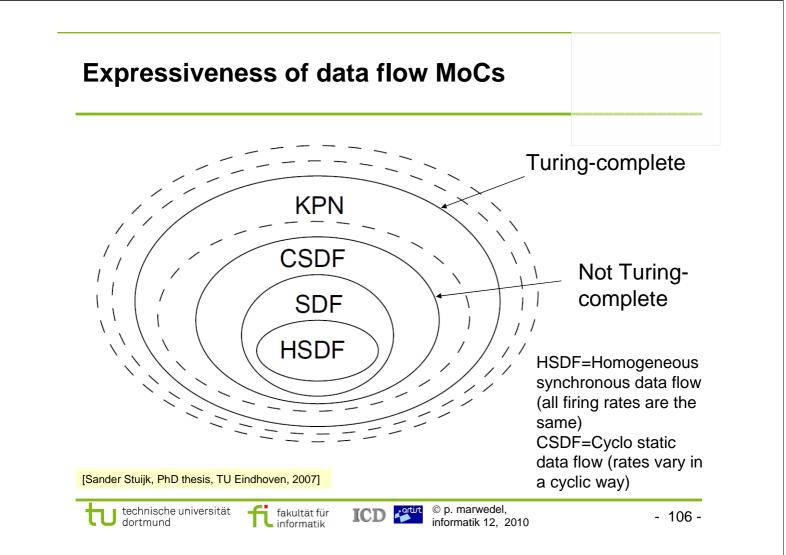

#### SDF

Less computationally powerful, but easier to analyze:

Synchronous data flow (SDF).

Again using asynchronous message passing.

informatik

- 73 -

#### Synchronous data flow (SDF)

Synchronous data flow =

global clock controlling "firing" of nodes

Asynchronous message passing=

tasks do not have to wait until output is accepted.

In the general case, a number of tokens can be produced/ consumed per firing; firing rate depends on # of tokens ...

#### **Parallel Scheduling of SDF Models** SDF is suitable for automated mapping onto Many scheduling parallel optimization problems can be processors and formulated. Some synthesis of can be solved, too! parallel circuits. Sequential Parallel Source: ptolemy.eecs.berkeley.edu/presentations/03/streamingEAL.ppt © p. marwedel, technische universität ICD fakultät für - 76 informatik 12, 2010 dortmund informatik

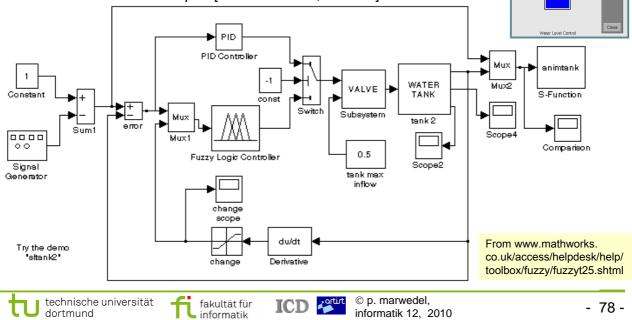

**Semantics?** "Simulink uses an idealized timing model for block execution and communication. Both happen infinitely fast at exact points in simulated time. Thereafter, simulated time is advanced by exact time steps. All values on edges are constant in between time steps." [Nicolae Marian, Yue Ma]

#### Summary

Specifications and Modeling

- Early phases

- Text

- Use Cases

- (Message) Sequence Charts

- FSM-based models

- Shared memory-based (StateCharts)

- Message passing-based (SDL)

- Data flow

- Kahn process networks

- Synchronous data flow

#### **Questions?**

fi fakultät für informatik

#### Specifications and Modeling (2)

These slides use Microsoft clip arts. Microsoft copyright restrictions apply.

## Models of computation considered in this course

| Communication/<br>local computation | Shared memory   |               | age passing         |

|-------------------------------------|-----------------|---------------|---------------------|

| local computation                   | memory          | Synchronous   | Asynchronous        |

| Undefined                           | Plain tex       | t, use cases  |                     |

| components                          |                 | (Message) see | quence charts       |

| Communic. finite state machines     | StateCharts     |               | SDL                 |

| State machines                      |                 |               |                     |

| Data flow                           | (Not useful)    |               | Kahn networks, SDF  |

| Petri nets                          |                 | C/E net       | s, P/T nets,        |

| Discrete event                      | VHDL*, Verilog, | Only experim  | ental systems, e.g. |

| (DE) model                          | SystemC,        | distributed   | d DE in Ptolemy     |

| Von-Neumann                         | C, C++, Java    | C, C++, Ja    | ava with libraries  |

| model                               |                 | CSP, ADA      |                     |

\* Classification is based on implementation of VHDL, Verilog, SystemC with central queue

Graphics: © Alexandra Nolte, Gesine Marwedel, 2003

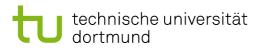

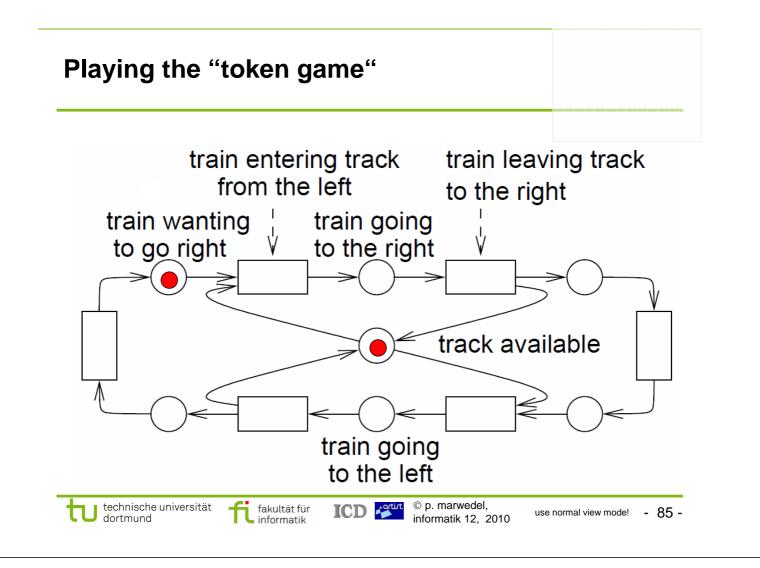

#### Introduction Introduced in 1962 by Carl Adam Petri in his PhD thesis. Focus on modeling causal dependencies; no global synchronization assumed (message passing only). Key elements: Conditions Either met or no met. Events May take place if certain conditions are met. Flow relation Relates conditions and events. Conditions, events and the flow relation form a **bipartite graph** (graph with two kinds of nodes). © p. marwedel, technische universität ICD fakultät für - 83 informatik 12, 2010 dortmund informatik **Example: Synchronization at single** track rail segment train entering track train leaving track from the left to the right train going train wanting to go right to the right "Preconditions" track available train going to the left single-laned

#### Conflict for resource "track"

## Models of computation considered in this course

| Communication/                  | Shared                      | Mess          | age passing                            |

|---------------------------------|-----------------------------|---------------|----------------------------------------|

| local computation               | memory                      | Synchronous   | Asynchronous                           |

| Undefined                       | Plain tex                   | t, use cases  |                                        |

| components                      |                             | (Message) see | quence charts                          |

| Communic. finite state machines | StateCharts                 |               | SDL                                    |

| Data flow                       | (Not useful)                |               | Kahn networks, SDF                     |

| Petri nets                      |                             | C/E net       | s, P/T nets, …                         |

| Discrete event<br>(DE) model    | VHDL*, Verilog,<br>SystemC, |               | ental systems, e.g.<br>d DE in Ptolemy |

| Von-Neumann                     | C, C++, Java                | C, C++, Ja    | ava with libraries                     |

| model                           |                             | CSP, ADA      |                                        |

\* Classification is based on implementation of VHDL, Verilog, SystemC with central queue

# HDLs using discrete event (DE) semantics Used in hardware description languages (HDLs): Description of concurrency is a must for HW description languages! • Many HW components are operating concurrently • Typically mapped to "processes" • These processes communicate via "signals" • Examples: • MIMOLA [Zimmermann/Marwedel], ~1975 ... • VHDL (very prominent example in DE modeling) One of the 3 most important HDLs:

VHDL, Verilog, SystemC Definition started in 1980, updated every 5 years

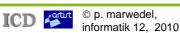

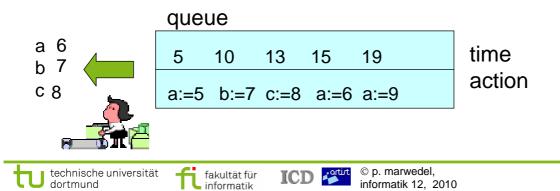

#### **Discrete event semantics**

Basic discrete event (DE) semantics

- Queue of future actions, sorted by time

- Loop:

- Fetch next entry from queue

- Perform function as listed in entry

- May include generation of new entries

- Until termination criterion = true

#### Simple example (VHDL notation)

Processes will wait for changes on their input ports.

If they arrive, processes will wake up, compute their code and deposit changes of output signals in the event queue and wait for the next event.

If all processes wait, the next entry will be taken from the event queue.

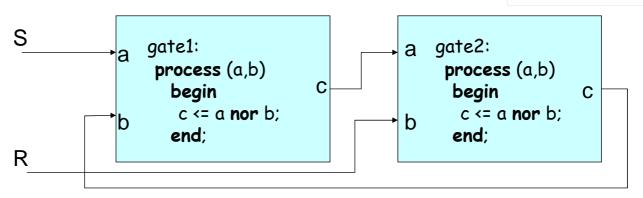

# VHDL processes

Delays allowed: process (a,b) begin c <= a nor b after 10 ns; end;

Equivalent to

#### process

begin

c <= a nor b after 10 ns;

wait on a,b;

end;</pre>

- =: signal assignment operator

- Each executed signal assignment will result in adding entries in the projected waveform, as indicated by the (optional) delay time

- Implicit loop around the code in the body

- Sensitivity lists are a shorthand for a single wait on-statement at the end of the process body

| S<br>R | 011   |      |        | $\mathcal{I}$ | gate1:<br>process (S,Q)<br>begin<br>nQ <= S nor Q;<br>end;<br>gate2:<br>process (R,nQ)<br>begin<br>Q <= R nor nQ; |

|--------|-------|------|--------|---------------|-------------------------------------------------------------------------------------------------------------------|

| C      | )ns 0 | ns+δ | 0ns+28 | 0ns+3δ        | end;                                                                                                              |

| R      | 1     | 1    | 1      | 1             |                                                                                                                   |

| S      | 0     | 0    | 0      | 0             | $\delta$ cycles reflect the fact that no real                                                                     |

| 9      |       |      | •      |               | gate comes with zero delay.                                                                                       |

| 2      | 1     | 0    | 0      | 0             | 🖙 should delay-less signal                                                                                        |

## Models of computation considered in this course

| <b>Communication/</b>           | Shared                      | Mess          | age passing                          |

|---------------------------------|-----------------------------|---------------|--------------------------------------|

| local computation               | memory                      | Synchronous   | Asynchronous                         |

| Undefined                       | Plain tex                   | t, use cases  |                                      |

| components                      |                             | (Message) see | quence charts                        |

| Communic. finite state machines | StateCharts                 |               | SDL                                  |

| Data flow                       | (Not useful)                |               | Kahn networks, SDF                   |

| Petri nets                      |                             | C/E net       | s, P/T nets,                         |

| Discrete event<br>(DE) model    | VHDL*, Verilog,<br>SystemC, |               | ental systems, e.g.<br>DE in Ptolemy |

| Von-Neumann                     | C, C++, Java                | C, C++, Ja    | ava with libraries                   |

| model                           |                             | CSP, ADA      |                                      |

\* Classification is based on implementation of VHDL, Verilog, SystemC with central queue

#### **Communication via shared memory**

Several threads access the same memory

- Very fast communication technique (no extra copying)

- Potential race conditions:

thread a { u = 1; if  $u < 5 \{u = u + 1; ..\}$

thread b { u = 5

Context switch after the test could result in u == 6.

results possible

Critical sections = sections at which exclusive access to resource r (e.g. shared memory) must be guaranteed

#### Imperative model should be supported by:

- mutual exclusion for critical sections

- cache coherency protocols

#### **Communication/synchronization**

- Special communication libraries for ES & CPS

- OSEK/VDX COM

- ...

- Adopted communication libraries for general computing

- CORBA (Common Object Request Broker Architecture)

- Message passing interface (MPI)

- Posix threads (PThreads)

- OpenMP

- UPnP, DPWS, JXTA, ...

Frequently not easy to adjust to real-time requirements

#### Deadlocks

Deadlocks can happen, if the following 4 conditions are met [Coffman, 1971]:

- Mutual exclusion: a resource that cannot be used by >1 thread at a time

- Hold and wait: thread already holding resources may request new resources

- No preemption: Resource cannot be forcibly removed from threads, they can be released only by the holding threads

- Circular wait: ≥ 2 threads form a circular chain where each thread waits for a resource that the next thread in the chain holds

There is no general, always applicable technique for turning one of these conditions false.

In non-safety-critical software, it is "ok" to ensure that deadlocks are "sufficiently" infrequent.

#### **Mutual exclusion in Java**

"The Observer pattern defines a one-to-many dependency between a subject object and any number of observer objects so that when the subject object changes state, all its observer objects are notified and updated automatically."

Erich Gamma, Richard Helm, Ralph Johnson, John Vlissides: *Design Patterns*, Addision-Wesley, 1995

#### Mutexes using monitors are minefields public synchronized void addListener(listener) {...} public synchronized void setValue(newvalue) { myvalue=newvalue; x calls addListener lock ValueChai requests for (int i=0; i<mylisteners.length; i++) { held myListeners[i].valueChanged(newvalue) lock } valueChanged() may attempt to acquire a lock on some other object and stall. If the holder of that lock calls addListener(): deadlock!

#### **Problems with imperative languages** and shared memory

- Potential deadlocks

- Specification of total order of operations is an overspecification. A partial order would be sufficient. The total order reduces the potential for optimizations

- Timing cannot be specified

- Access to shared memory leads to anomalies, that have to be pruned away by mutexes, semaphores, monitors

- Access to shared, protected resources leads to priority inversion

- Termination in general undecidable

- Preemptions at any time complicate timing analysis

#### Comparison of models

Graphics: © Alexandra Nolte, Gesine Marwedel, 2003

These slides use Microsoft clip arts. Microsoft copyright restrictions apply.

#### Mixing models may require formal models of MoCs

#### Mixing models of computation: Ptolemy

Ptolemy (UC Berkeley) is an environment for simulating multiple models of computation.

http://ptolemy.berkeley.edu/

Available examples are restricted to a subset of the supported models of computation.

#### Mixing MoCs: Ptolemy

(Focus on executable models; "mature" models only)

| Communication/<br>local computations | Shared<br>memory | Message passing<br>Synchronous   Asynchronous       |

|--------------------------------------|------------------|-----------------------------------------------------|

| Communicating finite state machines  | FSM, sync        | chronous/reactive MoC                               |

| Data flow                            |                  | Kahn networks, SDF, dynamic dataflow, discrete time |

| Petri nets                           |                  |                                                     |

| Discrete event (DE) model            | DE               | Experimental distributed DE                         |

| Von Neumann model                    |                  | CSP                                                 |

| Wireless                             | Special r        | model for wireless communication                    |

| Continuous time                      | Р                | artial differential equations                       |

## Mixing models of computation: UML (Focus on support of early design phases)

| Communication/<br>local computations | Shared<br>memory           | Message<br>Synchronous                | passing<br>Asynchronous |

|--------------------------------------|----------------------------|---------------------------------------|-------------------------|

| Undefined                            | Use cases                  |                                       |                         |

| components                           |                            | Sequence chart                        | s, timing diagrams      |

| Communicating finite state machines  | State<br>diagrams          |                                       |                         |

| Data flow                            | (Not useful)               | Data flow                             |                         |

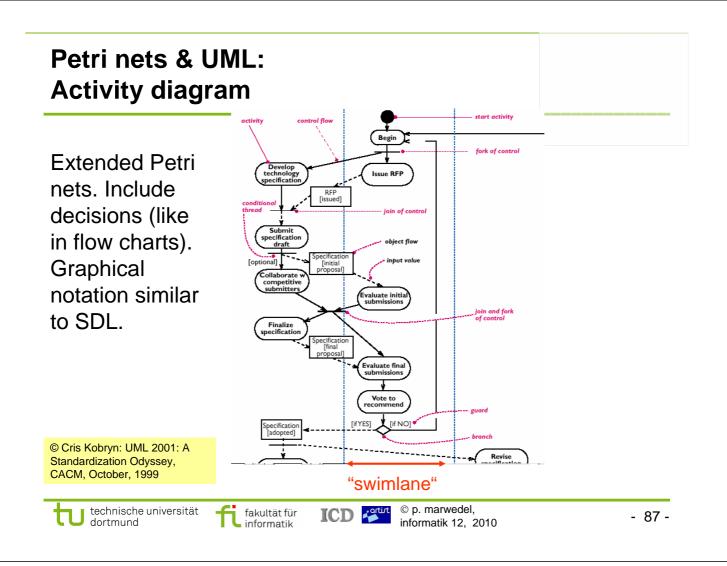

| Petri nets                           |                            | Activity                              | / charts                |

| Discrete event (DE)<br>model         | -                          |                                       | -                       |

| Von Neumann model                    | -                          |                                       | -                       |

|                                      |                            |                                       |                         |

| tu technische universität fi         | fakultät für<br>informatik | © p. marwedel,<br>informatik 12, 2010 | - 111 -                 |

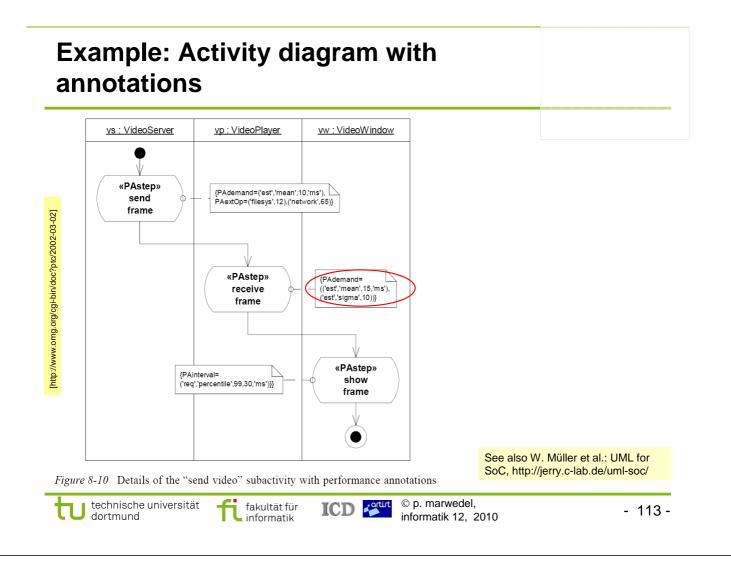

#### UML for embedded systems?

Initially not designed for real-time.

Initially lacking features:

- Partitioning of software into tasks and processes

- specifying timing

- specification of hardware components

Projects on defining profiles for embedded/real-time systems

- Schedulability, Performance and Timing Analysis

- SysML (System Modeling Language)

- UML Profile for SoC

- Modeling and Analysis of Real-Time Embedded Systems

- UML/SystemC, …

Profiles may be incompatible

#### ICD Curtic © p. marwedel, informatik 12, 2010

#### What's the bottom line?

- The prevailing technique for writing embedded SW has inherent problems; some of the difficulties of writing embedded SW are not resulting from design constraints, but from the modeling.

- However, there is no ideal modeling technique which fits in all cases.

- The choice of the technique depends on the application.

- Check code generation from non-imperative models

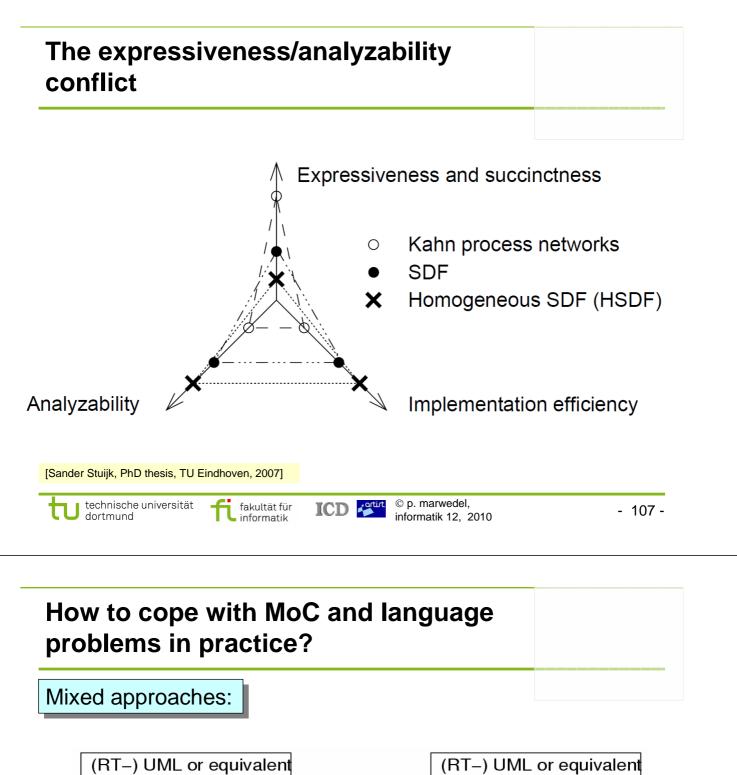

- There is a tradeoff between the power of a modeling technique and its analyzability.

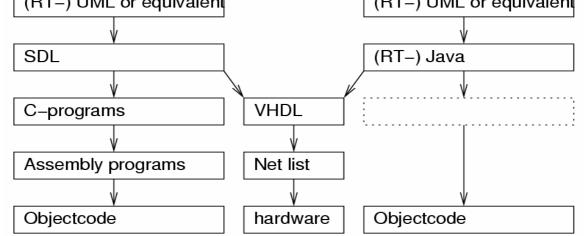

- It may be necessary to combine modeling techniques.

- In any case, open your eyes & think about the model before you write down your spec! Be aware of pitfalls.

You may be forced, to use imperative models, but you can still implement, for example, finite state machines or KPNs in Java.

fakultät für informatik

#### Summary

- Imperative Von-Neumann models

- Problems resulting from access to shared resources and mutual exclusion (e.g. potential deadlock)

- Communication built-in or by libraries

- Comparison of models

- Expressiveness vs. analyzability

- Process creation

- Mixing models of computation

- Ptolemy & UML

- Using FSM and KPN models in imperative languages, etc.

| technische universität fi fakultät für ICD 🚰 © p. marwedel,<br>dortmund - 11 | 15 - |  |

|------------------------------------------------------------------------------|------|--|

|------------------------------------------------------------------------------|------|--|

#### Structure of this course

- energy efficiency

- size

- cost

- other attributes (volatile vs. persistent, etc)

ICD

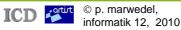

Rixner's et al. model [HPCA'00], Technology of 0.18 µm

Source and © H. Valero, 2001

memory hierarchy

These slides use Microsoft clip arts. Microsoft copyright restrictions apply.

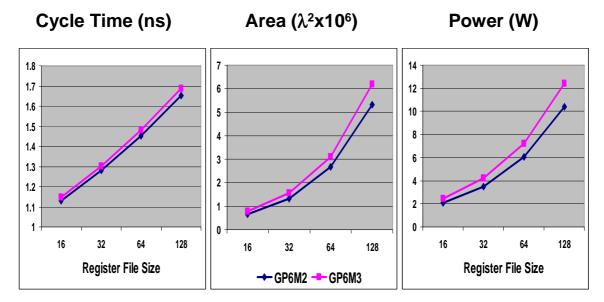

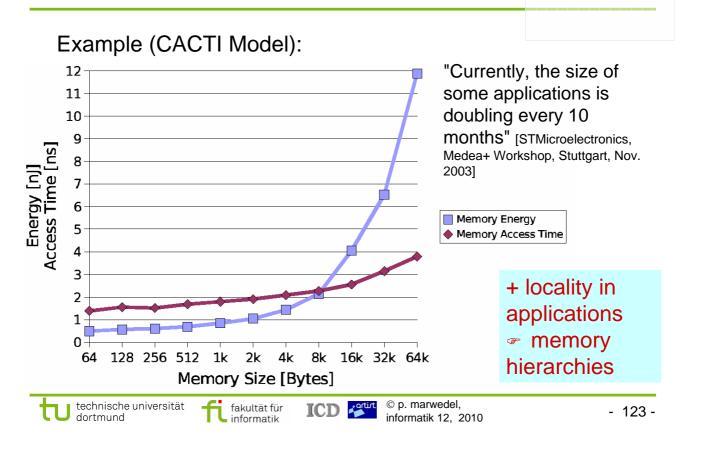

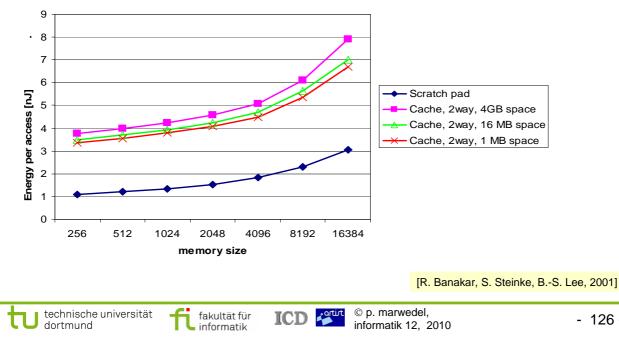

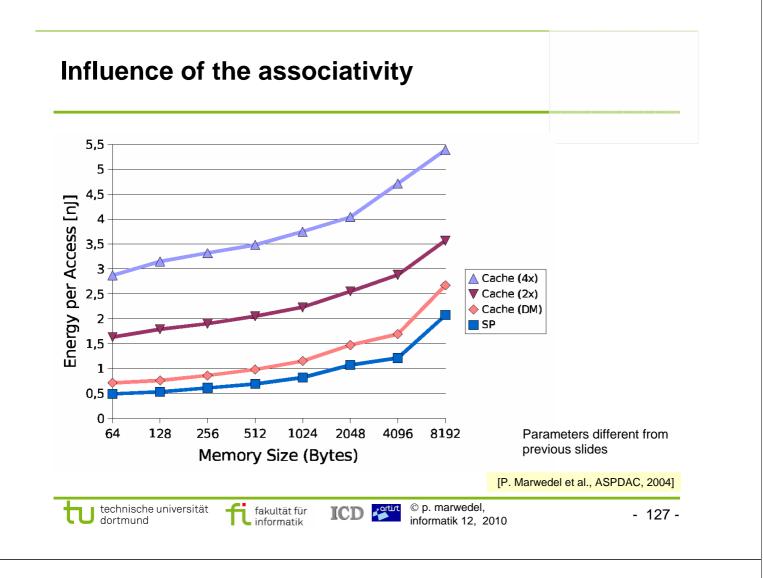

## Access times and energy consumption increases with the size of the memory

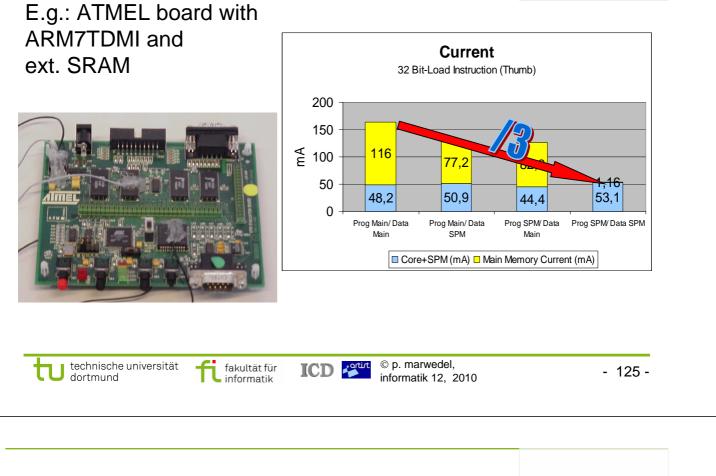

#### **Comparison of currents using** measurements

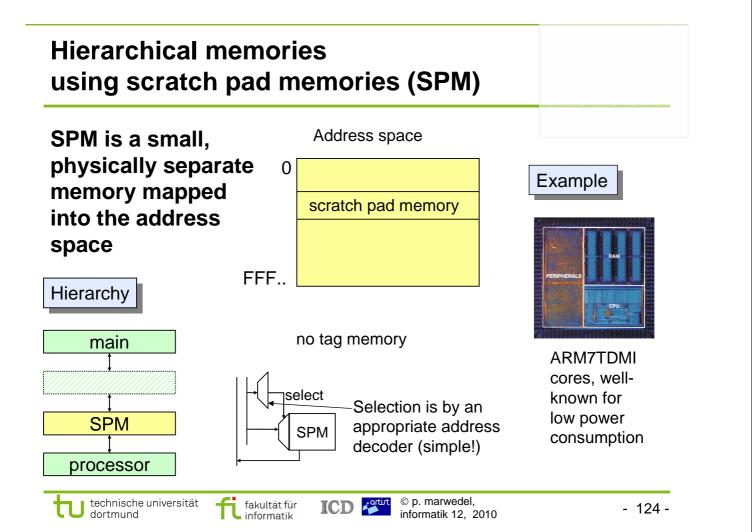

#### Why not just use a cache ?

Energy for parallel access of sets, in comparators, muxes.

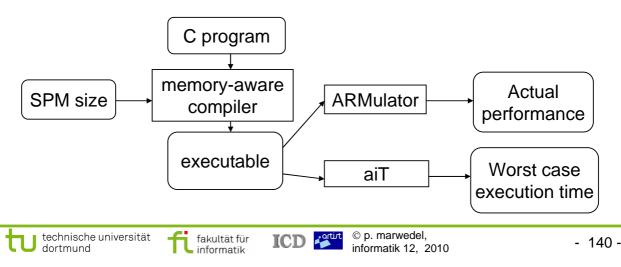

## Very limited support in ARMcc-based tool flows

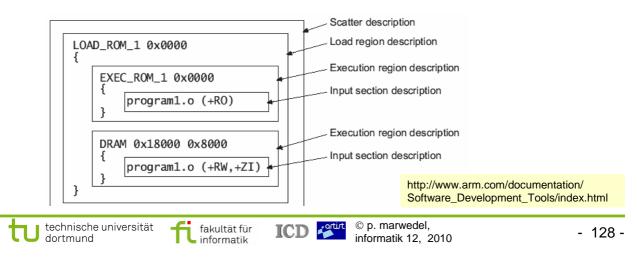

## 1. Use pragma in C-source to allocate to specific section: For example: #pragma arm section rwdata = "foo", rodata = "bar" int x2 = 5; // in foo (data part of region) int const z2[3] = {1,2,3}; // in bar

2. Input scatter loading file to linker for allocating section to specific address range

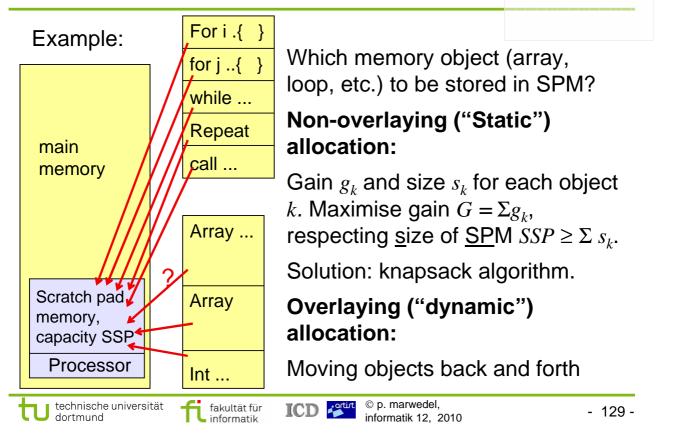

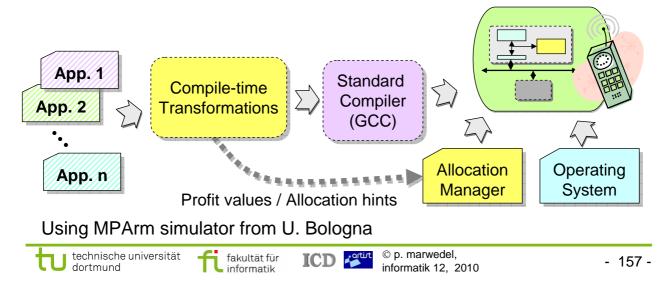

## Migration of data & instructions, global optimization model (TU Dortmund)

## IP representation - migrating functions and variables-

#### Symbols:

$S(var_k) = size of variable k$   $n(var_k) = number of accesses to variable k$   $e(var_k) = energy saved per variable access, if <math>var_k$  is migrated  $E(var_k) = energy saved if variable var_k is migrated (= <math>e(var_k) n(var_k)$ )  $x(var_k) = decision variable, =1 if variable k is migrated to SPM,$  =0 otherwiseK = set of variables; Similar for functions I

#### Integer programming formulation:

Maximize  $\sum_{k \in K} x(var_k) E(var_k) + \sum_{i \in I} x(F_i) E(F_i)$

Subject to the constraint

$\sum_{k \in K} S(var_k) x(var_k) + \sum_{i \in I} S(F_i) x(F_i) \le SSP$

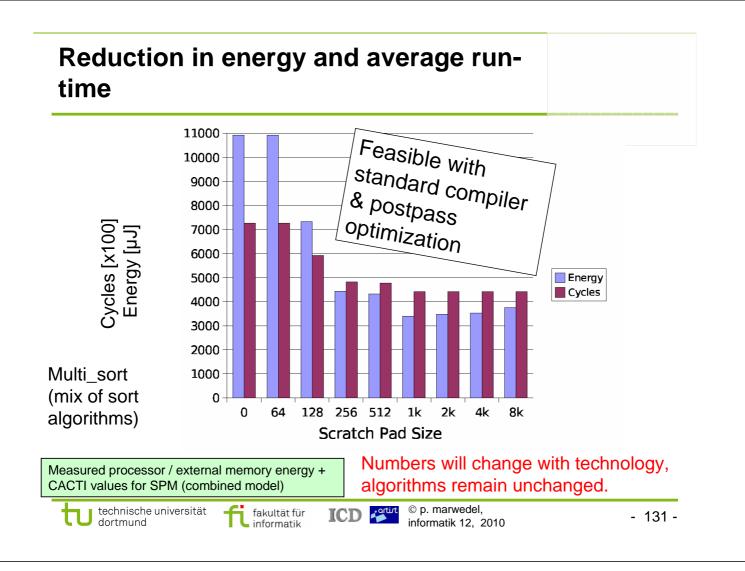

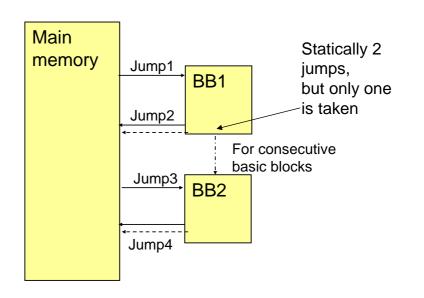

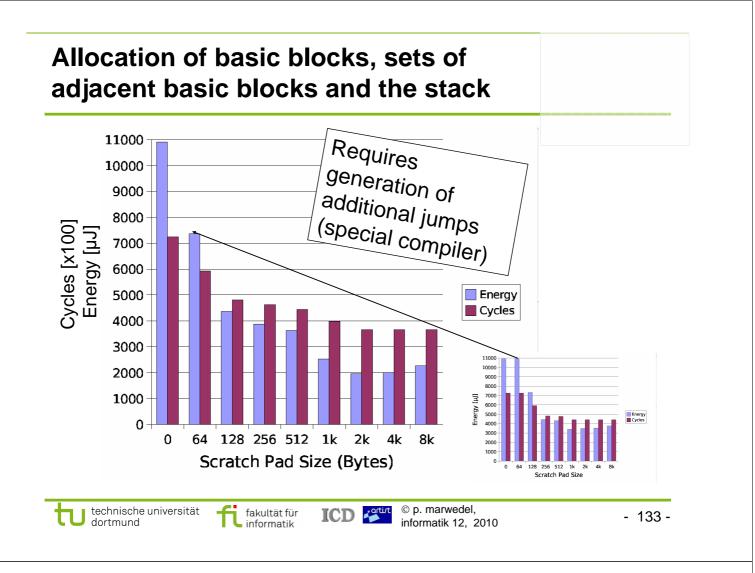

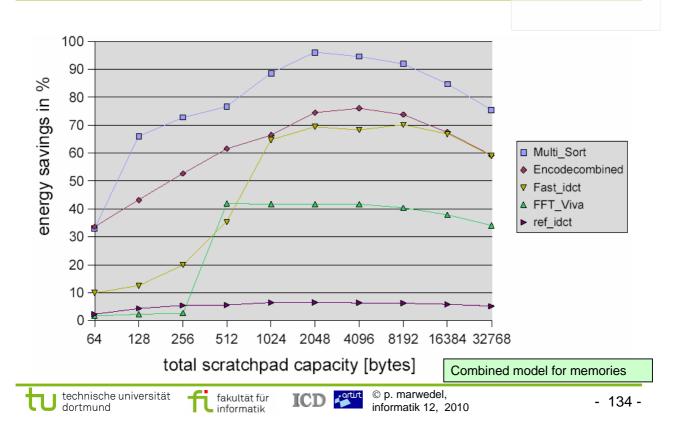

#### Allocation of basic blocks

Fine-grained granularity smoothens dependency on the size of the scratch pad.

Requires additional jump instructions to return to "main" memory.

ICD

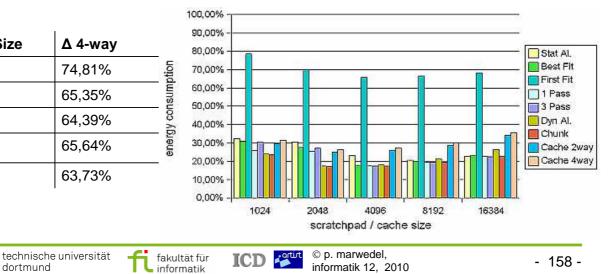

## Savings for memory system energy alone

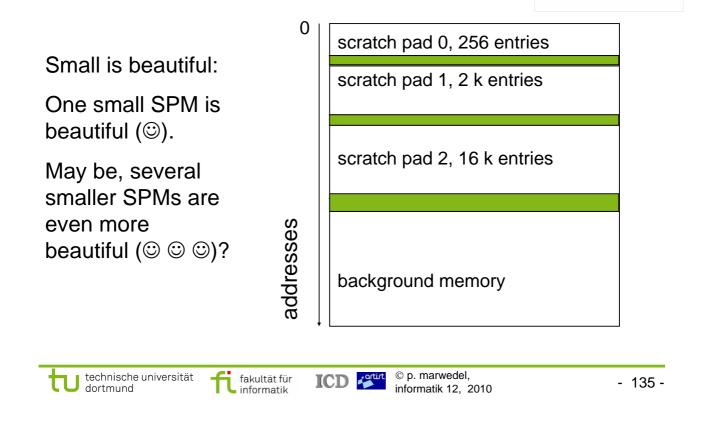

#### Multiple scratch pads

#### **Optimization for multiple scratch pads**

Minimize

$$C = \sum_{j} e_{j} \cdot \sum_{i} x_{j,i} \cdot n_{i}$$

With  $e_j$ : energy per access to memory j, and  $x_{j,i}$ = 1 if object i is mapped to memory j, =0 otherwise, and  $n_i$ : number of accesses to memory object i, subject to the constraints:

$$\forall j : \sum_{i} x_{j,i} \cdot S_i \leq SSP_j$$

$$\forall i : \sum_{i} x_{j,i} = 1$$

With  $S_i$ : size of memory object *i*,  $SSP_j$ : size of memory *j*.

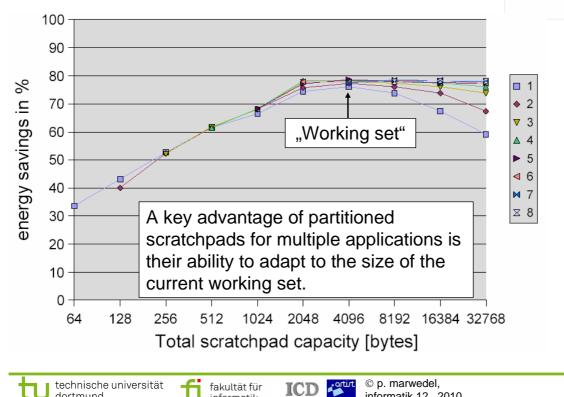

#### **Considered partitions**

Example of considered memory partitions for a total capacity of 4096 bytes

| 4k<br>0 | 2k<br>1 | 1k         | 512                                                                                   | 256                                                                                                                 | 128                                                                                                                                               | 64                                                                                                                                                                              |

|---------|---------|------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | 1       |            | 1                                                                                     |                                                                                                                     | 120                                                                                                                                               | 04                                                                                                                                                                              |

|         | -       | 1          | 1                                                                                     | 1                                                                                                                   | 1                                                                                                                                                 | 2                                                                                                                                                                               |

| 0       | 1       | 1          | 1                                                                                     | 1                                                                                                                   | 2                                                                                                                                                 | 0                                                                                                                                                                               |