Year 3 (Jan-Dec 2010) D3-1.0-Y3

IST-214373 ArtistDesign Network of Excellence on Design for Embedded Systems

Workpackage Report for Year 3

## Jointly-executed Programme of Integrating Activities (JPIA) Report

With input from all clusters.

Workpackage Leader:

Bruno Bouyssounouse (UJF/VERIMAG) <a href="http://www-verimag.imag.fr/~bouyssou/">http://www-verimag.imag.fr/~bouyssou/</a>

Policy Objective (abstract)

Each ArtistDesign research activity has work within both the JPIA and the JPRA workpackages. The JPIA activities are carried out on a global, NoE level, transcending the clusters. They form the supporting background for integration of the NoE, and are executed in phase and in interplay with the JPRA research activities. For instance, funds for staff mobility will be allocated taking into account the needs for research.

The activities listed here will promote integration of geographically dispersed teams. All these activities will have long-lasting effects, well beyond the duration of the initial EC funding.

These activities include Joint Technical Meetings, Staff Mobility and Exchanges, Tools and Platforms.

## Versions

| number | comment                                  | date                          |

|--------|------------------------------------------|-------------------------------|

| 1.0    | First version delivered to the reviewers | February 4 <sup>th</sup> 2010 |

## **Table of Contents**

| 1. Ov | 1. Overview of the Workpackage                                                               |    |  |  |  |

|-------|----------------------------------------------------------------------------------------------|----|--|--|--|

| 1.1   | ArtistDesign Participants and Affiliated Partners                                            | 5  |  |  |  |

| 1.2   | Starting Date, and Expected Ending Date                                                      | 5  |  |  |  |

| 1.3   | Policy Objective                                                                             | 5  |  |  |  |

|       |                                                                                              |    |  |  |  |

| 2. Jo | int Technical Meetings                                                                       |    |  |  |  |

| 2.1   | SW Synthesis, Code Generation and Timing Analysis cluster                                    | 6  |  |  |  |

| 2.2   | Operating Systems and Networks cluster                                                       | 11 |  |  |  |

| 2.3   | Hardware Platforms and MPSoC Design cluster                                                  |    |  |  |  |

| 2.4   | Design for Adaptivity Transversal Activity                                                   |    |  |  |  |

| 2.5   | Design for Predictability Transversal Activity                                               | 15 |  |  |  |

| 2.6   | Integration Driven by Industrial Applications Transversal Activity                           | 16 |  |  |  |

|       |                                                                                              |    |  |  |  |

| 3. St | aff Mobility and Exchanges                                                                   |    |  |  |  |

| 3.1   | SW Synthesis, Code Generation and Timing Analysis cluster                                    | 28 |  |  |  |

| 3.2   | Operating Systems and Networks cluster                                                       | 30 |  |  |  |

| 3.3   | Hardware Platforms and MPSoC Design cluster                                                  | 33 |  |  |  |

| 3.4   | Design for Adaptivity Transversal Activity                                                   | 34 |  |  |  |

| 3.5   | Design for Predictability Transversal Activity                                               | 35 |  |  |  |

| 3.6   | Integration Driven by Industrial Applications Transversal Activity                           | 35 |  |  |  |

|       |                                                                                              |    |  |  |  |

| 4. To | ols and Platforms                                                                            | 36 |  |  |  |

| 4.1   | SW Synthesis, Code Generation and Timing Analysis cluster                                    | 36 |  |  |  |

| 4.1   | 1.1 Tool or Platform: WCC                                                                    | 36 |  |  |  |

| 4.1   | 1.2 MAPS                                                                                     | 37 |  |  |  |

| 4.1   | 1.3 CoSy                                                                                     | 39 |  |  |  |

| 4     | 1.4 ICD-C                                                                                    |    |  |  |  |

|       | 1.5 MPMH – an integration of MPA parallelization assistant and MH static memory allocation t |    |  |  |  |

|       | PSoC                                                                                         |    |  |  |  |

| 4.1   | 1.6 aiT                                                                                      | 41 |  |  |  |

| 4.1   | 1.7 Bound-T                                                                                  | 42 |  |  |  |

| 4.1   | 1.8 SWEET                                                                                    | 43 |  |  |  |

| 4.1   | 1.9 LooPo                                                                                    | 44 |  |  |  |

| 4.1   | 1.10 R <sup>2</sup> G                                                                        | 44 |  |  |  |

| 4.1.11                  | MNEMEE Tool Flow                                                                                    | 45    |

|-------------------------|-----------------------------------------------------------------------------------------------------|-------|

|                         | perating Systems and Networks cluster                                                               |       |

| 4.2.1                   | iLAND middleware                                                                                    |       |

| 4.2.2                   | FTT-SE network manager                                                                              | 48    |

| 4.2.3                   | OpenZB – ZigBee for Wireless Sensor Networks                                                        |       |

| 4.2.4                   | Architecture Simulator                                                                              |       |

| 4.2.5                   | Partitioning Tool for Multicore Platforms                                                           | 51    |

| 4.2.6                   | MaRTE OS                                                                                            | 51    |

| 4.3 Ha                  | ardware Platforms and MPSoC Design cluster                                                          | 53    |

| 4.3.1                   | Tool: SymTA/S                                                                                       | 53    |

| 4.3.2                   | Tool: Analysis and optimisation framework for fault tolerant distributed embedded sy 54             | stems |

| 4.3.3<br>allocat        | Tool: MPMH – an integration of MPA parallelization assistant and MH static memory<br>tion for MPSoC |       |

| 4.3.4                   | Tool: MoVES - Modelling and Verification of Embedded Systems                                        | 57    |

| 4.3.5                   | Tool: MPA (Modular Performance Analysis)                                                            | 58    |

| 4.3.6                   | Tool: DOL (Distributed Operation Layer)                                                             | 59    |

| 4.3.7                   | Platform: Multicore Network on Chip Platform (McNoC)                                                | 60    |

| 4.3.8                   | Tool: Formal System Design (ForSyDe)                                                                | 62    |

| 4.4 De                  | esign for Adaptivity Transversal Activity                                                           | 63    |

| 4.4.1                   | SWEET (SWEdish Execution Time tool)                                                                 | 63    |

| 4.4.2                   | Hardware setup to demonstrate self-protection and adaptability of embedded Real-Ti                  |       |

|                         | ns                                                                                                  |       |

| 4.4.3                   |                                                                                                     |       |

| 4.4.4                   | Other Tools and Platforms                                                                           |       |

|                         | esign for Predictability Transversal Activity<br>Tool or Platform: aiT                              |       |

| 4.5.1                   | Tool or Platform: WCC                                                                               |       |

| 4.5.2<br>4.5.3          | Tool or Platform : MAST                                                                             |       |

|                         |                                                                                                     |       |

| 4.5.4                   | Tool or Platform : MPA (Modular Performance Analysis)                                               |       |

| <i>4.5.5</i><br>4.6 Int | Tool or Platform : MPARM<br>egration Driven by Industrial Applications Transversal Activity         |       |

| 4.6.1                   | Tool or Platform: SymTA/S                                                                           |       |

| 4.6.2                   | COSI                                                                                                |       |

| 4.6.3                   | Metropolis and Metro II                                                                             |       |

| 7.0.0                   |                                                                                                     |       |

| 5. Asses                | sment of the Workpackage at the end of Y3                                                           | 77    |

## 1. Overview of the Workpackage

## 1.1 ArtistDesign Participants and Affiliated Partners

Each ArtistDesign research activity contributes to achieving both research and integration goals. Thus, each has work within both the JPIA and the JPRA workpackages, and all partners and affiliated partners participate in the Joint Programme of Integration Activities.

## 1.2 Starting Date, and Expected Ending Date

These activities are intimately related to the JPRA (Joint Programme of Research Activities) and run for the entire duration of the NoE.

## 1.3 Policy Objective

The JPIA activities are carried out on a global, NoE level, transcending the clusters. They form the supporting background for integration of the NoE, and are executed in phase and in interplay with the JPRA research activities. For instance, funds for staff mobility will be allocated taking into account the needs for research.

The activities listed here will promote integration of geographically dispersed teams. All these activities will have long-lasting effects, well beyond the duration of the initial EC funding.

These activities include Joint Technical Meetings, Staff Mobility and Exchanges, Tools and Platforms.

#### -- Changes wrt Y2 deliverable --

No changes to the above text with respect to Year 2.

## 2. Joint Technical Meetings

Joint Technical meetings aim to present, discuss and integrate the ongoing work, and exchange points of view with other teams. They also serve to identify future work directions.

They are often organized around the annual General Assembly and Review, or around some of the main conferences in the area (most of which are piloted by a majority of ArtistDesign partners).

Depending on the context and in particular on the maturity of the topics under discussion, these Joint Technical Meetings may be open to the public, or by invitation (which implicitly includes all interested ArtistDesign partners).

This is all new text: this entire chapter pertains only to activity in Year 3.

#### 2.1 SW Synthesis, Code Generation and Timing Analysis cluster

#### **Course: Retargetable Compilation**

Lugano, Switzerland, Feb. 16-19 & Feb 23-25, 2010

Objectives: Spreading excellence in memory-architecture aware compilation and processor retargetability beyond ArtistDesign partners.

Presenters: Peter Marwedel (TU Dortmund), Rainer Leupers (RWTH Aachen) Other participants: about 20 students

Conclusion: The new, extended format turned out to be very useful.

http://www.alari.ch

#### ICT 4 Energy Efficiency

#### Brussels, Belgium – Feb. 23<sup>rd</sup>, 2010

IMEC representatives and P. Marwedel participated at a forum on energy efficiency organized by the Commission of the European Communities. The goal was to provide a contribution in the area of energy efficiency for embedded systems.

#### Cebit

#### Hannover, Germany – March 9<sup>th</sup>, 2010

P. Marwedel participated at a panel at the Cebit fair. The purpose was to contribute an embedded systems view on energy efficiency issues of ICT.

#### Meeting: Brief meeting at DATE

#### DATE 2010, Dresden – March 11th, 2010-12-10

Participants of the cluster, including members from RWTH Aachen, TU Berlin, TU Dortmund, and IMEC meet at DATE on March 11<sup>th</sup>. They discussed the state of cooperation, in particular preparations for the MAP2MPSoC flagship workshop at Rheinfels castle in June.

#### Special Session: Rainer Leupers (organizer), Cool MPSoC Design

DATE 2010, Dresden – March 11<sup>th</sup>, 2010

Wireless multimedia terminals are among the key drivers for MPSoC platform evolution. Heterogeneous multi-processor architectures achieve high performance and can lead to a significant reduction in energy consumption for this class of applications. However, just

designing energy efficient hardware is not enough. Programming models and tools for efficient MPSoC programming are equally important to ensure optimum platform utilization. Unfortunately, this discipline is still in its infancy, which endangers the return on investment for MPSoC architecture designs. On one hand there is a need of maintaining and gradually porting a large amount of legacy code to MPSoCs. On the other hand, special C language extensions for parallel programming as well as adapted process network programming models provide a great opportunity to completely rethink the traditional sequential programming paradigm for sake of higher efficiency and productivity. MPSoC programming is more than just code parallelisation, though. Besides energy efficiency, limited and specialized processing resources, and real-time constraints also growing software complexity and mapping of simultaneous applications need to be taken into account. The purpose of this session was to analyze the programming methodology requirements for heterogeneous MPSoC platforms and to outline new approaches. With emphasis on wireless applications, this special session has provided a blend of academia/industry presentations, including contributions from innovative startup companies in that domain. This way, it has aimed at consolidation of real life requirements and novel solutions, and stressed the need for intensified and cooperative research activities in MPSoC programming.

http://www.date-conference.com/

#### Poster session at DATE 2010

#### Dresden, Germany – March 12<sup>th</sup>, 2010

The presentation during the Friday poster session at DATE was focused on the automatic parallelization step developed in the MNEMEE project. Furthermore, the embedding of this technique into the integrated tool flow has been presented to the audience.

#### Winter school course: Rainer Leupers, Cool MPSoC Design

#### ASCI Winter School 2010, Soesterberg, The Netherlands – Mar 16-18, 2010

Wireless multimedia terminals are among the key drivers for MPSoC platform evolution. The problems of programming MPSoCs (as already described for the session at DATE above), were also discussed at a special session at the ASCI winter school. R. Leupers gave a lecture on Cool MPSoC Design at the ASCI winter school on embedded system. RWTH Aachen has analyzed the programming methodology requirements for heterogeneous MPSoC platforms and R. Leupers has outlined the approaches taken in MAPS compiler project at RWTH Aachen.

http://www.asci.tudelft.nl/pages/events.php?event\_id=1

#### **Industrial Workshop**

Stockholm, Sweden – April 12th, 2010

L. Thiele, P. Marwedel, AbsInt and other members of the PREDATOR project organized an industrial workshop during the Cyber-physical systems week.

## Joint demo at ACE/Compaan Booth at DAC 2010 (Anaheim), "Mapping Streaming Applications onto OMAP"

#### Anaheim, US - June 13-18, 2010

RWTH Aachen (Germany) and Compaan/ACE (Netherlands) have worked together to couple Compaan's technology (HotSpot Parallelizer) which transforms sequential C code into parallel process networks with the MAPS compiler towards real-life heterogeneous MPSoC backends. A joint demo has been established in this year's DAC (June 2010) to exhibit mapping multiple streaming applications to a commercial multi-processor SoC, the Texas Instruments OMAP 3530. The MAPS (MPSoC Application Programming Studio) project is a research effort to tackle the challenge of programming heterogeneous MPSoCs, ranging over multi-application

modelling, efficient scheduling/mapping and code generation. This joint work enables a complete mapping and compilation flow of streaming Kahn Process Networks (KPN) applications for the OMAP architecture. The demo showed practical scenarios such as quick mapping exploration, parallelizing sequential part and dynamic mapping, using both tools and was well received in the DAC exhibition.

http://www.dac.com

#### Tutorial: SystemC for Holistic System Design

Anaheim, CA – June 18<sup>th</sup>, 2010

At this year Design Automation Conference (DAC), Jürgen Teich organized a Friday tutorial covering the topic "SystemC for Holistic System Design with Digital Hardware, Analog Hardware, and Software".

#### Workshop: Software & Compilers for Embedded Systems (SCOPES) 2010

*St. Goar, Germany – June 28-29, 2010*

Objectives for the meeting: SCOPES focuses on the software generation process for embedded systems.

Organizer: Heiko Falk (TU Dortmund)

Conclusions: There were many discussions between cluster members at SCOPES (starting already on the eve before the sessions), at DATE, making the entire week the key joint event in spring.

http://www.scopesconf.org/scopes-10

## Keynote: Rainer Leupers, System Level MPSoC Design: A Bright Future for Compiler Technology?

SCOPES 2010, St. Goar, Germany – June 29<sup>th</sup>, 2010-12-02

R. Leupers delivered a keynote speech regarding system level MPSoC design in the SCOPES 2010. Looking back at the SCOPES history, compiler research for embedded processors started out in the 1990s with two major ambitions: (1) more architecture aware code optimizations to better support specialized target machines such as DSPs, and (2) higher flexibility to enable compiler retargeting over a wide range of machines. These research efforts have led to numerous results, many of which are part of industrial products today. So, what is left to do in embedded compilers and who -in a world with "free" tools like GCC and LLVM- will pay for them? Naturally, the evolution of embedded processor architectures demands for a never-ending stream of code optimization innovations. However, he argued that the current trend towards ESL design of embedded MPSoC platforms opens up the most promising new opportunities for compiler research, going far beyond the obvious problem of sequential code partitioning. Increasingly complex software stacks, consolidation of the MPSoC platform market, and higher design abstraction levels induce many interesting novel compiler technology use cases, some of which have been highlighted in the keynote.

http://www.scopesconf.org/scopes-10

#### Meeting: 3<sup>rd</sup> Workshop on Mapping Applications to MPSoCs, 2010

*St. Goar, Germany – June 29-30, 2010*

Objectives for the meeting: This is the flagship workshop of this cluster. The goal of this workshop is to establish links between leading researchers in the area and to stimulate advanced research.

Organizer: Peter Marwedel (TU Dortmund) Other participants: About 50

Conclusions: We are reaching out far beyond the ArtistDesign network. The workshop is now a key forum for discussions in this area. Attendees expressed their strong interest to continue this series of informal workshops as a platform for discussions.

http://www.artist-embedded.org/artist/-map2mpsoc-2010-.html

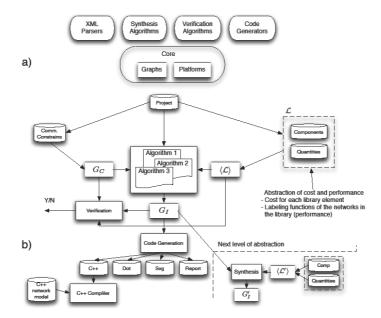

#### Tutorial: Rheinfels MNEMEE tutorial

St. Goar, Germany – June 30<sup>th</sup>, 2010

The MNEMEE tool flow was demonstrated for the second time in a MNEMEE workshop collocated with 3rd Workshop on Mapping of Applications to MPSoCs and the SCOPES Workshop. The placement of these workshops facilitated the attendance of the industrial and academic workshop participants. Besides an introductional part where an overview of the whole tool flow has been presented, interactive presentations of the MNEMEE tools have been shown by each partner.

#### Workshop: 10<sup>th</sup> International Workshop on Worst-Case Execution Time Analysis, 2010

Brussels, Belgium – July 6<sup>th</sup>, 2010, in connection with ECRTS 2010

Objectives for the meeting: To present and discuss recent work in WCET analysis of all kinds of systems by static or dynamic methods.

Organizer: Björn Lisper (Mälardalen)

Other participants: About 35

Conclusions: this year, the workshop had several contributions concerning WCET analysis for multicore systems, and the use of model checking techniques for timing analysis, in addition to the more traditional timing analysis topics. An invited talk by Dr. Jean Souyris from Airbus gave an industrial perspective on timng analysis of safety-critical software.

http://www.artist-embedded.org/artist/-WCET-2010-.html

#### Tutorial: Model-Based Embedded Systems Design

Rabat, Morocco – July 12<sup>th</sup>, 2010

P. Marwedel presented a full-day tutorial on model-based design of embedded systems at the first African ArtistDesign Summer School.

http://www.artist-embedded.org/artist/Overview,1958.html

#### Tutorial: Invasive Computing - Basic Concepts and Foreseen Benefits

*Autrans, France, September* 7<sup>th</sup>, 2010

Jürgen Teich presented a novel paradigm for organizing the computations of large scale MPSoCs of the future at the ARTIST Summer School Europe 2010. The main idea of Invasive Computing relies on the vision that applications will organize themselves and spread their computational load at run-time on processors, communication and memory resources in phases called invasion, and, depending on available degree of parallelism, dynamically changing user objectives or in dependence of the state of the underlying hardware such as temperature profile, load, permissions, or faultiness, again retreat from these.

http://www.artist-embedded.org/artist/Overview,2064.html

#### Workshop: IFIP Workshop on Software Technologies for Future Embedded and Ubiquitous Systems (SEUS 2010)

Waidhofen/Ybbs, Austria - Oct. 13-15, 2010

Objectives for the meeting: SEUS is a forum for practitioners and researchers to discuss experiences and ideas relating to the development of embedded and ubiquitous systems. Organizer: Peter Puschner (TU Vienna)

Conclusions: There were some interesting contributions and discussions on the role of time in the design and construction of embedded applications, which underlined the importance of the architectural support for building time-predictable embedded systems.

http://pan.vmars.tuwien.ac.at/seus2010/index.html

#### **Tutorial: Scottsdale MNEMEE tutorial**

Scottsdale, US – October 24<sup>th</sup>, 2010

Members of the teams from Dortmund, TU Eindhoven and IMEC presented results of the MNEMEE workshop at ESWEEK. A tool flow for memory optimizations was demonstrated as a Sunday-Tutorial related to this series of Conferences. The format of a half-a-day tutorial provided in-depth presentations of the tools and techniques developed in MNEMEE.

## Workshop: 6<sup>th</sup> Workshop on Embedded Systems Education, 2010

#### Scottsdale, US, – October 28<sup>th</sup>. 2010

Objectives for the meeting: Embedded system education is still a very young area and frequently restricted to teaching the details of microcontroller programming. A long-term objective of this workshop is to improve the visibility of work in the area and to stimulate the introduction of broader curricula.

Organizer: Peter Marwedel (TU Dortmund)

Other participants: About 30

Conclusions: Visibility was improved by the inclusion of the proceedings in the ACM digital library. Presenters included top researchers from the US and Asia. Attendees were extremely satisfied with the quality of the presentations.

http://www.artist-embedded.org/artist/-WESE-10-.html

#### Workshop: 2<sup>nd</sup> Workshop on Software Synthesis, 2010

#### Scottsdale, US, – October 29<sup>th</sup>, 2010

Objectives for the meeting: An increasing amount of software is not written manually any more. Rather, software is synthesized from abstract models of the required functionality. Software synthesis has been implemented in various disperse communities. The workshop aimed at bringing these communities together.

Organizer: Peter Marwedel (TU Dortmund); Alberto Sangiovanni-Vincentelli

Other participants: About 10

Conclusions: Presenters at this workshop presented industrial as well as academic results. Attendees agreed on the necessity of more work in this area.

http://www.artist-embedded.org/artist/-WSS-10-.html

#### 2.2 Operating Systems and Networks cluster

#### Meeting: Cache-aware scheduling and timing analysis

City, Country: Pisa, Italy

Date: February 22-23, 2010

<u>Objectives for the meeting</u>: Understand how schedulability analysis and timing analysis tools can be integrated to properly select preemption points in the task code to reduce cache related overhead, stack usage and power consumption.

Organizer: Giorgio Buttazzo (Scuola Superiore Sant'Anna, Pisa)

<u>Other participants</u>: Marko Bertogna (Pisa), Francesco Esposito (Pisa), Mauro Marinoni (Pisa), Christoph Cullmann (Absint), Martin Kaiser (Absint), Sebastian Altmeyer (USAAR), Claire Burguiere (USAAR), Jian-Jia Chen (ETHZ), Andreas Schranzhofer (ETHZ), Martino Ruggiero (University of Bologna), Paolo Burgio (University of Bologna).

<u>Conclusions</u>: A set of experiments were planned using the Erika kernel on the MPARM simulator to evaluate the effects of non-preemptive scheduling on cache behavior, stack usage and power consumption. A number of suggestions were identified to improve timing analysis to provide data cache and support and stack information for ARM7.

#### Meeting: Developing real-time applications on multicore reservations

City, Country: Pisa, Italy

Date: June 3-4, 2010

<u>Objectives for the meeting</u>: Understand how to implement a parallel applications on a multicore platform abstracted on a set of virtual processors, using data flow languages.

Organizer: Giorgio Buttazzo (Scuola Superiore Sant'Anna, Pisa), Karl-Erik Årzén (Lund)

Other participants: Johan Eker, (Ericsson), Carl Von Platen (Ericsson), Charles Chen Xu (Ericsson), Enrico Bini (Pisa), Gerhard Fohler (TUKL), Stefan Schorr (TUKL), Vanessa Romero Segovia (ULUND), Anders Nilsson (ULUND), Christophe Lucarz (EPFL), Marco Mattavelli (EPFL), Ghislain Roquier (EPFL), Claudio Scordino (Evidence), Paolo Gai (Evidence).

<u>Conclusions</u>: A set of guidelines to be use in the development of real-time parallel applications.

#### Meeting: Resource management in multi-core systems

City, Country: Brussels, Belgium

Date: January 11th, 2010

<u>Objectives for the meeting</u>: To discuss multi-resource scheduling and how to integrate different research efforts.

Organizer: Alan Burns (University of York)

<u>Other participants</u>: Giorgio Buttazzo (Pisa), Giuseppe Lipari (Pisa), Eduardo Tovar (Porto), Luis Almeida (Porto) Lucia Lo Bello (Catania), Pau Marti (Catalonia), Marisol Garcia Valls (UC3-Madrid), Tullio Vardanega (University of Padova), Alejandro Alonso (UP Madrid), Gerhard Fohler (TUKL), Stefan Schorr (TUKL).

<u>Conclusions</u>: It was agreed that the wiki was a useful way of organizing collaboration and the exchange of research results as they apply to more complex platforms with multi-cores, buses, NoC and heterogenuois processors may all be presents, and where energy usage may also be an issue. Members agreed to add to the wiki over the coming year.

Year 3 (Jan-Dec 2010) D3-1.0-Y3

#### Meeting: Hierarchical scheduling in control

City, Country: Kaiserslautern, Germany

Date: March 3-5, 2010

<u>Objectives for the meeting</u>: To discuss hierarchical scheduling and contract based virtualization.

Organizer: Gerhard Fohler (TUKL).

<u>Other participants</u>: Giuseppe Lipari (Pisa), Alan Burns (University of York), Michael Gonzalez Harbour (University of Cantabria), Stefan Schorr (TUKL).

<u>Conclusions</u>: An approach was developed that would allow the approaches developed for single processor systems to be adapted and extended for multiprocessor and multicore platforms. Future research questions were identified to be worked on throughout the year. Results were discussed at a further meeting in December 2010.

#### Meeting: Hierarchical scheduling and contract based virtualization

City, Country: San Diego, USA

Date: December 1, 2010

<u>Objectives for the meeting</u>: To discuss hierarchical scheduling and contract based virtualization.

Organizer: Giuseppe Lipari (Pisa).

<u>Other participants</u>: Alan Burns (University of York), Stefan Schorr (TUKL), Gerhard Fohler (TUKL).

<u>Conclusions</u>: An approach was consolidated and a process for exploiting the scheme both academically and industrially was identified. Discussions will continue.

## 2.3 Hardware Platforms and MPSoC Design cluster

#### **Meeting: Predictability Measures**

Zurich, Switzerland – 30.9.2010

Objectives: Define measures for predictability and efficiency in computer architectures. Organizer: ETH Zurich

Other participants: University Saarland

Conclusions: We have been comparing and developing several measures that allow to estimate the degree of predicvtability of complex systems in a compositional manner. There is no final conclusion yet as there are still technical problems to overcome.

## Meeting: Shared Resources in Multiprocessor Systems - Modeling Concepts and Observations Brussels, Belgium – July 5, 2010

Objectives for the meeting: TU Braunschweig and ETH Zürich are working on similar analysis approaches for multiprocessor systems with shared resources. The main objective of this meeting was a mutual update on the research activities related to multiprocessor systems with shared resources.

Organizer: Simon Schliecker and Mircea Negrean (TUBS), and Andreas Schranzhofer (ETHZ) Other participants: -

Conclusions: Open issues and possible improvements on the modelling and analysis approaches of multi-core systems with shared resources were identified. Results have been presented jointly by TU Braunschweig and ETHZ at the annual ArtistDesign Cluster Meeting in Leuven, Belgium. During that meeting, further ideas regarding approaches addressing shared resources in multiprocessor systems have been exchanged with partners of this activity, e.g. Linköping University.

#### Meeting : MPSoC Cluster Meeting

Dresden, Germany – March 2010 Objectives for the meeting: Status, plans and discussions for the cluster. The meeting was collocated with DATE 2010 Organizer: Petru Eles (LiU) Other participants: Most members of the cluster Conclusions : Progress according to plans.

#### Meeting : ARTIST HW Platform and MPSoC Technical Meeting

IMEC, Leuven, Belgium – July 6-7, 2010

Objectives for the meeting: The whole cluster meets once a year to share results and directions. Besides a keynote on biomedical research at IMEC, there were 11 technical presentations covering the two activities of the cluster: Design, and Analysis. Organizer: Maja D'Hondt (IMEC)

Other participants: Karim Benchehida (CEA), Jan Madsen (DTU), Elena Maftei (DTU), Lothar Thiele (ETHZ), Andreas Schranzhofer (ETHZ), Iuliana Bacivarov (ETHZ), Maja D'Hondt (IMEC), Rudy Lauwereins (IMEC), Roel Wuyts (IMEC), Martin Palkovic (IMEC), Satya Munaga (IMEC), Rogier Baert (IMEC), Carolina Blanch (IMEC), Gert Vanmeerbeeck (IMEC), Francky Catthoor (IMEC), Robert Fasthuber (IMEC), Petru Eles (LU), Soheil Samii (LU), Simon Schliecker (TUB), Mircea Negrean (TUB), Andrea Bartolini (Unibo)

Conclusions : The cluster is very healthy with a lot of interesting research on both existing themes of the cluster, and on new directions. The collaboration with industry has increased, partly due to partners involved in Artemis projects. Progress following the plans set out in the cluster deliverable for year 2,

http://www.artist-embedded.org/artist/Agenda-Slides,2177.html

## 2.4 Design for Adaptivity Transversal Activity

**Meeting:** Retis Laboratory Pisa, 22.3. – 23.3.2010 Objectives for the meeting: Discuss the current progress in the joint research program on adaptivity and servers. Participants: ETHZ, SSSA Organizer: Giorgio Buttazzo, RETIS Laboratory

Meeting: Retis Laboratory Pisa, 17.12.2010. Objectives for the meeting: Discuss the current progress in the joint research program on adaptivity and servers. Discuss PhD thesis of Luca Santinelli (was exchange student at ETH Zurich) Participants: ETHZ, SSSA Organizer: Giorgio Buttazzo, RETIS Laboratory

## Workshop: First International Workshop on Adaptive Resource Management (WARM 2010), Cyber-Physical Systems Week 2010, April 12, 2010, Stockholm, Sweden

The focus of WARM was software-based approaches to adaptive resource management for soft or adaptive embedded real-time applications, e.g., multimedia applications or non-safety critical control applications. Special emphasis was given to multi-resource management and to multi-core platforms.

The programme included 8 submitted presentations, 3 invited presentations and one keynote on challenges and solutions for adaptive resource management in cyber-physical systems given by Prof Raj Rajkumar, CMU.

Organizers:

- Prof. Giorgio Buttazzo, Scuola Superiore Sant'Anna, Pisa

- Prof. Gerhard Fohler, TU Kaiserslautern

- Prof. Alan Burns, University of York

- Prof. Luis Almeida, University of Porto

- Prof. Karl-Erik Årzén, Lund University

- Prof. Michael Gonzalez Harbour, University of Cantabria

URL: http://www.artist-embedded.org/artist/Theme.html

In addition to the above several meetings involving the partners have been held within the projects, typically., FP7 STREP projects (COMBEST, ACTORS, PREDATOR, ...), where the actual collaborative work mostly is being performed.

## 2.5 Design for Predictability Transversal Activity

#### Meeting : Towards a Demonstrator

Karlsruhe, Germany - <2010-07-21>

Objectives for the meeting: PREDATOR-internal meeting. Definition of a demonstrator for the review meeting, which involves several PREDATOR partners and their expertise. Identify remaining challenges.Organizer: Jian-Jia Chen (KIT)

Other participants: Daniel Grund (USAAR), Simon Kramer (Bosch), Andreas Schranzhofer (ETHZ), Claire Maiza (USAAR) Conclusions : A demonstration is feasible with respect to Bosch's DemoCar platform. It will consist of ETHZ's WCRT analysis together with AbsInt/USAAR's parameter analyses. Other potential integration opportunities have been identified as well.

#### Meeting : Predictable Architectures

Zürich, Swizerland – 2010-09-30 to 2010-10-01

Objectives for the meeting: Resuming the discussion (USAAR/ETHZ) on the definition of predictability; Continuing the discussion with Bosch/ETHZ/AbsInt towards the demonstrator Organizer: Lothar Thiele (ETHZ), Andres Schranzhofer (ETHZ) Other participants: Jian-Jia Chen (KIT), Reinhard Wilhelm (USAAR), Daniel Grund (USAAR), Christoph Cullmann (AbsInt), Simon Kramer (Bosch), Luca Benini (UNIBO) [on phone] Conclusions:

- Predictability is difficult to define.

- PREDATOR Demonstrator is on the way. AbsInt delivered adapted version of aiT.

- Bosch will deriver (and by now did) the parameters, which ETHZ needs for their analysis.

Bosch's Hardware Model is difficult to analyze. Separation of communication and computations is beneficial

#### **Meeting: Predictability Measures**

*Zurich, Switzerland – 30.9.2010* Objectives: Define measures to determine predictability and efficiency in computer architectures. Organizer: ETH Zurich Other participants: University Saarland Conclusions: We have been comparing and developing several measures that allow to estimate the degree of predicvtability of complex systems in a compositional manner. There is no final conclusion yet as there are still technical problems to overcome.

## 2.6 Integration Driven by Industrial Applications Transversal Activity

#### Meeting: SafeTRANS Industrial Days

Frankfurt, Germany, May 5, 2010, and Stuttgart, Germany, November 23, 2010

Within the context of SafeTRANS (including ArtistDesign Members OFFIS and TU Braunschweig) two Industrial Days were organized in 2010. The workshops provide a platform for discussion and exchange of experiences in industry across application domains. Each workshop had about 45 participants.

The first one on "Interdependency between Safety and Security in Embedded Systems" was held in May in Frankfurt at DB Netz AG. Given presentations cover security and safety aspects in railway communication, protection against manipulation regarding plant integrity, IT risk analysis concerning safety and security in civil aviation, challenges concerning safety and security for car-2-X communication, and others.

The second workshop took place on November 23 at Mercedes Event Center in Sindelfingen, Germany. The title of that workshop was "Model-based Systems Engineering". Presentations given by industrial participants (Daimler, Volkswagen, EADS, Siemens, ESG, Esterel Technologies) cover topics like quality of software models, test systems, formal methods for model based specification of railways systems, experiences of MBSE in the development of airplane systems, seamless design process integrating system and software design.

http://www.safetrans-de.org/de\_8\_Industrial\_Day.php

http://www.safetrans-de.org/de 9 Industrial Day.php

#### Workshop: 3<sup>rd</sup> Annual ICES Conference Stockholm,

*Sweden, Sept.* 2<sup>*nd*</sup>, 2010

ICES 3rd Annual Conference was entitled *-Networked Products - a solution for the energy problems of the future!* 115 people from academia and industry gathered together for this 1-day conference at Norra Latin, Stockholm City Conference Centre, on Thursday 2nd September 2010.

A key role for ICES is that of nurturing an active network across the borders of academia and industry, with the aim of achieving synergy in education and research. ICES focuses on the thematic areas of embedded systems architecture, system and software verification and development methodology. These areas become more and more important as embedded systems become more advanced and interconnected throughout our whole society.

The theme for the 2010 ICES annual conference, "Networked Products, a solution for the energy problems of the future", is fully in line with this ambition. Although today's energy systems are already enabled by embedded systems, a structured approach to their integration would provide new opportunities, not only for greatly enhancing the efficiency of energy systems but also in providing innovative solutions in the search for sustainable energy provision. However, it emerged during discussions between ICES members that it is extremely rare for experts from the energy systems domain to actually meet with embedded systems experts! Thus this year's conference set out to achieve several goals, including:

- Establishing a meeting point between the "energy" and "embedded systems" communities;

- Identifying the key challenges posed by sustainable energy systems from an embedded systems perspective

- Communicating the huge potential of embedded systems to energy related stakeholders in a contextual and informative way, leading to new discussions, collaboration, and a mutual awareness of the opportunities and challenges ahead.

The program featured an exciting blend of prominent speakers, effectively representing multiple energy system domains such as buildings, cities, smart grids, transportation and legislation. The program also included presentations of research activities in Stockholm, with a specific focus on the area of energy and embedded systems.

A condensed summary of the topics that were raised by the speakers and in the concluding panel debate is provided on the web site including presentations http://www.kth.se/itm/centra/ices/previous-events/networked-products-conf-1.66443?l=en\_UK

## Meeting : Workshop: ICES Seminar: Formalisms for Description and Visualization of Embedded Systems Architectures

#### - Current State Of Practice, Needs And Research Topics

#### Stockholm, Sweden, April 12<sup>th</sup>, 2010

This ArtistDesign workshop was carried out as part of CPS Week at KTH, 12 April 2010, with approx. 50 participants from industry and academia.

A key fundamental challenge in developing embedded systems is that of managing their complexity while providing products of the desired quality, and at the right cost considering the whole life-cycle. As one important means to handle complexity, architecture description languages (ADL's) have emerged as a means to formally describe software and hardware architectures, providing a basis for analysis of system properties such as reliability and performance, and for synthesis (e.g. generating glue code). The dominating views provided by ADLs is that of describing the system structure, mainly with the notion of black box (SW/HW) components, following the lines of compositionality where the idea is that system properties can be derived from a configuration of components and their externally visible properties. This situation fits well for the purposes of a system integrator that specifies the system architecture and has to reason about system level properties without details of the internals of component implementations. It is clear that embedded systems expose many different types of structures. The term architecture is usually reserved for the fundamental organization of a system that determines essential non-functional properties. At the same time several graphical formalisms have been proposed with the purpose to visualize, communicate and document advanced embedded systems. Examples of early ADL's and formalisms include MetaH, Hatley-Pirbhai modeling, CoDARTS and ROOM.

Over the recent years, many development have taken place, including

- OMG development and standardization leading to UML, SysML and MARTE.

- The standardization of the AADL by SAE (based on MetaH).

- The development of Autosar and the EAST-ADL in the automotive industry.

- Further evolution and maturity of model-driven engineering, including domain-specific languages, environments, and model transformation techniques.

Obviously, each formalism is developed in a particular context, thereby emphasizing certain abstractions, relations and properties. One thrust shared by these efforts is to combine the support for visualization with that of formalized descriptions that are amenable to analysis and synthesis. Visualization, analysis and synthesis, are all key to the engineering of advanced embedded systems based products, with the goals to facilitate communication among people, early decision making and automation. However, while such formalisms have been

researched, and prototype tools been developed, there has been a slow, or only partial adoption in embedded systems industry, with varying degree of success.

The lack of adoption of such formalisms could be explained by the lack of mature tools and standards, and the "normal" gap from research to industrial take-up. It can also be noted that while behavior descriptions and design flows are quite mature for several embedded systems domains, structural descriptions a la ADLs have been lagging behind. The automotive AUTOSAR represents a new effort and departure from this state in providing a middleware standard and by pushing tool vendors to support AUTOSAR. All these efforts, in one way or another, represent efforts in the area of model and component based development. However, because of the multitude of research, standardization and industrial efforts, the current situation is, to say the least, a bit confusing.

The workshop therefore had the overall goal to bring representatives from several "architecture description language" communities together to discuss trends, issues for industrial adoption and what the key outstanding research issues are.

The workshop in addition provided a hands-on session with selected formalisms including AADL, EAST-ADL (a UML profile for embedded systems), SystemC/VHDL, and Domain specific ADL's (using a meta-modeling environment where different formalisms can be created).

http://www.artist-embedded.org/artist/Overview,1937.html

#### Meeting: Workshop on Green and Smart Embedded System Technology: Infrastructures, Methods and Tools at the Cyber-Physical System Week

Stockholm, Sweden, April 12<sup>th</sup>, 2010

#### Organizing committee, general chairs

Alberto Sangiovanni Vincentelli, Huascar Espinoza, Marco Di Natale, Roberto Passerone

#### Overview

Efficient production, transmission, distribution and use of energy are fundamental requirements for our modern society and the challenge of a green, low carbon economy. Embedded systems have an important role to play in increasing the energy efficiency and in reducing carbon emissions to sustainable growth. Indeed, most systems for monitoring and control of energy production, distribution and use are today interconnected and controlled by embedded devices, in areas such as industrial manufacturing, transportation systems, building automation, domestic appliances and more. This offers the opportunity for the creation of new integrated systems offering new products, processes and services with greater efficiency and better situation awareness to end-users and service and infrastructure owners.

Energy-efficient systems offer unique challenges to the embedded system community, from system-level design to dynamic and adaptive controls, optimization of architectures and communication, real-time and reliable services as well as reusable software components and systems.

Energy efficient solutions include both local and global smart solutions. Smart embedded solutions merge ubiquitous computing and the Internet of Things, i.e., the technology integration with sensors, actuators, micro-chips, micro- and nano-embedded systems that allow for collecting, filtering and producing more and more information locally, to be further consolidated and managed globally according to business functions and services. Locally, embedded systems provide information on energy consumption of every energy consuming appliance in a single location (e.g., home, building, vehicle) to be provided in real-time, in a user friendly way, thereby empowering citizens to take decisions that lead to energy savings. Globally, energy efficient solutions include smart grid concepts, which require dynamic controls

for balancing and organizing production from renewable and conventional sources, negotiating, purchasing and routing power requests, but also regulating, balancing and controlling the amount of electrical power that systems consume.

From the system-level design perspective, there is a need for simulation, modelling, analysis, and monitoring methods and tools to facilitate an integrated system approach. Today, energy efficient solutions are developed by independent companies whose products or components are tested for individual performance independently of each other. An integrated system approach to the design and implementation, where these components are integrated in a way that they reduce energy consumption through cooperation, is rarely used. This often leads to significant system-level inefficiencies. System design methods and tools, including model-based solutions, must consider the growth and evolvability of hardware and software platforms, to ease the conception, development, validation and integration of new devices and services. The challenge and opportunities not only lie in the integration issue, but also in providing methods and tools for innovative solutions that satisfy government regulations, customer expectations and meet environmental challenges.

#### **Objectives / Agenda**

GREEMBED 2010 aims at bringing together experts, researchers, and practitioners, from the embedded systems community, who are interested on research and development of embedded system infrastructures, methods, and tools for green and smart energy-efficient applications.

The topics of the proposed workshop are extremely important from an economic and social view and yet some of them still constitute emerging research areas, possibly without wellestablished or recognized results and require integration of knowledge and cross-fertilization from different domains. CPS Week is an excellent opportunity to bring together people from diverse embedded systems communities, such as controls, simulation and modeling, embedded computation and communication models and algorithms, software and hardware design, languages, sensor networks, real-time systems and several applications communities. Jointly, these communities can help create a critical mass of research, development and innovation in green embedded system technologies. An open exchange of ideas and experiences will benefit the global community, leading to new insights and stimulating further development.

Program: Morning session

#### 9:00-11:00 Session 1: ICT for Energy Efficiency in Buildings

INVITED SPEAKER: Juan Perez (Labein-Tecnalia, Spain), "REEB - The European Strategic Research Roadmap to ICT enabled Energy-Efficiency in Building and Construction"

INVITED SPEAKER: Anke Weidlich (SAP, Germany), "Enterprise Integration for Decentralized Energy Management"

INVITED SPEAKER: Jose-Javier De Las Heras (ACCIONA, Spain) "EDIANA -Embedded Systems for Energy Efficient Buildings"

#### 11:00-12:15 Session 2: User interfaces for Energy Awareness

INVITED SPEAKER: Régis Decorme (CSTB, France), "IntUBE - Intelligent Use of Buildings' Energy Information – Energy Challenge Concept"

INVITED SPEAKER: Carin Torstensson (Interactive Institute, Sweden), "BeAware– Boosting Energy Awareness, presentation of the pilot phase on 8 households"

INTERACTIVE SESSION - Short quiz on energy awareness + brainstorming session with the audience on "user interfaces for energy awareness: content and layout" (chaired by IntUBE and BeAware project partners)

#### **Program: Afternoon Session:**

#### 13:30-15:15 Session 3: Smart Buildings & Smart Grids

INVITED SPEAKER: Hakan Johansson (ABB, Sweden), "Smart Grid Activities at ABB"

"Energy Saving Information Platform: ENERsip", Boris Kantsepolsky (MOTOROLA, Israel) and Rafael Morillo (AMPLIA, Spain)

Scheduling energy consumption with local renewable micro-generation and dynamic electricity prices", Onur Derin & Alberto Ferrante (University of Lugano, Switzerland)

"DSM in Spain. Results from GAD Project: Aims, Developments and Ongoing Results", Laura Moreno (ITE, Spain), Susana Bañares (REE, Spain), Isabel Navalón (Iberdrola, Spain) and Alfredo Quijano (ITE, Spain)

#### 15:30-17:15 Session 4: System and Control Engineering for EE in Buildings

INVITED SPEAKER: Sylvain Robert (CEA, France), "The CLIMB project - Implementing the Building Information Model to Optimize Energy Efficiency" (Cancelled)

"Adopting system engineering methodology to Virtual Power System design flow", Slobodan Lukovic, Igor Kaitovic & Umberto Bondi (University of Lugano, Switzerland)

"Optimised Embedded Distributed Controller for Automated Lighting Systems", Alie El-Din Mady, Menouer Boubekeur & Gregory Provan (University College Cork, Ireland)

"Embedded Controllers for Increasing HVAC Energy Efficiency", Jiri Vass, Jana Trojanova, Radek Fisera & Jiri Rojicek (Honeywell, Czech Republic)

http://www.artist-embedded.org/artist/Overview,1928.html

#### Meeting: IWBDA: International Workshop on Bio-Design Automation at DAC

http://cctbio.ece.umn.edu/wiki/index.php/IWBDA:International\_Workshop\_on\_Bio\_Design\_Automation

#### **Objectives/Description**

The Second International Workshop on Bio-Design Automation (IWBDA) at DAC brought together researchers from the synthetic biology, systems biology, and design automation communities. The focus is on concepts, methodologies and software tools for the computational analysis of biological systems and the synthesis of novel biological systems.

Still in its early stages, the field of synthetic biology has been driven by experimental expertise; much of its success has been attributable to the skill of the researchers in specific domains of biology. There has been a concerted effort to assemble repositories of standardized components. However, creating and integrating synthetic components remains an ad hoc process. The field has now reached a stage where it calls for computer-aided design tools. The electronic design automation (EDA) community has unique expertise to contribute to this endeavour. This workshop offered a forum for cross-disciplinary discussion, with the aim of seeding collaboration between the research communities.

Topics of interest included:

- Design methodologies for synthetic biology;

- Standardization of biological components;

- Automated assembly techniques;

- Computer-aided modeling and abstraction techniques;

- Engineering methods inspired by biology.

This workshop obtained strong interest from industry as well as scientific organizations as shown below:

We had a good number of participants (about 90), 13 talks and 18 posters including a special session that was dedicated to the topic at the Design Automation Conference.

#### Agenda

Monday – June 14th

■ 9am - 10am, Rm. 303CD

Opening Remarks: Marc Riedel (General Chair), Ron Weiss (<u>http://weisswebserver.ee.princeton.edu/</u>)

*Keynote Address:* Roger Brent (<u>http://labs.fhcrc.org/brent/people.html</u>), Fred Hutchinson Cancer Research Center..

- 10:30 Noon Rm. 303CD

- Tutorial #1 on DNA Nanostructures, Shawn Douglas (<u>http://www.shawndouglas.com/</u>), Harvard.

■Tutorial #2 on CAD for Genetic Circuits, Jean Peccoud (<u>https://www.vbi.vt.edu/faculty/personal\_pages/jean\_peccoud</u>), Virginia Tech.

- Noon 2pm, Rm. 304A

- Lunch (Rm. 304A) and Posters Session 1 (outside of Rm. 303CD)

- 2:00pm 4:00pm, Rm. 303CD

- Tech. Talks Session 1 Tools for Bio-Design Automation

■ 1BDA.1 SynBioSS Designer: From DNA Sequences to Dynamic Phenotypes and Back Emma Weeding and Yiannis Kaznessis

■ 1BDA.2 TinkerCell: CAD Application with Support for Third-party Programs, Deepak Chandran and Herbert Sauro

■ 1BDA.3 Automatic Compilation from High-Level Languages to Genetic Regulatory Networks, Jacob Beal, Ting Lu and Ron Weiss

■ 1BDA.4 Designing Biological Devices in GEC, James Brown, Neil Dalchau, Michael Pedersen and Andrew Phillips

- 4:30pm 6:00pm, Rm. 303CD

- Tech. Talks Session 2 Modeling and Standards for Bio-Design

■ 2BDA.1 A Semantic Knowledge Base of Standard Biological Parts, Michal Galdzicki, Cesar Rodriguez, Deepak Chandran, John Gennari and Herbert Sauro

- 2BDA.2 Modeling and Predicting the Strength of Bacterial Promoters: A Test-case with Promoters Regulated by Escherichia coli Sigma E, Virgil Rhodius, Vivek Mutalik and Carol Gross

- 2BDA.3 Resolving Variable Dependencies in the MPDE-SSA Algorithm, Abiezer Tejeda, Chris Winstead, Eduardo Monzon, Chris Myers and Curtis Madsen

■ 7:00pm - 10:00pm, Dinner - Sponsored by ArtistDesign (<u>http://www.artist-embedded.org/artist/</u>) and COMBEST(<u>http://www.combest.eu</u>)

Tuesday – June 15th

- 8:30am 10:15am, Ballroom ABC

- General DAC Keynote (full conference)

- 10:30am Noon, Rm. 303CD

- Open Poster Session (full conference)

- Tech. Talks Session 3 Design of Biological Circuits and Networks

■ 3BDA.1 Automatic Design of Digital Synthetic Gene Circuits, Mario Marchisio and Joerg Stelling

■ 3BDA.2 Design of In-vitro Synthetic Gene Circuits Slides, Elisa Franco and Richard Murray

■ 3BDA.3 Fan-out Considerations in Gene Regulatory Networks, Kyung Kim and Herbert Sauro

- Noon 2pm, Rm. 203A

- Lunch (Rm. 203A or Terrance) and Posters Session 2 (Outside of Rm. 303CD)

- 2:00pm 3:00pm, Rm. 303CD

- Tech. Talks Session 4 Biological Pathway and Network Optimization

■ 4BDA.1s Predictably Profitable Paths in Metabolic Networks Slides, Ehsan Ullah, Mark Walker, Kyongbum Lee and Soha Hassoun

4BDA.2s Robust Inference of Biological Bayesian Networks Slides, Masoud Rostami and Kartik Mohanram

■ 4BDA.3s Pathway Identification for Strain Engineering Slides, Mona Yousofshahi, Kyongbum Lee and Soha Hassoun

■ 3:00pm - 4:00pm, Rm. 303CD

Panel Session - Sponsored by ArtistDesign (<u>http://www.artist-embedded.org/artist/</u>) and COMBEST(<u>http://www.combest.eu</u>)

Alberto Sangiovanni Vincentelli, University of California at Berkeley and University of Trento -Moderator

- Ron Weiss (MIT)

- J.Christopher Anderson (UC Berkeley)

- Andreas Kuehlmann (Cadence Research Labs)

- Andrew Phillips (Microsoft Research)

- 4:00pm 4:10pm, Rm. 303CD

- Closing Remarks, Doug Densmore (<u>http://ddensmore.net/</u>) (General Secretary)

- 4:30pm 6:00pm, Rm. 209AB

- Joint IWBDA/DAC Session, Invited Talks

- Pamela Silver (<u>http://openwetware.org/wiki/User:PamSilver</u> ), Harvard University

- J. Chris Anderson (<u>http://andersonlab.qb3.berkeley.edu/</u>), Berkeley

- Richard Murray (<u>http://www.cds.caltech.edu/~murray/wiki/Main\_Page</u>), Caltech

Meeting: 2010 Design Automation Conference Panel: Designing the Always-Connected Car of the Future, Chair: Alberto Sangiovanni-Vincentelli - Univ. of California, Berkeley, CA, University of Trento, Italy, Organizers: Arkadeb Ghosal - General Motors, Palo Alto, CA, Paolo Giusto - General Motors, Palo Alto, CA, Alberto Sangiovanni Vincentelli

#### **Objectives/Descriptions**

The automotive industry is introducing novel features, such as seamless vehicle-to-vehicle and vehicle-to-infrastructure connectivity to improve in vehicle driver safety (e.g., forward collision) and comfort (e.g., routing to avoid congestion) while facing stricter government regulations, and shortened time-to-market. As a result, automotive Electronic Control System (ECS) architectures are becoming increasingly complex. To cope with these challenges and opportunities, the entire automotive supply chain is engaged as follows: automotive OEMs are managing complexity by reusing legacy components and enabling new technologies; tier one suppliers are increasingly up-integrating features on the same computing platform; tier two suppliers are providing multicore and other powerful technologies; academic institutions are doing research in new analysis, synthesis and optimization methods; and tool providers are trying to raise the level of abstraction for system modeling, analysis and optimization.

The panel was attended by over 400 people and was considered one of the most successful panels of the Conference.

http://www.dac.com/conference+program.aspx

# Meeting: Workshop on Software Systems at ESWEEK 2010 Organizers Peter Marwedel, TU Dortmund, Germany and Alberto Sangiovanni-Vincentelli, UC Berkeley, US; University of Trento, I

This is the second year we organized this Workshop held during ESWEEK 2010. There were about 20 participants. Next year we will organize this workshop again.

#### **Objectives/Description**

An increasing amount of software is not written manually any more. Rather, software is synthesized from abstract models of the required functionality. As a result, the effort of generating software is reduced and software verification typically becomes easier.

Software synthesis has been implemented in various disperse communities.

The workshop aims at bringing these communities together and at identifying research problems which should be addressed by the scientific community.

## Program

| 8:30<br>am  | Opening                                                                                                                                                 | Alberto Sangiovanni-<br>Vincentelli (UC Berkeley,                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|             |                                                                                                                                                         | US)                                                                       |

| 8:40<br>am  | Keynote: Synthesis of Reliable Distributed Real-<br>Time Software                                                                                       | Edward Lee (UC Berkeley, US)                                              |

| 9:30<br>am  | coffee break                                                                                                                                            |                                                                           |

| 10:00<br>am | Software Synthesis in the LabVIEW Graphical<br>System Design Framework                                                                                  | Kaushik Ravindran and<br>Hugo Andrade (National<br>Instruments, US)       |

| 10:30<br>am | Code generation or software synthesis? Are they the same?                                                                                               | Alberto Sangiovanni-<br>Vincentelli (UC Berkeley)                         |

| 11:00<br>am |                                                                                                                                                         | Samarjit Chakraborty (TU<br>Munich, Germany)                              |

| 11:30<br>am | Synthesizing real-time implementations from abstract specifications based on timed automata                                                             | Jacques Combaz, Joseph<br>Sifakis and Tesnim<br>Abdellatif (IMAG, France) |

| 11:45<br>am | Are software synthesis and code generation<br>widely accepted in industry? What are the urgent<br>problems to solve to make it universally<br>accepted? | -                                                                         |

| 12:30       | Close                                                                                                                                                   |                                                                           |

http://www.esweek.org/

#### Meeting: Two Special Sessions on Compositional Techniques at DATE2011, Organizers Alberto Sangiovanni Vincentelli and Joseph Sifakis

Grenoble, March 17<sup>th</sup>, 2011

Participants: Trento, University of California at Berkeley, Verimag, ETH, INRIA, OFFIS, IST

Alberto Sangiovanni Vincentelli and Joseph Slfakis co-organized two special sessions of the Design and Test European Conference (DATE2011) on the achievements of our group. The allocation of two special sessions to the same group is an exceptional event due to the credibility of the team and the quality of the results.

#### Scope and Agenda

Special Session Type: Hot Topic

**Special Session Title:** Foundations of Component-based Design for Embedded Systems

#### Special Session Description

Component-based validation techniques for parallel and distributed embedded systems should be able to deal with heterogeneous components, interactions, and specification mechanisms. This special session describes a unified composition paradigm that allows the composition of subsystems with different execution and interaction semantics, combining computational and analytic models. This paradigm focuses on constructivity, which is reasoning about global system properties based on properties of its individual components.

#### Special Session Organizers:

Alberto Sangiovanni Vincentelli, University of California, Berkeley and University of Trento, USA and Italy, <u>alberto@eecs.berkeley.edu</u>: Joseph Sifakis, VERIMAG, France, sifakis@verimag.fr

#### **Special Session Moderator**

Joseph Sifakis, VERIMAG, France, sifakis@verimag.fr

#### **Presentations (90 min total)**

- 1st Presentation

- Presentation Length 30 min:

- **Title:** Composing heterogeneous components for system-wide performance analysis

- **Speaker** Lothar Thiele, ETHZ, Switzerland, thiele@ethz.ch:

- **1st Author** Lothar Thiele, ETHZ, Switzerland, <u>thiele@ethz.ch</u>:

- 2nd Presentation:

- Presentation Length 30min

- **Title:** Formal Methods for Composing Components

- Speaker Tom Henzinger, Institute of Science and Technology, Vienna, Austria, tah@ist.ac.at

- 1st Author Tom Henzinger, President, Institute of Science and Technology, Vienna, Austria, tah@ist.ac.at

- 3rd Presentation:

- Presentation Length 30min:

- **Title:** Requirement Engineering for Composition

- **Speaker** Albert Benveniste, INRIA, Rennes, France, benveniste@inria.fr

- o **1st Author** Albert Benveniste, INRIA, Rennes, France, benveniste@inria.fr

**Special Session Title:** Flows, Applications and Future of Component-based Design for Embedded Systems

#### **Special Session Description:**

It is essential that theoretical results developed by the community of researchers in the domain of compositionality be integrated in coherent component-based design flows that must validated in comparison with existing industrial practices. Furthermore, compositionality results should be implemented in scalable supporting methods and tools. The special session presents a component-based design flow, its application to specific industrial domains and to diverse areas of design endeavors such as energy efficient buildings and synthetic biology.

#### Special Session Organizers:

Alberto Sangiovanni Vincentelli, University of California, Berkeley and University of Trento, USA and Italy, <u>alberto@eecs.berkeley.edu</u>: Joseph Sifakis, VERIMAG, France, sifakis@verimag.fr

#### **Special Session Moderator**

Alberto Sangiovanni Vincentelli, University of California, Berkeley and University of Trento, USA and Italy, <u>alberto@eecs.berkeley.edu</u>

#### Presentations

- 1st Presentation

- Presentation Length 30 min:

- **Title:** Methods and Tools for Component-based Design

- **Speaker** Joseph Sifakis, VERIMAG, France, sifakis@verimag.fr

- **1st Author** Joseph Sifakis, VERIMAG, France, sifakis@verimag.fr:

- 2nd Presentation:

- Presentation Length 30min

- **Title** Using contract-based component specifications for virtual integration testing and architecture design

- **Speaker** Werner Damm, OFFIS, Germany, damm@offis.de

- o 1st Author Werner Damm, OFFIS, Germany, damm@offis.de

- **2nd Author** Eike Thaden, OFFIS, Germany

- **3rd Author** Ingo Stierand, OFFIS, Germany

- **4th Author** Thomas Peikenkamp, OFFIS, Germany

- **5th Author** Hardi Hungar, OFFIS, Germany

- 3rd Presentation:

- Presentation Length 30min:

- **Title:** Component-based Design for the Future

- Speaker Alberto Sangiovanni Vincentelli, University of California, Berkeley and University of Trento, USA and Italy, <u>alberto@eecs.berkeley.edu</u>

- 1st Author Alberto Sangiovanni Vincentelli, University of California, Berkeley and University of Trento, USA and Italy, <u>alberto@eecs.berkeley.edu</u>

## 3. Staff Mobility and Exchanges

#### From the Description of Work:

Staff Mobility and Exchanges between teams are essential for integration within and beyond the NoE, including mobility of students and/or researchers, between core teams, or between core teams and affiliated teams.

Mobility should be justified by and refer to involvement in an activity from the JPRA or JPIA, or one of the following: co-funded scholarships with industry; exchange of students and personnel within the consortium.

This is all new text: this entire chapter pertains only to activity in Year 3.

## 3.1 SW Synthesis, Code Generation and Timing Analysis cluster

**Visiting researcher:** Dipl.-Inf.Armin Größlinger (University of Passau) Team visited: ALCHEMY team, led by Albert Cohen (INRIA Saclay) Orsay, France, April 2009 – March 2010 Reason for the visit: pooling forces on GPGPU programming Conclusions/objectives reached: finalization of a prize-winning dissertation and a joint publication

Visiting researcher: Prof. Paul A. Feautrier (ENS Lyon) Team visited: LooPo team, led by Christian Lengauer (University of Passau) Passau, Germany, 5–23 April 2010 Approximate cost for travel and lodging: €2730 (paid for by the BFHZ) Reason for the visit: co-authorship of an encyclopedia entry on the polyhedron model Conclusions/objectives reached: entry submitted and accepted, publication in June 2011

Visiting researcher: Prof. Björn Lisper (Mälardalen)

Team visited: National University of Singapore, led by Abhik Roychoudhury (NUS) *Singapore – Sep. 5, 2010 to Sep. 9, 2010*

Approximate cost for travel and lodging: 2000€

Reason for the visit: Examination of a PhD thesis, and to discuss potential collaborations between Mälardalen and NUS.

Conclusions/objectives reached: There are a number of possible collaboration topics. One candidate is to use Mälardalen's concept of scoped flow facts to aid the scope-ware data cache persistence analysis being developed by NUS. Another possible topic is the use of loop invariant generation techniques for timing analysis. A third topic is industrial PhD programmes, where NUS wants to build up such a programme and where Mälardalen has considerable experience.

Visiting researcher: Benedikt Huber, MSc (TU Vienna)

Team visited: Mälardalen University, led by Björn Lisper (Mälardalen University)

Västeras, Sweden – Oct. 11, 2010 to Oct. 16, 2010

Approximate cost for travel and lodging: 970 €

Reason for the visit: Discuss connections and cooperation between the flow-analysis research at Mälardalen University and the work on writing time-predictable software at TU Vienna Conclusions/objectives reached: The precise input-data dependency analysis developed at TU Vienna provides an ideal basis to simplify the input model for Mälardalens abstract execution

engine SWEET, which has the potential to be used for an improvement of the scalability of flow analysis. From the perspective of TU Vienna, SWEET will be used to automatically derive flow facts for certain classes of programs the group at TU Vienna is investigating. We want to explore the relationship between these restricted program classes and the different merging strategies that need to be used in SWEET.

#### Visiting student : Volker Seeker (Technical University of Berlin)

Team visited: <u>Compiler and Architecture Design Group</u>, Björn Franke (University of Edinburgh) Edinburgh, United Kingdom – October 2010 to January 2011

Approximate cost for travel and lodging: 2.500 €

Reason for the visit: Volker Seeker is a student of Computer Science at the Technical University of Berlin. He is currently spending a couple of months at the University of Edinburgh to work on his master thesis. The topic of his thesis is "Design and Implementation of an Efficient Instruction Set Simulator for an Embedded Multi-Core Architecture". Volker's thesis is jointly advised by Björn Franke (Edinburgh) and Sabine Glesner (Berlin).

Conclusions/objectives reached: The thesis is expected to be finished in the first quarter of 2011. Hence, we will report about is conclusions and the objectives reached in the deliverables of 2011.

#### 3.2 Operating Systems and Networks cluster

Visiting researcher: PhD researcher, Gaetano Anastasi (University of Pisa) Team visited: Distributed Real-Time Systems Lab led by Marisol García-Valls (UC3M) Leganés, Spain – From October 2010 to July, 2010 Approximate cost for travel and lodging: 5000 € Reason for the visit: Research collaboration on QoS-based resource management. Conclusions/objectives reached: Joint publication of research collaboration.

**Visiting researcher:** Researcher, Ricardo Marau (University of Porto) Team visited: Distributed Real-Time Systems Lab, led by Marisol García-Valls (UC3M) *Madrid*, *Spain*– *October 25-30*, *2010*

Approximate cost for travel and lodging: 300 €

Reason for the visit: Research on project iLAND connected to ARTISTDesign activities. Conclusions/objectives reached: Design and implement combined resource management work in iLAND project.

Visiting researcher: Researcher, Axel Jantsch, (KTH)

Team visited: Real-Time Systems Lab (University of York)

York, UK– February 24-25, 2010

Reason for the visit: Discussion on predictable NoC architectures, real-time analysis for worstcase communication latency in NoCs, use of network calculus to provide latency bounds for traffic over NoCs.

Conclusions/objectives reached: Clearer view on the different analysis approaches (real-time analysis and network calculus) and the requirements they impose on the application and NoC platform models. Ideas to build a TLM model of a NoC which mixes analysis and simulation, aiming to high simulation speed and high accuracy

Visiting researcher: Researcher, Lothar Thiele (ETH Zurich)

Team visited: Real-Time Systems Lab, Scuola Superiore Sant'Anna (Pisa)

Pisa, Italy- March 22-23, 2010

Approximate cost for travel and lodging: 1000€

Reason for the visit: Organization of a course on real-time calculus. Research on real-time schedulability analysis.

Conclusions/objectives reached: New ideas were exchanged for the investigation of multimode reservation servers that guarantee timing behaviour during mode transitions.

#### Visiting researcher: PhD researcher, Rui Santos (Universities of Porto and Aveiro)

Team visited: MRTC, Malardalen University, (Malardalen)

Vasteras, Sweden – March 15-June 30, 2010

Approximate cost for travel and lodging: 3000€

Reason for the visit: Research on hierarchical scheduling for Ethernet switches.

Conclusions/objectives reached: A hierarchical framework for enhanced Ethernet switches was derived together with a response time analysis.

Visiting researcher: Researcher, Luis Almeida (University of Porto)

Team visited: Real-Time Systems Lab, Scuola Superiore Sant'Anna (Pisa) *Pisa, Italy– April 27-30, 2010*

Approximate cost for travel and lodging: 1000€

Reason for the visit: Organization of a course on real-time networks. Research on real-time networks.

Conclusions/objectives reached: New ideas were exchanged for the development of mobile sensor networks with real-time requirements.

Visiting researcher: Researcher, Shantao Chen (Zhejiang University)

Team visited: DaRTES lab, University of Porto, (UnivPorto)

Porto, Portugal – May 1 - -July 31, 2010

Approximate cost for travel and lodging: 2250€

Reason for the visit: Research on adaptive wireless sensor networks for tracking applications. Conclusions/objectives reached: An approach was developed to balance energy consumption and tracking accuracy/responsiveness using a dual-rate beacon scheduling technique.

**Visiting researcher:** Researcher, Julian Proenza (University of Balearic Islands) Team visited: Distrib. and Real-Time Embedded Systems Lab, University of Porto (UnivPorto) *Porto. Portugal – July 1-August 1, 2010*

Approximate cost for travel and lodging: 1500€

Reason for the visit: Research on projects HaRTES and CANbids related ARTISTDesign activities.

Conclusions/objectives reached: Definition of further steps in the collaboration towards faulttolerant mechanisms for adaptive systems. Start of preparation of joint paper on formal dependability assessment of ReCANcentrate.

Visiting researcher: PhD researcher, Augusto Oliveria (University of Waterloo)

Team visited: DaRTES lab, University of Porto, (UnivPorto)

Porto, Portugal – October 11 – November 13, 2010

Approximate cost for travel and lodging: 1500€

Reason for the visit: Collaboration in the scope of the distributed resource management. Conclusions/objectives reached: Development of a versatile tagging approach that simplifies accounting for resource consumption in a distributed setup.