# MADES

Neil Audsley, Ian Gray, Leandro Indrusiak, Dimitris Kolovos, Nikos Matragkas, Richard Paige

> Department of Computer Science The University of York

## MADES

- EU FP7 STREP project April 2010 for 30 months

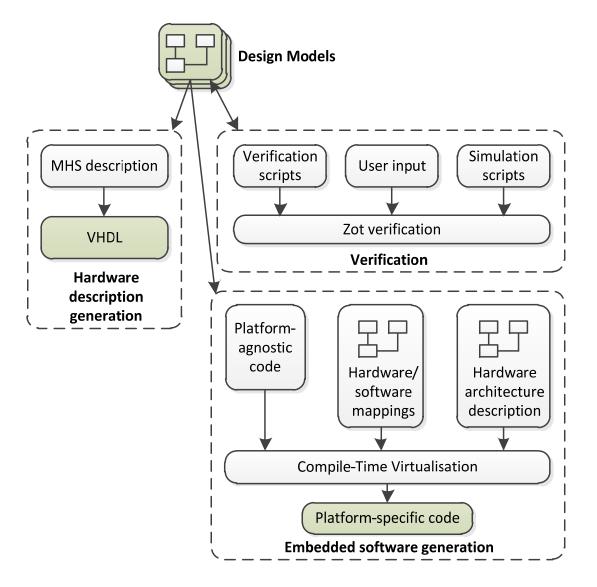

- Model-driven Code Generation for Embedded Systems

- UML + MARTE to Real-Time Java / C++

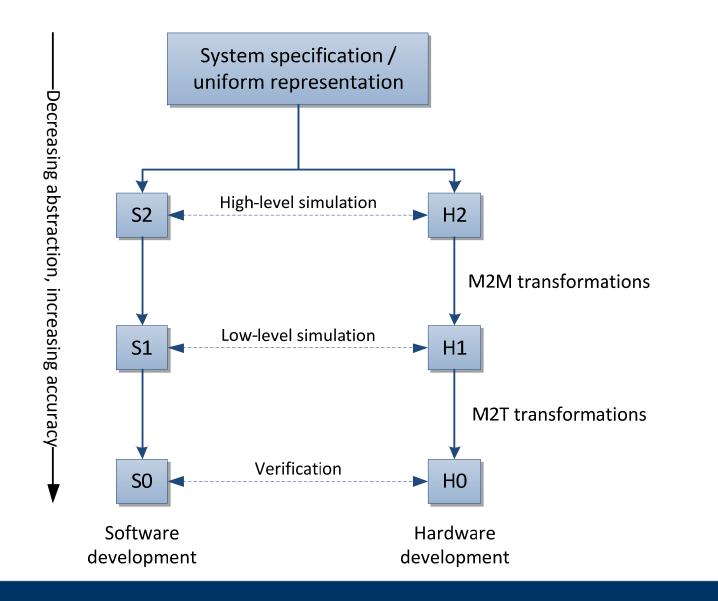

## Modelling overview

### Hardware models

| Model | Modelling level                    |                                                                                                | System C<br>simulation level         |

|-------|------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------|

| H2    |                                    | Topology not<br>modelled, totally-<br>connected network<br>assumed                             | Functional                           |

| H1    | CPU - CPU<br>CPU - Mem<br>Mem      | Topology modelled,<br>untimed, simple<br>functional model<br>reduces accuracy of<br>simulation | Transaction-level<br>modelling (TLM) |

| НО    | CAN bus<br>Arm 9<br>DCache<br>DDR2 | Complete hardware<br>model, allows<br>verification                                             | Cycle-accurate                       |

#### Model Verification and Code Generation