## SymTA/S - Roadmap

# Future of standards and tools for schedulability analysis

#### ArtistDesign Workshop on Real-Time System Models for Schedulability Analysis

Christoph Ficek

Santander, February 7-8, 2011

Solutions for Complex

**Real-Time Systems**

### **Future work**

- Full integration of SymTA/S in design and development processes in automotive

- □ Interfaces, tool chains, etc.

- Upcoming analysis topics:

- □ Gateway analysis

- □ Multi-Core

- □ Aerospace

- Ethernet

## **Early-Phase: Virtual Timing Verification**

Network:

- network topology options

- bus configuration rules

ECU:

- initial task layout & software architecture

- execution time budgets / estimates

- virtual timing verification

- avoid late timing problems

- system optimization

## **Late-Stage: Integration Verification**

#### Network:

□ fixed topology

detailed network configuration

#### ECU:

- detailed OS configuration

- measured execution times

- "real" timing verification

- system fine-tuning

- safety guarantees

Symtavision Product Strategy and Roadmap February 2011 © Symtavision GmbH, Germany

4

#### **Test & Integration Verification**

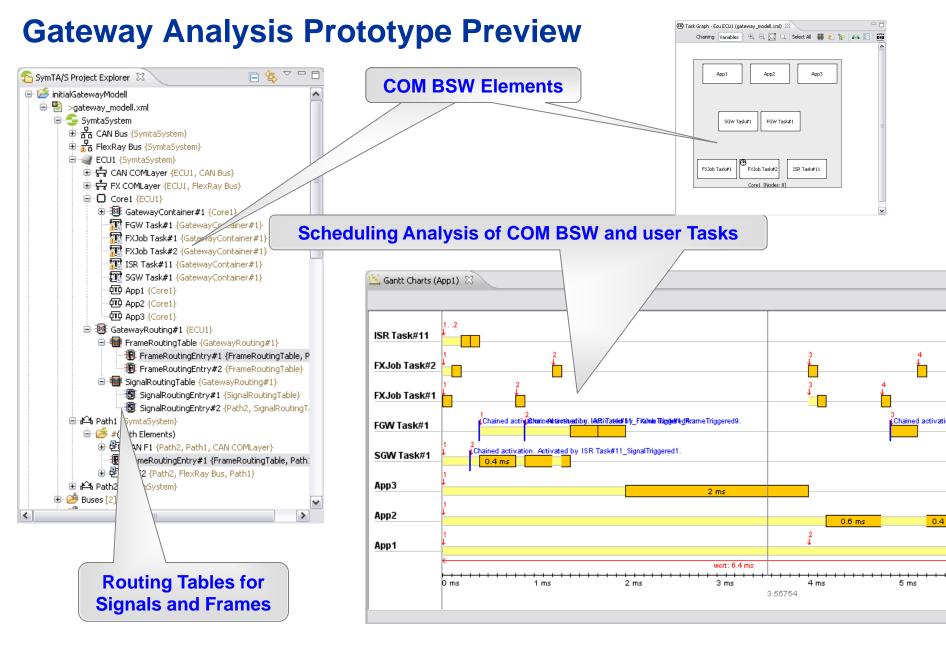

## **Gateway Analysis Library**

- Modeling of gateway timing:

- □ COM BSW components: CAN ISRs, FlexRay jobs, gateway tasks

- configuration data: signal & frame routing tables

- combination with application software tasks

- □ scheduling analysis of BSW execution & routing delay

#### Design support:

- □ GW SW architecture optimization

- □ GW delay minimization

- avoidance of critical ASW disturbance

- interface: ARXML and SymTA/S XML

Symtavision Product Strategy and Roadmap February 2011 © Symtavision GmbH, Germany

## **Multicore Feature Roadmap in SymTA/S**

- waiting effects due to runnable chains across cores

- Communication cost analysis

- □ different memory imply different data access time

- work done at Symtavision (together with Infineon, publication imminent)

- prototype exists

- Consideration of timing implication of locking semaphore across cores

- □ critical sections can contain also memory accesses

- work performed at TUBS

- current goal is to enable prototype in SymTA/S

- Automatic SW-mapping in multicore environment

- □ Runnable remapping and task schedule sysnthesis

Symtavision Product Strategy and Roadmap February 2011 © Symtavision GmbH, Germany

## Symtavision Aerospace Roadmap

- Status: Available prototypes for

- □ ARINC 653 (IMA)

- □ ARINC 664 (AFDX)

- Next:

- □ Productization of ARINC 653 (IMA) and CAN for aerospace

- Collaboration with lead customers

## Thank You !

### **Contact information**

Symtavision GmbH Frankfurter Str. 3C 38122 Braunschweig Germany www.symtavision.com

ficek@symtavision.com

Tel +49 531 886 179-00

Fax +49 531 886 179-29