# Modeling and Verification of Memory Architecture with AADL and REAL

Stéphane Rubini and Frank Singhoff - University of Brest, UEB, France {stephane.rubini,frank.singhoff}@univ-brest.fr Jérome Hugues - University of Toulouse, ISAE, France jerome.hugues@isae.fr

April 27, 2011

# Outline

#### Why to model memory systems?

- Memory components are not universals

- The memory hierarchy

- Memory Layout Examples

#### 2 Modeling of memory

- 3 Check the consistency of the model

- 4 Conclusion and futher works

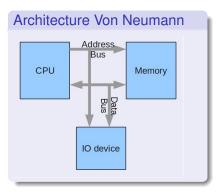

# Why to model memory systems ?

But, today's memory systems are not so simple !

The universal memory technology, suitable to all needs, does not exist.

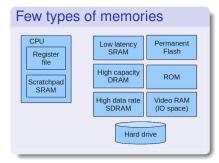

## Why to model the memory systems ? (2)

Design space of a memory system

- Performances (capacity, latency, data rate)

- Capabilities (persitency, supported operations, access type and ports)

- Other criteria (reliability, consumption, cost, robustness, ...)

In a computer system (embedded), the memory is a resource which must be characterized.

- Design phase : complexity, cost

- Verification and validation : software usage (amount of resources, access time variability, technological limits, ...)

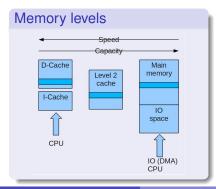

# The memory hierarchy

- Memory wall, consumption ⇒ memory hierarchy, cache memories (1 or more levels)

- 1 variable = 1 or more physical storage locations

- $\Rightarrow$  Coherency (read sensitive address, Direct Memory Access)

- $\Rightarrow$  Predictability (how to evaluate the WCET ?)

- $\Rightarrow$  Shared memory in multi-processor context

Needs to control how the data are managed within the memory hierarchy.

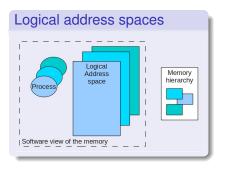

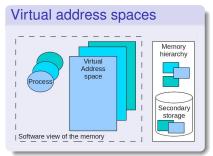

## The memory hierarchy: logical and virtual address

- One logical address space per process (or task)

- Address translation: logical address  $\rightarrow$  physical address in the real memory

- Process (or task) isolation

# Memory layout examples

### VxWorks (MC68040 board) Physical address space

| sysMemTop()    | System memory pool |

|----------------|--------------------|

| Size of 0x1000 | Interrupt stack    |

|                | Boot code and data |

| _end symbol    | system image       |

|                | (Text, data, BSS)  |

| 0x1000         |                    |

|                | Initial stack      |

| 0x0900         |                    |

|                | Exception messages |

| 0x0800         |                    |

|                | Boot line          |

| 0x0700         |                    |

| 0.0100         | Reserved           |

| 0x0120         |                    |

| 0x0000         | Interrupt vectors  |

| 0x0000         |                    |

### Windows Embedded CE6 Logical address space

| FFFF FFFF |                       |

|-----------|-----------------------|

|           | Static Mapped         |

| A000 0000 | Uncached              |

|           | Static Mapped         |

| 8000 0000 | Cached                |

| 7000 0000 | Shared System Heap    |

|           | Memory Mapped Objects |

| 6000 0000 |                       |

|           | Shared User Mode DLL  |

| 4000 0000 |                       |

|           | Per process           |

|           | virtual space         |

|           |                       |

|           | code                  |

| 0000 0000 | reserved              |

# Outline

#### Why to model memory systems ?

#### 2 Modeling of memory

- Modeling Guideline and Goals

- AADL Properties

- Examples

3 Check the consistency of the model

4 Conclusion and futher works

# Modeling Guideline

Hardware modeling

- Describe the physical features of memory components.

- Describe their mapping within the physical address space of a processor.

Software view modeling

- Describe the memory segments as defined by the OS and the applications. A memory segment is a range of address dedicated to a given usage, which must support a same set of operations.

- Describe their mapping within the address space (process memory layout); this layout may be different than the physical one.

# Modeling goal and Exploitation

- Define the matching (static) between the software view and the hardware implementation of the target memory system.

- Validate the software requirements and the physical features of the target memory features match.

- Sontrol the development chain for targeting a given memory system.

- Estimate, from the model, the quantitative and functional memory requirements for a software component.

- Back-annotate (update) the model with the memory usage information arises from the code generation.

# Core AADL Properties useful for memory models

- Base\_Address : aadlinteger 0 .. Max\_Base\_Address address of the first word in the memory

- Source\_Stack\_Size: Size, Source\_Heap\_Size: Size, Source\_Data\_Size: Size, Source\_Code\_Size: Size maximum size of respectively the stack, heap, data and code

- Word\_Space: aadlinteger 1 .. Max\_Word\_Space => 1 word alignment constraints

- Word\_Size: Size => 8 bits smallest independently readable and writable unit of storage in the memory

- Byte\_Count: aadlinteger 0 .. Max\_Word\_Count number of bytes in the memory

# Properties from the ARINC653 annex

- Supported\_Access\_Type : type enumeration (read, write, read\_write)

- Access\_Type : Supported\_Access\_Type

- Supported\_Memory\_Kind : type enumeration (memory\_data, memory\_code)

Memory\_Kind : Supported\_Memory\_Kind

Limitations :

- The memory types do not encompass the diversity of the usage of the memory segments.

- The access types do not represent all the operational aspects bound to some memory technologies.

# New properties

segment\_kind, precises the segment type: (1) address space or (2)memory

segment.

- An address space represents only a range of memory addresses. The property address\_kind models the actual implementation of the address:

- physical: the address selects directly a word stored in a memory component (in fact a semiconductor memory);

- logical: the address selects a word stored in a memory component, optionally after an address translation;

- virtual: the address selects a word stored in the main memory, or in a slower secondary memory device;

- io\_register: address registers to control or communicate with input/output (read-sensitive locations).

- A memory segment represents a set of memory words accessible within a range of addresses. One and only one word is mapped to each address.

## Additional properties

#### • aadl\_project.aadl: access type and memory kind defined per project

Supported\_Memory\_Kind : **type enumeration** (text, stack, heap, bss, data\_seg, memory\_system\_pool); Supported\_Access\_Type : **type enumeration** (read, write, execute, slow\_write, erase);

• memory\_segment\_properties.aadl: an additional property set

property set Memory\_Segment\_Properties is Supported\_Address\_Kind: type enumeration (physical\_as, logical\_as, virtual\_as, io\_register\_as); Address\_Kind : Supported\_Address\_Kind applies to (memory); Supported\_Segment\_Kind : type enumeration (memory\_segment, address\_space); Segment\_Kind : Supported\_Segment\_Kind applies to (memory); Page\_Size : Size applies to (memory); end Memory\_Segment\_Properties;

#### • arinc653\_properties.aadl: an update proposition

— Supported\_Access\_Type : type enumeration (read, write, read\_write); into aadl\_project — Supported\_Memory\_Kind : type enumeration (memory\_data, memory\_code); Access\_Type : list of Supported\_Access\_Type applies to (memory);

# Layout of the memory

#### Layout of the segment "system image"

memory implementation memory\_segment.system\_image subcomponents

```

seg text : memory memory segment.impl {

Base Address => 016#001000#;

arinc653::Memory Kind => text;

arinc653::Access Type => (execute, read);

Byte Count => 3000; };

seg bss : memory memory segment.impl {

Base Address \Rightarrow 016#003000#;

arinc653::Memory Kind => bss: }:

seg data : memory memory segment.impl {

Base Address => 016#002000#;

arinc653::Memory Kind => data seg; };

properties

Base Address => 016#001000#:

arinc653:: Memory Kind => image:

end memory segment.system image;

```

# Binding logical and physical view

system implementation vxworks.impl subcomponents

| processi    | • | process noue_a.mpr,                    |

|-------------|---|----------------------------------------|

| logical_as  | : | <b>memory</b> address_space.vxworks;   |

| physical_as | : | <pre>memory address_space.mv162;</pre> |

| cpu1        | : | <pre>processor MC68040.impl;</pre>     |

#### properties

# Outline

3

Why to model memory systems ?

#### 2 Modeling of memory

Check the consistency of the model

- Ocarina, REAL annex

- What can we check ?

- REAL Theorem Examples

#### 4 Conclusion and futher works

# **REAL** Language

- REAL (Requirement Enforcement Analysis Language), a Domain-Specific Language, implemented as an AADL language annex.

- Based on set theory and associated mathematical notations, a REAL theorem verifies an expression over all the elements of a set of AADL entities.

- Checking constraints enforcement on AADL architectural descriptions at the specification step:

- Enabling easy navigation through AADL model elements;

- Allowing for modularity through definition of separate constraints that can be later combined;

- Being integrated as an AADL annex language, constraints are coupled to models.

## What can we check on the memory model

We defined 21 REAL theorems to be validated on a model.

- General memory layout constraints check whether the memory layout as described by the AADL model is consistent with its definition:

- usage of modeling patterns, size of segments, non-overlapping of segments.

- Software binding constraints check that software components memory requirements match the resources provided by the hardware:

- address space binding, access types, address translations, software segment sizes.

- Alignment constraints ensure all memory boundaries are correctly aligned:

- word size and page size alignments.

- Specifics VxWorks constraints:

- software segment sizes and order.

# Check the memory model: example 1

Within a memory segment that describes a range of memory words, sub-segments cannot be "address space" segment.

Consistency check

```

theorem check_memory_segment_structure

foreach seg in Memory_Set do

sub_segments := {x in Memory_Set |

property_exists(seg, "Memory_Segment_Properties::Segment_Kind") and

property(seg, "Memory_Segment_Properties::Segment_Kind") = "memory"

and ls_Subcomponent_Of (x, seg) };

```

```

sub_memories := {x in sub_segments |

property_exists(x, "Memory_Segment_Properties::Segment_Kind") and

property(x, "Memory_Segment_Properties::Segment_Kind") = "memory" };

```

check (sub\_segments = sub\_memories); end check\_memory\_segment\_structure;

## Check the memory model: example 2

All the access types supported by a segment must be also supported by all its sub-segments.

```

Consistency of the allowed access types

theorem check_allowed_access

foreach m in Memory_Set do

good_segments:={x in Memory_Set |

Is_Subcomponent_Of (x, m) and (

not property_exists(x, "arinc653::Access_Type") or

Is_In(property(m, "arinc653::Access_Type"),

property(x, "arinc653::Access_Type"))) };

segments:={x in Memory_Set | Is_Subcomponent_Of (x, m)};

check ( cardinal(good_segments) = cardinal(segments) );

end check_allowed_access;

```

The REAL operator *Is\_In* is used to check whether all the access rights of a segment are included in the rights of its sub-segments.

# Outline

- Why to model memory systems ?

- 2 Modeling of memory

- 3 Check the consistency of the model

- 4 Conclusion and futher works

## Conclusion

- We have defined a set of AADL properties to describe more precisely a system memory layout;

- The REAL DSL has been shown to be useful in verifying the internal consistency of the memory model;

- A precise memory model  $\Rightarrow$  Characterizing of Components Off The Shelf

Remains to be done

- Control the development chain from the memory model → generation of linker scripts

- Back-annotate the model from the produced code

- size and localization of the memory segment

- localization of the system objects

- estimation of the memory footprints of a system.

- And so far : Cache Conscious Data Placement (CCDP)