Practical Embedded Systems Engineering Syllabus for Graduate Students with Multidisciplinary Backgrounds

Bastian Haetzer Gert Schley Rauf Salimi Khaligh **Martin Radetzki**

Embedded Systems Engineering / CSEE / U Stuttgart

# **Overview**

- 1. Context

- 2. Embedded systems courses

- 3. Practical (lab) course

- 4. Experiences

- 5. Conclusion

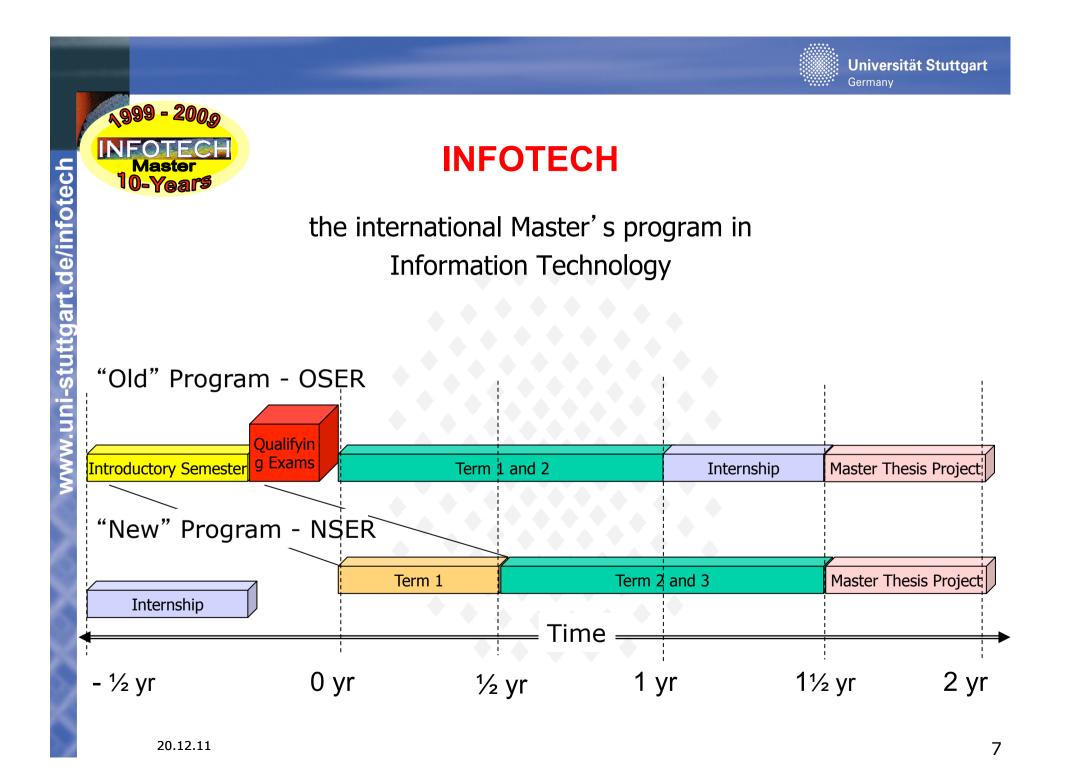

#### **INFOTECH Master**

- INFOTECH is a multidisciplinary (EE & CS) international master program

- On top of a qualifying Bachelor degree

- Leading to a Master of Science Degree (M.Sc.) in Information Technology

- With a regular study time of 4 terms (3 teaching + 1 Master Thesis)

- > Is truly international

- > Is multidisciplinary

- > 4 specializations (majors) can be selected

- Communication Engineering and Media Technology

- Embedded Systems

- Micro- and Optoelectronics

- Computer Hardware/Software Engineering

www.uni-stuttgart.de/infotech

#### **History and Facts**

- has been set up in 1999 (is in its 12<sup>th</sup> year)

- Attracted some 9500 applications

- Had applications from graduates of more than 1000 different universities

- From 116 different countries

- Admitted some 600 students

- Conferred 310 Master Degrees

- Offers 4 majors

- Is supported by some 20 professors of the faculty (faculty total of 30), 10 professors from other faculties and some 5 industry lecturers

- Some 55 Lecture Courses

- Some 10 Lab Courses

- Some 10 Seminars

- Currently admits 80 students / yr from > 1200 applicants

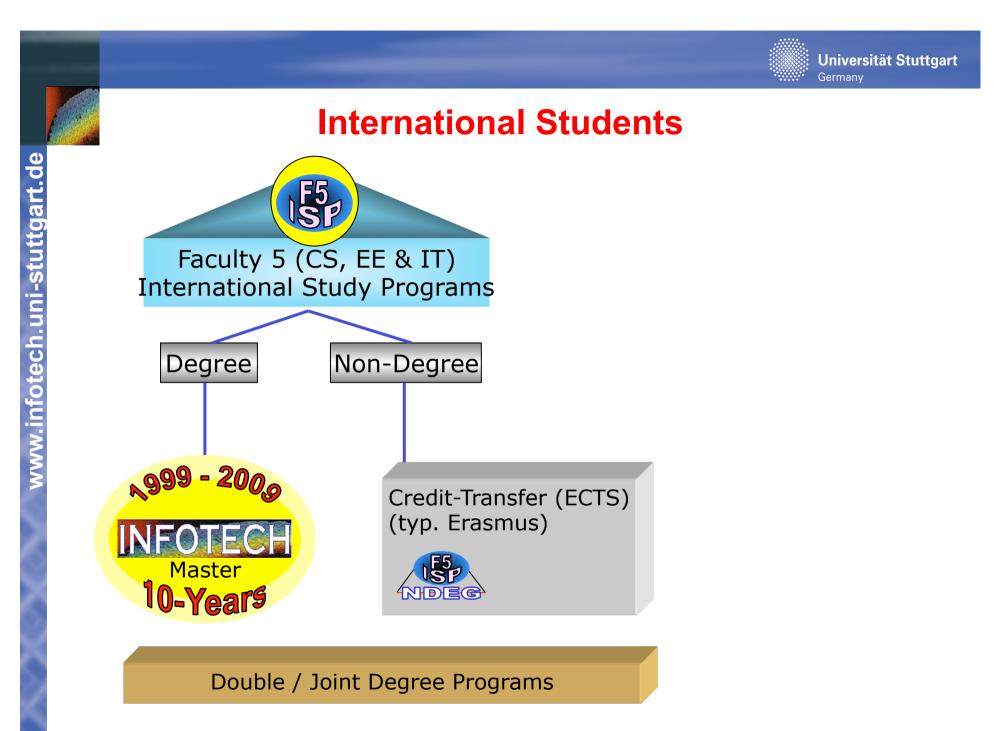

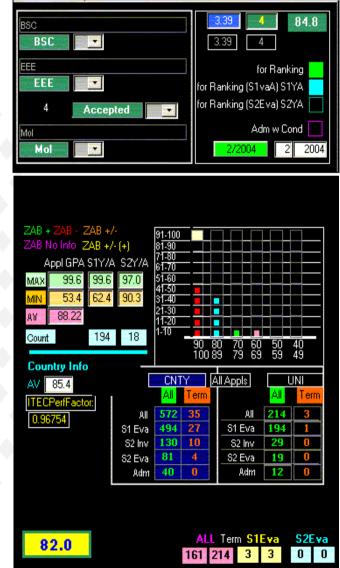

#### **Admission Selection**

Part-view of Applicants Database

- Several "Competition Groups" (e.g. World, Partner, etc.)

- Selection mainly on GPA basis

- Within group / University/ Country/ World

- Based on comprehensive experience and reference data from previous applications

- With weighted GPA (Itec Performance Factor)

- And based on Ranking of applicant

- And based on "Reputation of University" (Media, Own experience)

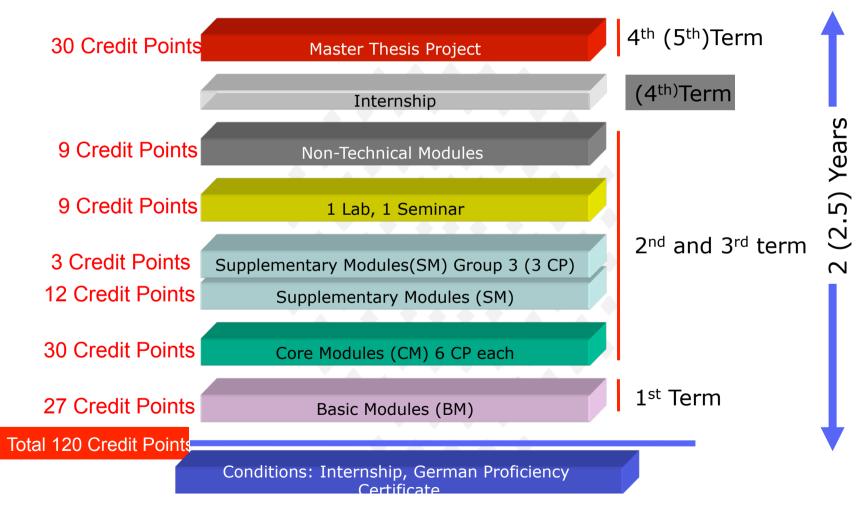

#### The Curriculum INFOTECH Master

#### **Basic Modules (1<sup>st</sup> Term)**

Basic Modules (BM)

- Advanced Higher Mathematics (AHM)

- "Container" Electronics and Communication (EC) with

- Communications (Com)

- System and Signal Theory (SST)

- Radio Frequency Technology (RF)

- Electronic Circuits (EIC)

- "Container" Computer Science (CS) with

- Programming Languages (PL)

- Computer Architecture and Organization (CAO)

- Data Structures and Algorithms (DSA)

- Operating Systems (OS)

#### Embedded Systems Core Modules

#### Core Modules (CM): 5 out of 12

- Advanced Processor Architecture

- Communication Networks I

- Communications III

- Design and Test of Systems-on-a-Chip

- Distributed Systems

- Embedded Systems Engineering

- Industrial Automation Systems

- Intelligent Sensors and Actors

- > Modelling, Simulation and Specification

- Real-Time Programming

- Software Engineering for Real-Time Systems

- Statistical and Adaptive Signal Processing

999 - 2000

Master

10-Years

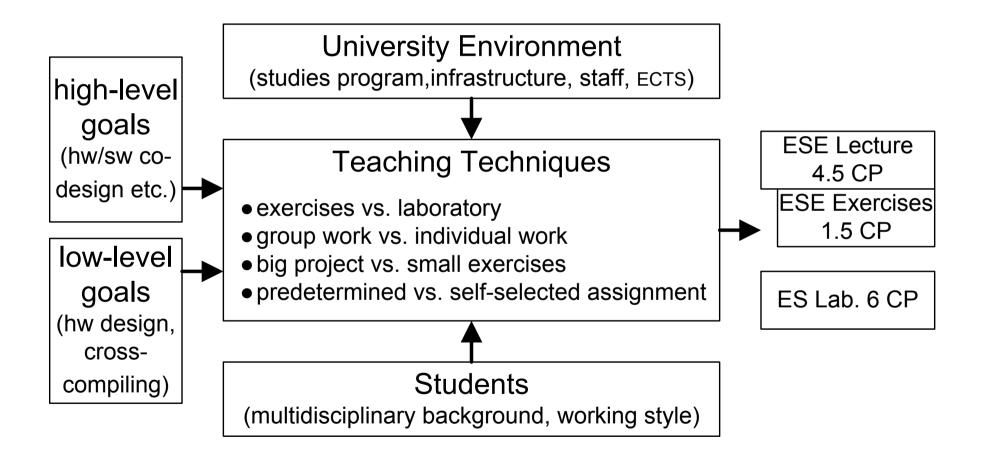

# Syllabus design

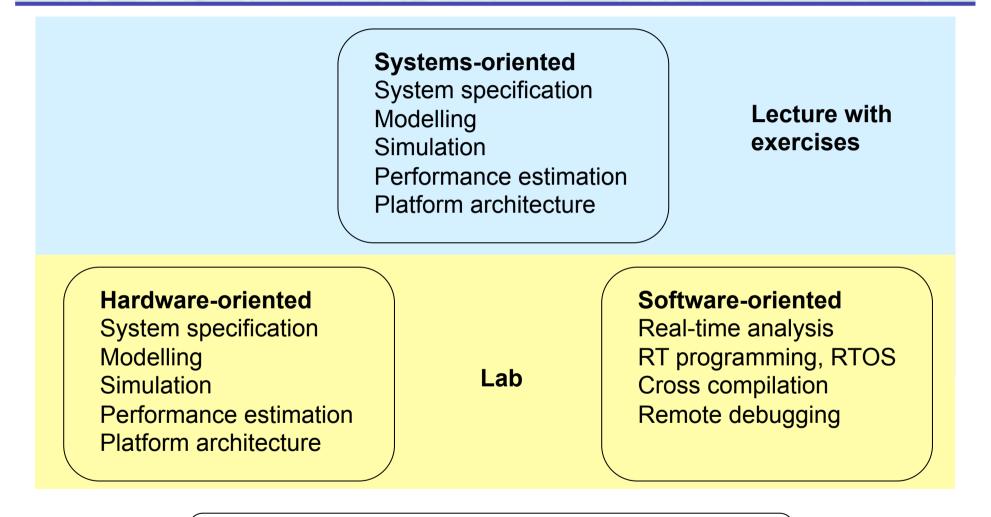

## **ES syllabus focus areas**

#### Application-oriented

Multimedia | Automotive | Robotics | ...

## **ESE lecture with exercises**

**Theory (exercises on paper, with ILP):** High-level synthesis: from algorithm to RTL, Pipelined data paths and controllers, Software scheduling: periodic and sporadic, Software on bare CPU vs. RTOS, schedulability tests, System architecture, storage and communication, HW/SW integration

#### **Practice (exercises in lab):**

| Task 1 | Session 1 | Processor-peripheral communication with memory-mapped I/O |

|--------|-----------|-----------------------------------------------------------|

| Task 2 | Session 2 | Implementation of the interrupt handler                   |

| Task 3 | Homework  | Design of a frame-based scheduler                         |

| Task 4 | Session 3 | Implementation of a framed-based scheduler                |

|        | Session 4 |                                                           |

### **Embedded Systems Lab**

# Lab design trade-offs

| Lab experiments                           | Structured lab assignment | Large project                                                                  |

|-------------------------------------------|---------------------------|--------------------------------------------------------------------------------|

| + guidance<br>+ focus<br>– no big picture | Lab                       | <ul> <li>(+) motivation</li> <li>+ overview</li> <li>– getting lost</li> </ul> |

| Norking individually | Working in groups           | Project team                       |

|----------------------|-----------------------------|------------------------------------|

| + grading            | + learn from each other     | + real-world                       |

| + focus Lab          | – one does all the work     | + soft skills                      |

| + individual advice  | + higher admission possible | <ul> <li>teaching costs</li> </ul> |

| Fixed assignment                         | Individual assignments                    | Self-assignment                    |

|------------------------------------------|-------------------------------------------|------------------------------------|

| + costs                                  | + adaptation to interests                 | (+) motivation                     |

| + focus both                             | <ul> <li>arbitration necessary</li> </ul> | – risk                             |

| <ul> <li>– invites plagiarism</li> </ul> | <ul> <li>teaching costs</li> </ul>        | <ul> <li>teaching costs</li> </ul> |

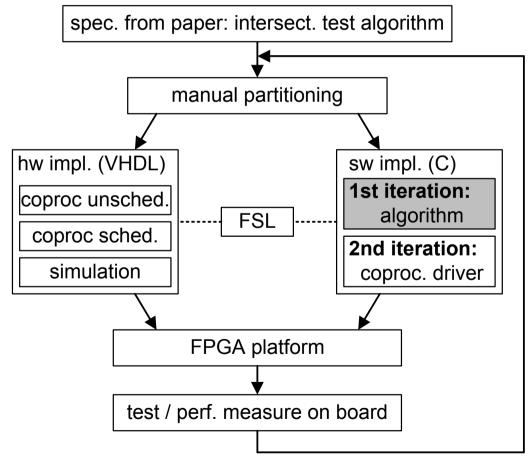

### **Design flow**

# Canonical embedded systems design flow

#### specification partitioning hardware software interface design design design integration verification

#### Design flow in lab

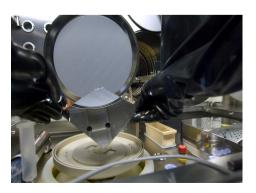

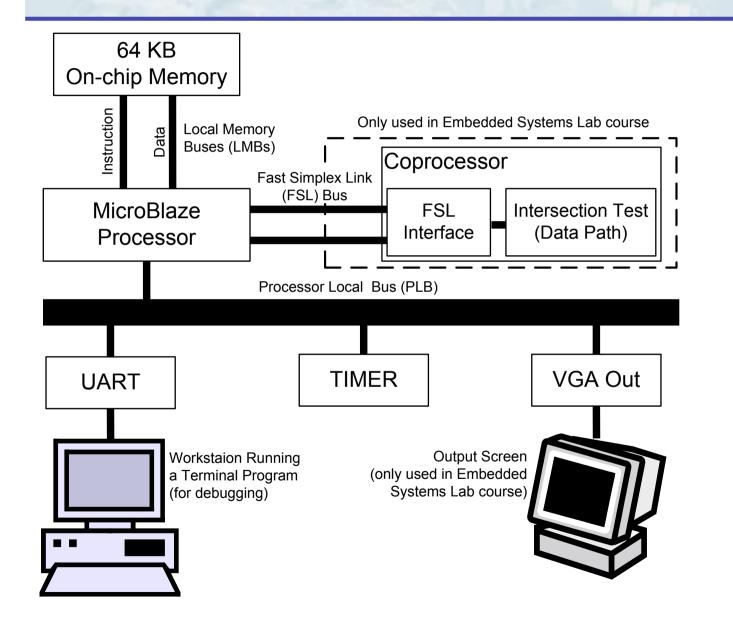

# **FPGA platform**

Initial try: ARM 7/9 + FPGA

Xilinx Univ. Programme boards

old: XUPV2P Virtex-II

new: XUPV5 Virtex-5

# Lab assignment (old)

| Part 1 | Session 1    | Introduction to XPS + platform building and basic I/O                                                                                                                                                                                                                                                                        |  |

|--------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|        | Session 2,3  | Software Implementation of algorithm + performance measurement                                                                                                                                                                                                                                                               |  |

| Part 2 | Session 4-11 | <ul> <li>Dataflow graph of algorithm</li> <li>Unscheduled implementation of operators</li> <li>Scheduling of operators</li> <li>Datapath with scheduled operators</li> <li>FSL-interface design</li> <li>Integration of coprocessor into platform</li> <li>Driver implementation</li> <li>Performance measurement</li> </ul> |  |

Many students got lost in part 2 due to

- lack of overview, unstructured working style

- lack of basic knowledge, in particular in VHDL

# Lab assignment (new)

#### Admission requires entry test in C and VHDL

| Part 1 | Session 1   | XPS Tutorial (Platform building + basic I/O)                                       |  |

|--------|-------------|------------------------------------------------------------------------------------|--|

|        | Session 2   | Software impl. of algorithm + performance measurement                              |  |

|        | Session 3   | VHDL crash course (simple traffic light)                                           |  |

| Part 2 | Session 4,5 | Dataflow graph of algorithm, unscheduled implementation + datapath testbench       |  |

|        | Session 6   | Scheduling of operators e.g. cross product                                         |  |

|        | Session 7   | Datapath with scheduled operators, simulation                                      |  |

|        | Session 8,9 | FSL-interface design (state machine) + integration of<br>coprocessor into platform |  |

|        | Session 10  | Driver implementation + performance measurement                                    |  |

| Part 3 | Session 11  | System simulation + software enhancement (assembler)                               |  |

|        | Session 12  | Pipelining of FSL communication                                                    |  |

# Deliverables

- Software code, structured and with comments

- VHDL code, structured and with comments

- Demo

- "sales presentation" of the results: speedup, FPGA area

- verbal examination, questioning of design decisions

- Written documentation (datasheet)

- data path documentation: IFs, structure, schedule

- controller documentation: IFs, FSM diagram

- SW integration documentation: FSL interface, register map

- measurements documentation

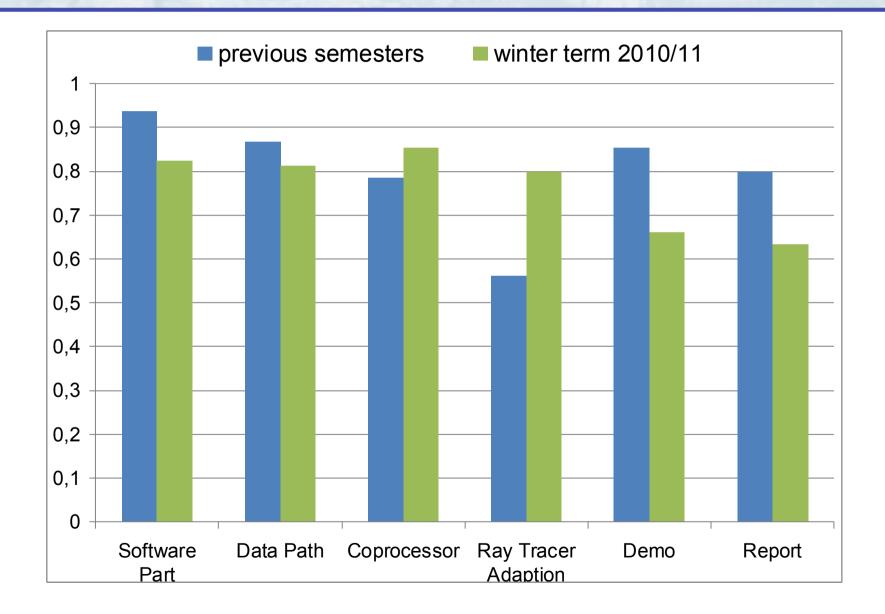

# **Fraction of points**

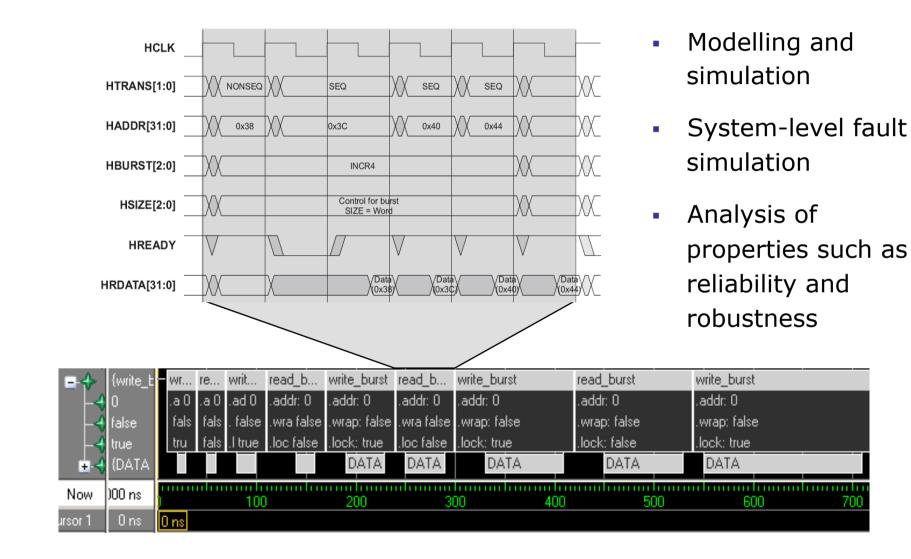

#### **Research: embedded architectures**

- Hardware/software architecture

- Many-core computing systems

- System communication

- Bus subsystems

- Networks-on-Chip

- Reconfigurable architectures

- Fault-tolerant architectures

Sample design (left): MPEG-4 H.264 video codec with ARM9 CPU and Xilinx Virtex5 FPGA to implement hardware accelerators

### **Research: design methods**

- Embedded HW/SW design fundamentals, valid for any application

- Heterogeneity of students' capabilites and backgrounds

- Monitoring results by qualitative and quantitative evaluation

- Monitoring the embedded market

- Continuous improvement of syllabus, courses