# From Streaming Models to Hardware and Software Implementations

Kaushik Ravindran and Hugo Andrade National Instruments Corporation, Berkeley, CA, USA

> Workshop on Software Synthesis October 14, 2011

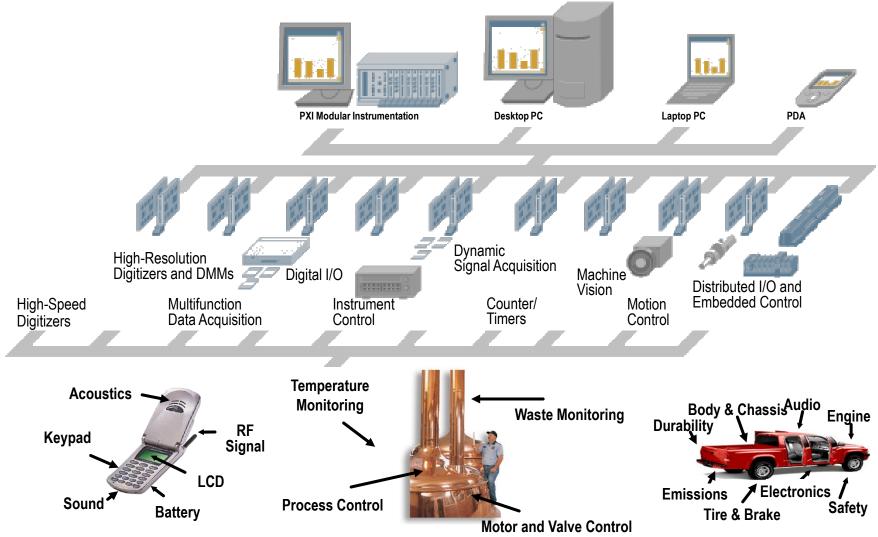

#### National Instruments: What We Do

<text><text><image><image>

#### Used By Engineers and Scientists for Test, Design and

# Virtual Instrumentation

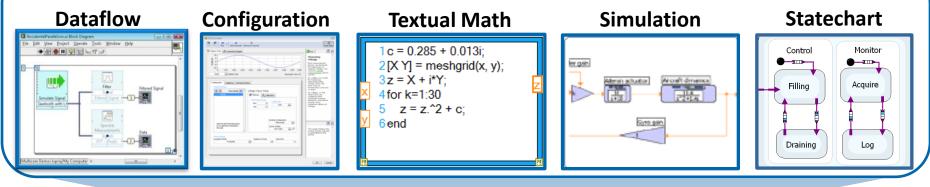

#### LabVIEW: Graphical System Design

#### **High-Level Design Models**

**Graphical Programming**

# Outline

- DSP Designer framework

- Models, analysis, and exploration

- Deployment challenges

- Summary

#### Motivation

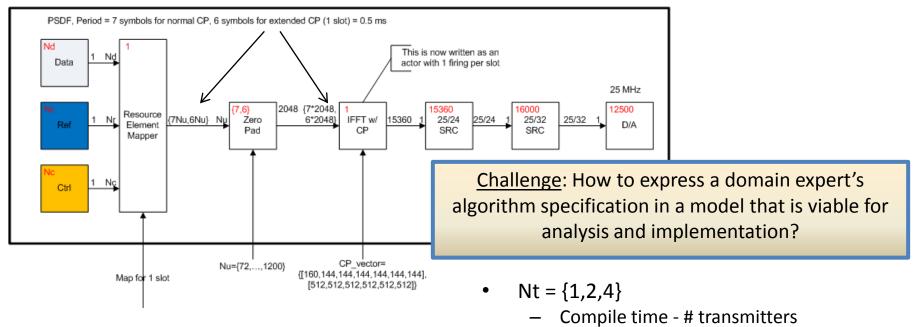

### Streaming Model of the OFDM Transmitter

- Nu = {72, 180, 300, 600, 900, 1200}

- Initialization time Bandwidth

- CP mode = {'Normal', 'Extended'}

- Run time

- To overcome Inter-symbol-interference

- Can be applied at symbol boundary

- CP Vector

- Vector elements must be applied at symbol boundary

- Vector selection based on CP mode

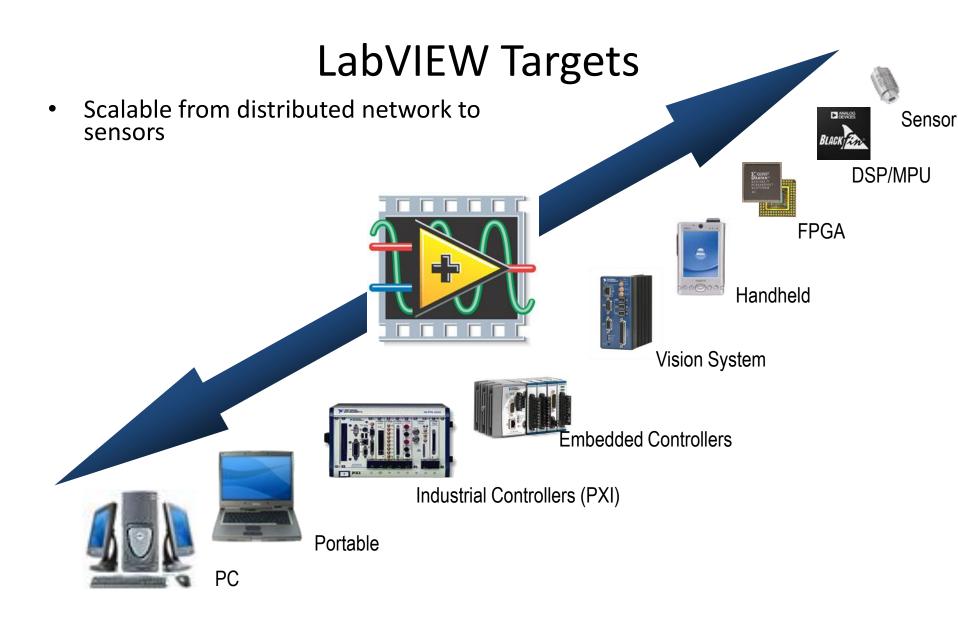

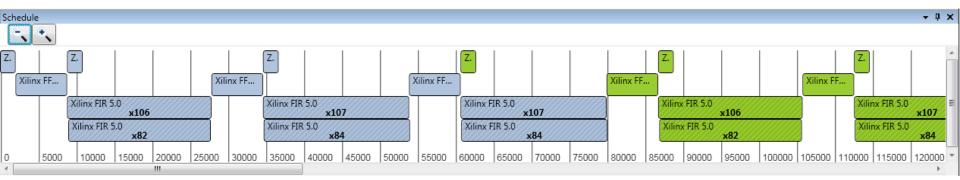

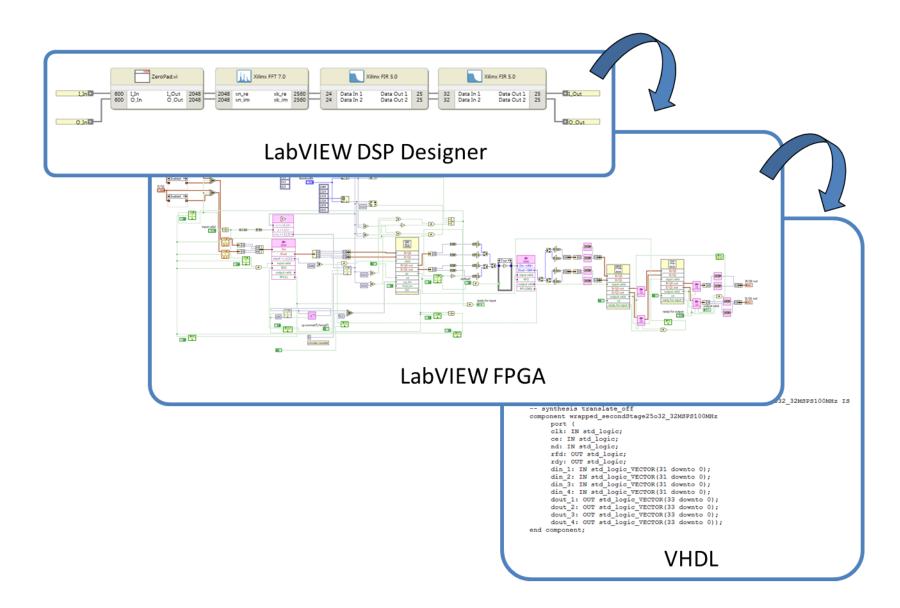

#### **DSP** Designer

- Development environment for creating streaming highperformance RF and DSP applications for FPGA targets

- Driving applications

- Spectral analysis, signal intelligence, software radios

- Platforms

- Heterogeneous FPGA platforms (R-series, FlexRIO)

- Target users

- RF and DSP domain experts

# Modeling System-Level Designs

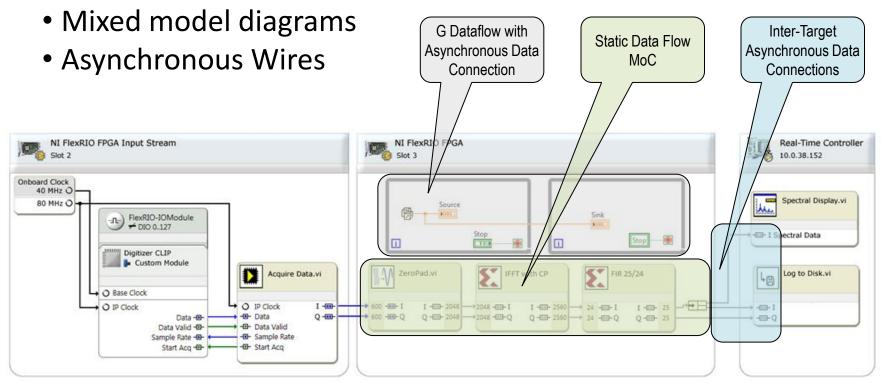

New modeling constructs

- Systems

- Targets

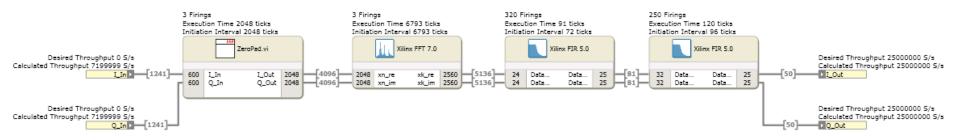

Calculated Schedule View

### Value of DSP Designer

#### **RF** Design Flow

### Outline

- DSP Designer framework

- Models, analysis, and exploration

- Deployment challenges

- Directions ahead

#### **DSP Designer Focus Areas**

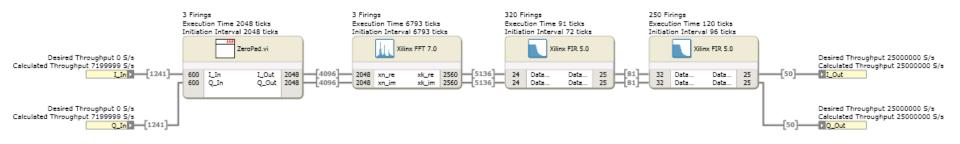

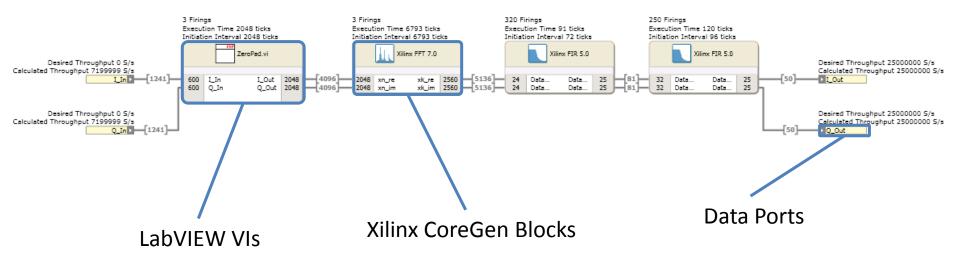

- DSP Diagram model of computation

- Analysis and optimization back end

- Performance models and timing library

- Actor definition

- IP modeling and integration

- Simulation and verification

- Code generation and implementation

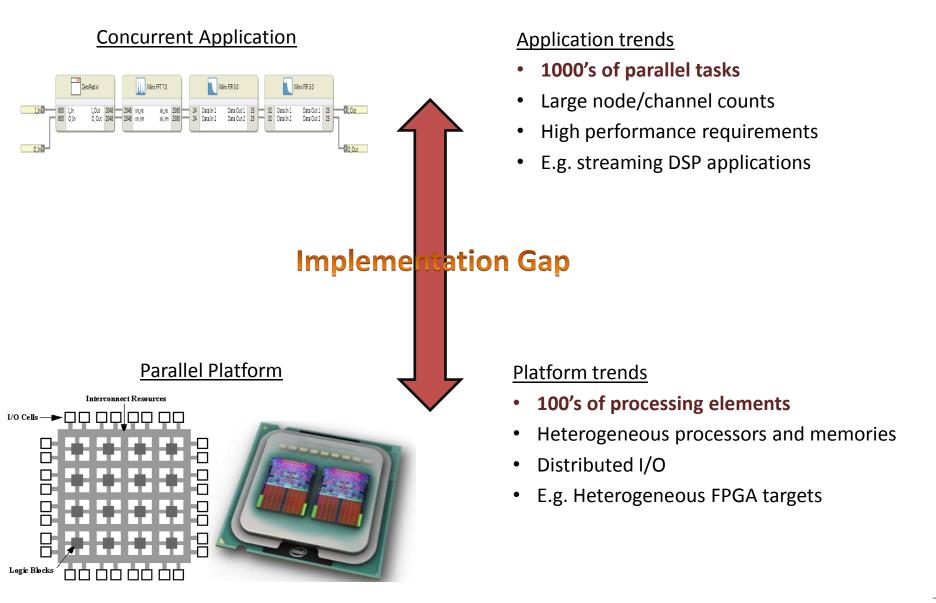

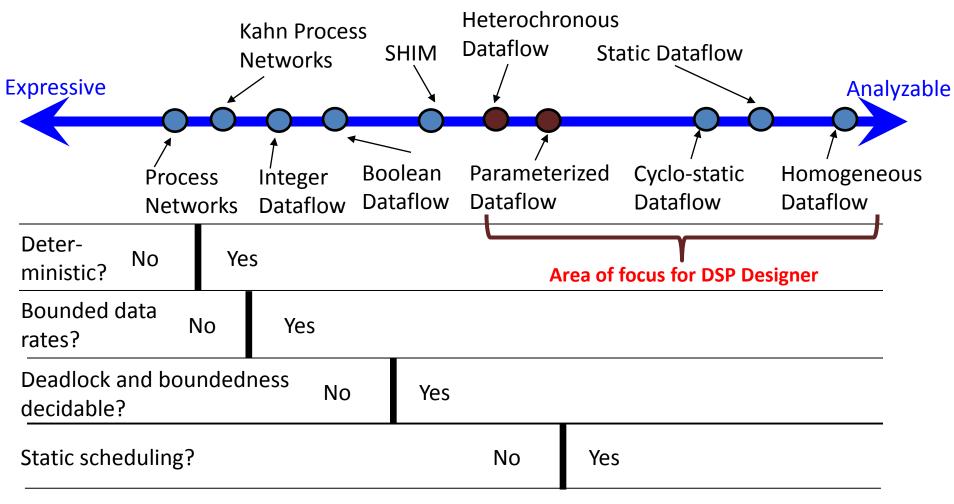

### MoCs for Streaming Applications

Key trade-off: Analyzability vs. Expressibility

[1] Edward A. Lee, "Concurrent Models of Computation for Heterogeneous Software", EECS 290, 2004.

[2] Stephen Edwards, "SHIM: A Deterministic Model for Heterogeneous Embedded Systems", UCB EECS Seminar, 2006. 19

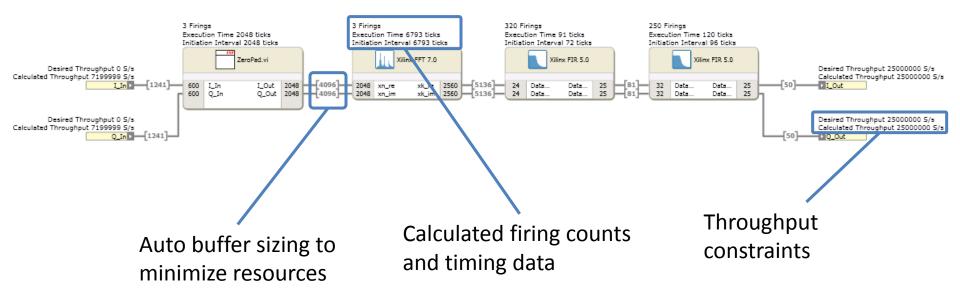

### Analysis and Optimization Features

- Core dataflow optimizations

- Model validation (deadlock and unboundedness detection)

- Throughput and latency computation

- Buffer size optimization (under throughput constraints)

- Schedule computation

- Hardware specific optimizations

- Resource constrained schedule computation

- Retiming and fusion

- Rate matching

- IP interface synthesis

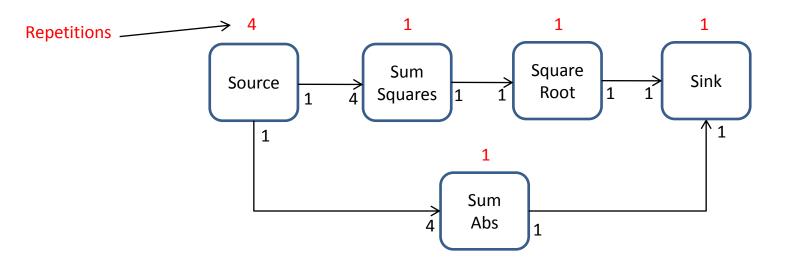

#### **Model Validation**

Analysis determines at compile time that this application executes in bounded memory and is deadlock free

#### **Buffer Size Optimization**

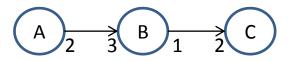

#### Example SDF Graph

Repetitions vector: (3, 2, 1)

#### **Problem Assumptions**

- Execution times: (A,1), (B,2), (C,2)

- No resource constraints

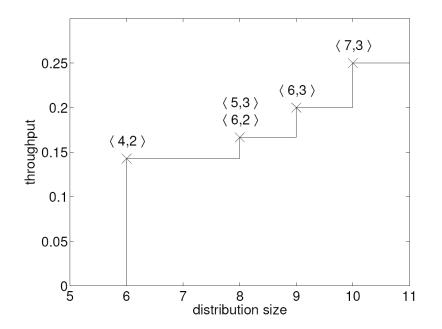

#### Pareto Space of Throughput and Buffer Sizes

Exploration results in a Pareto space of throughput and buffer sizes

[1] S. Stuijk, M.C.W. Geilen and T. Basten, "Exploring Trade-Offs in Buffer Requirements and Throughput Constraints for Synchronous Dataflow Graphs", DAC 2006

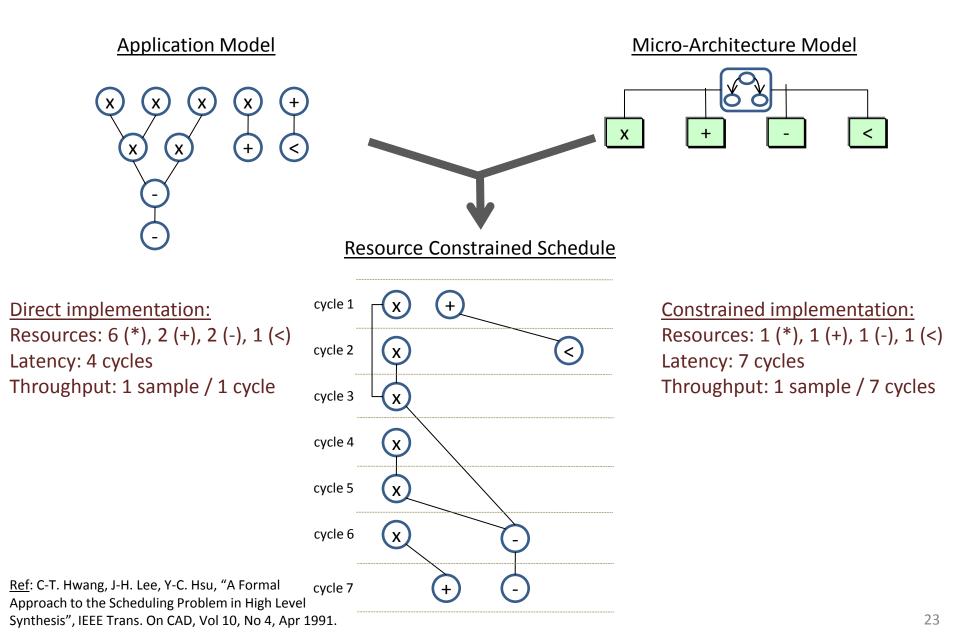

#### **Resource Constrained Scheduling**

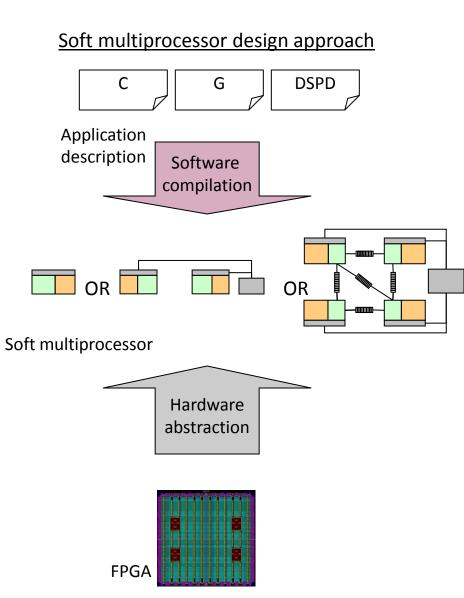

### FPGA Based Soft Multiprocessor Systems

- Designer customizes multiprocessor architecture

- Number of processors

- Interconnection network

- Custom co-processors

- Advantages

- FPGA becomes accessible to software developers

- Software compilation faster than hardware synthesis

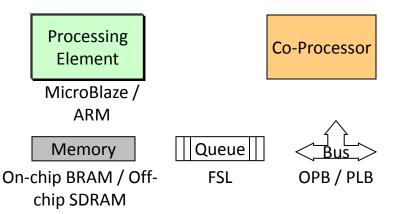

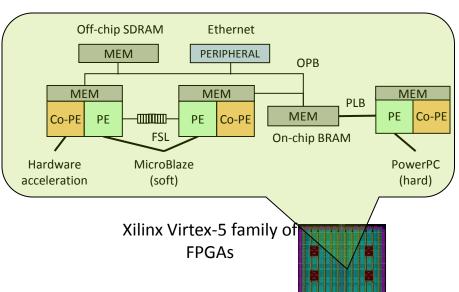

#### Architecture Building Blocks for Xilinx FPGAs

#### Multiprocessor Configuration

#### Designing Soft Multiprocessor Systems on FPGAs

- Modern FPGAs provide the capacity to build a variety of micro-architectures

- 50 processors growing with Moore's law

- Complex memory hierarchy

- Heterogeneous interconnection schemes

- Custom co-processors for critical operations

Given a target application(s): What is the best multiprocessor microarchitecture on the FPGA?

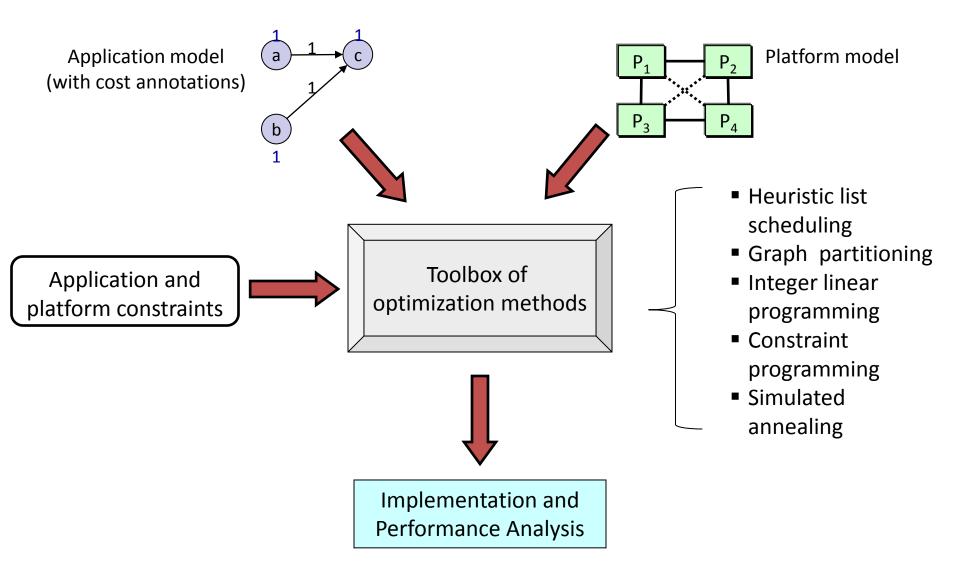

#### **Optimization Toolbox**

### Outline

- DSP Designer framework

- Models, analysis, and exploration

- Deployment challenges

- Directions ahead

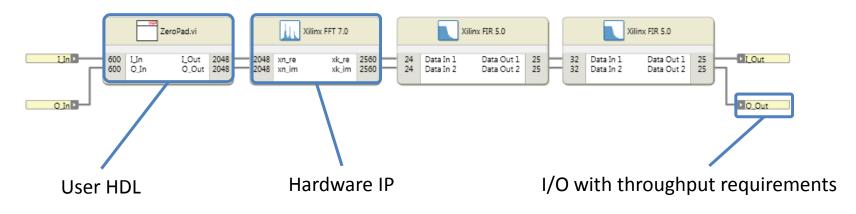

#### **IP** Integration

#### Streaming Model of the OFDMA Transmitter

<u>Design Challenge</u>: Generate a viable implementation of the OFDMA transmitter on a Xilinx Virtex-5 FPGA that meets correctness and performance requirements

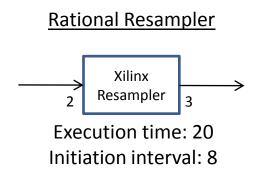

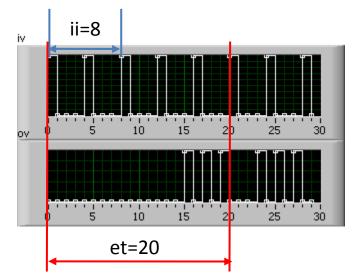

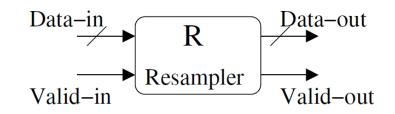

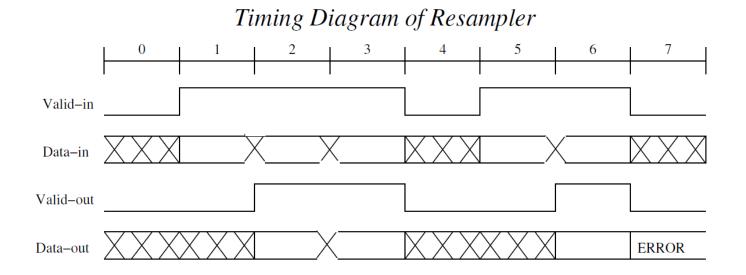

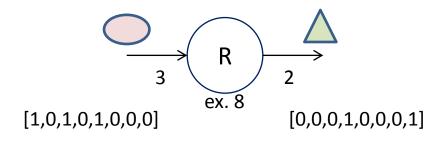

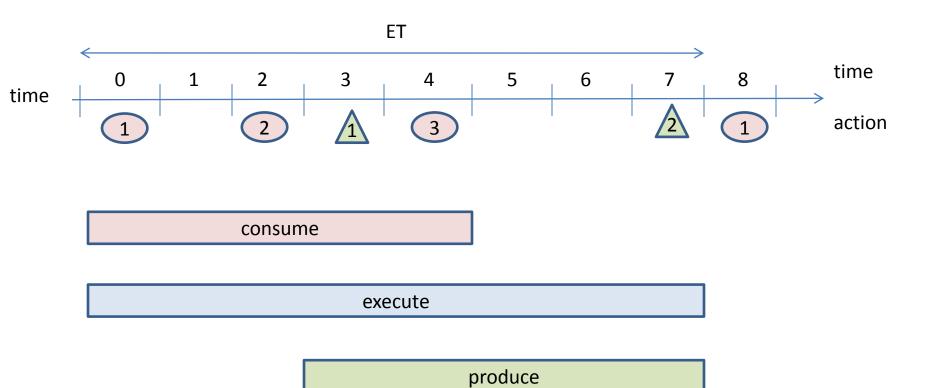

# **Timing Models for IP Blocks**

- <u>Execution time</u>: time to complete one firing, i.e. read 2 samples and produce 3 samples

- <u>Initiation interval</u>: minimum time between start of successive firings

[1] Xilinx Inc., Datasheet for CoreGen Resampler block.

| ~ Filter Specification              |                  |                                 |

|-------------------------------------|------------------|---------------------------------|

| Filter Type :                       | Interpolation    |                                 |

| Rate Change Type :                  | Fixed Fractional |                                 |

| Interpolation Rate Value :          | 3                | Range: 3512                     |

| Decimation Rate Value :             | 2                | Range: 22                       |

| Zero Pack Factor :                  | 1                | Range: 11                       |

| Number of Channels :                | 1                | Range: 164                      |

| Hardware Oversampling Specification |                  |                                 |

| Select format :                     | Sample Pe        | riod                            |

| Input Sampling Frequency :          | 0.001            | Range: 0.000001275.0 MHz        |

| Clock Frequency :                   | 300.0            | Range: 0.002550.0 MHz           |

| Input Sample Period :               | 4                | Range: 2.,10000000 Clock cycles |

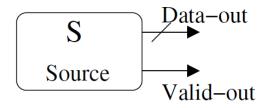

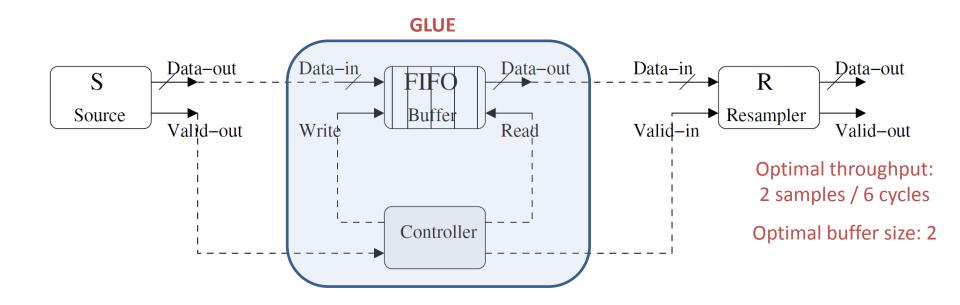

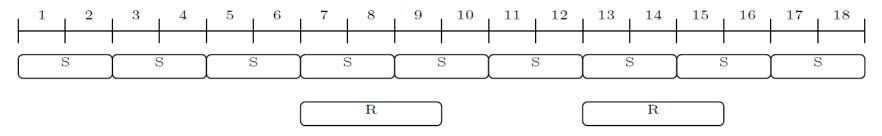

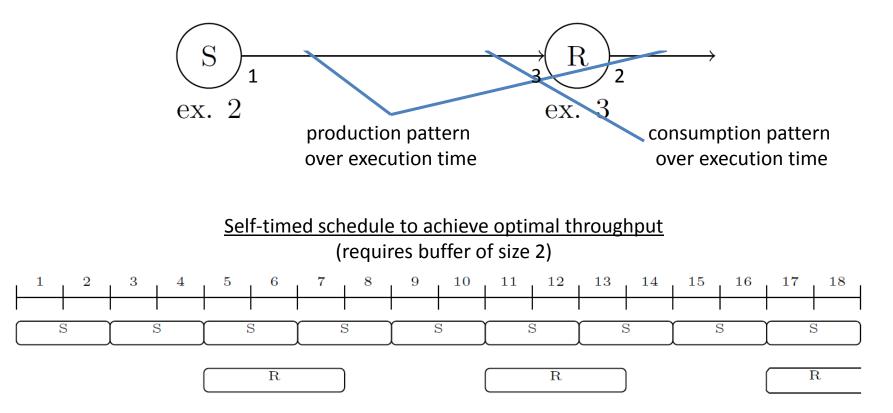

#### Example: Source-Resampler System

S outputs 1 sample every 2 cycles

R reads 3 inputs samples in consecutive cycles and outputs 2 samples in the 2<sup>nd</sup> and 3<sup>rd</sup> cycles

<u>Objective</u>: Create a valid composition of these blocks so that behavior and timing constraints are respected

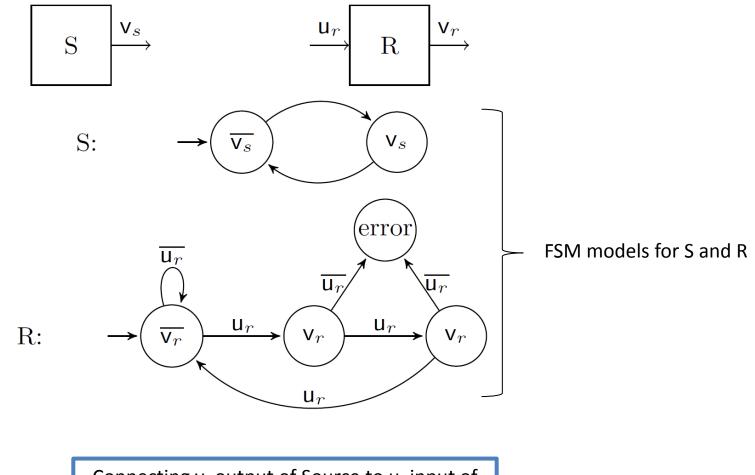

#### Source-Resampler: Interface Signals

Connecting  $v_s$  output of Source to  $u_r$  input of Resampler results in an invalid composition

#### Source-Resampler: System Implementation

<u>Glue design problem</u>: Given a set of actors, synthesize a glue (buffers and controllers), such that the resulting system satisfies correctness and performance properties

### Solutions to the Glue Design Problem

- Solutions at the HDL and FSM level

- Suffer state space explosion problem

- Infeasible for most practical systems

- Solutions based on abstract models

- Enable efficient static analysis

- Support automated synthesis

- But important to choose the right abstractions that yield <u>correct</u> and <u>non-defensive</u> implementations

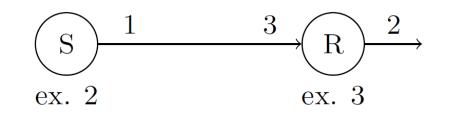

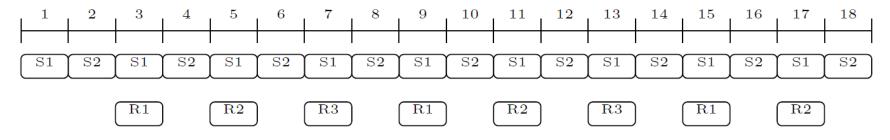

#### Source-Resampler: Static Dataflow Model

Self-timed schedule to achieve optimal throughput

(requires buffer of size 5)

Limitations of the SDF model:

- Does not capture how tokens are accessed

- Analysis conservatively allocates space for tokens from firings of S that occur while R executes

- Resulting implementation is <u>defensive</u>

[1] E. A. Lee and D. Messerschmitt, "Synchronous Dataflow", in Proc. of the IEEE, 75(9), 1987.

[2] S. Stuijk, M.C.W. Geilen and T. Basten, "Exploring Trade-Offs in Buffer Requirements and Throughput Constraints for Synchronous Dataflow Graphs", DAC 2006

#### Cyclo-Static Dataflow Model

Self-timed schedule to achieve optimal throughput

(requires buffer of size 1)

Limitations of the CSDF model:

- Does not capture requirement that Resampler IP must receive 3 tokens in consecutive cycles

- Analysis underestimates space needed for the buffer

- Resulting implementation is incorrect

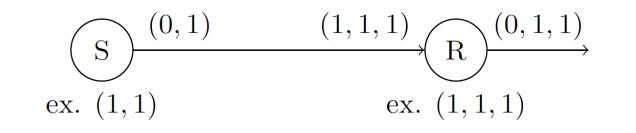

#### Static Dataflow Model with Access Patterns

Strengths of the SDF-AP model:

- Explicitly specifies how tokens are consumed and produced in time

- Analysis yields a buffer of size 2

- Resulting implementation is <u>correct</u> and <u>non-defensive</u>

#### Access Pattern Example

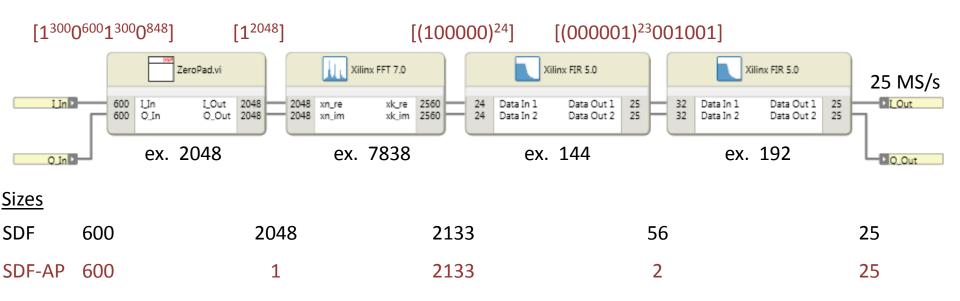

### Case Study: OFDMA Transmitter

Glue design using SDF-AP models

•

- Improves buffer sizes compared to SDF

- Results in a non-defensive controller implementation

### Outline

- DSP Designer framework

- Models, analysis, and exploration

- Deployment challenges

- Directions ahead

#### **Directions Ahead**

- Model and analysis extensions

- Efficient methods to check correctness and non-defensiveness

- Automatic characterization of access patterns

- Formalize relation between abstract and concrete models

- Specification for control and timing with dataflow

- Scenario aware, heterochronous, core-functional dataflow

- Parameterized models

- Other hardware specific problems

- Behavioral interface formalisms (IP-XACT)

- IP interface standardization

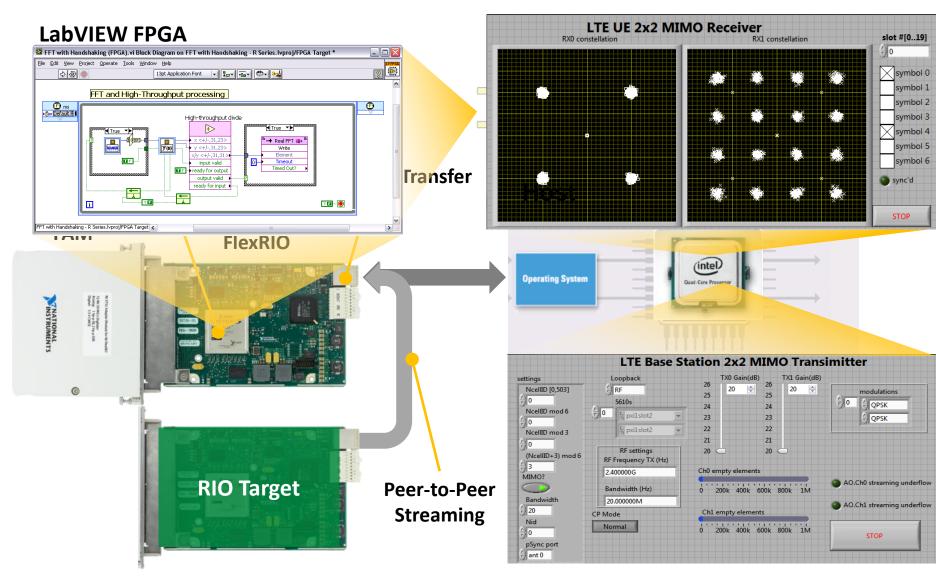

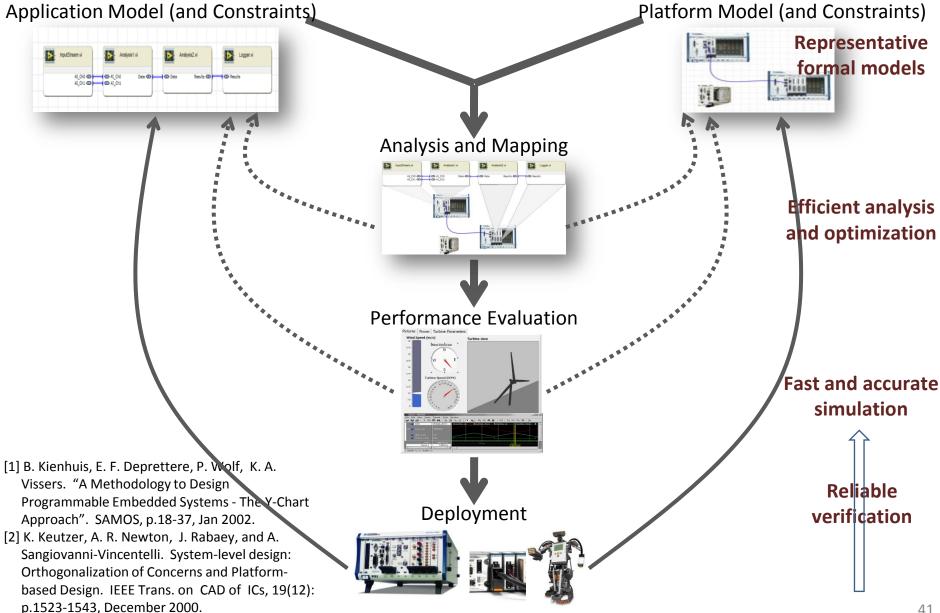

#### Y-Chart: A Disciplined System Design Methodology

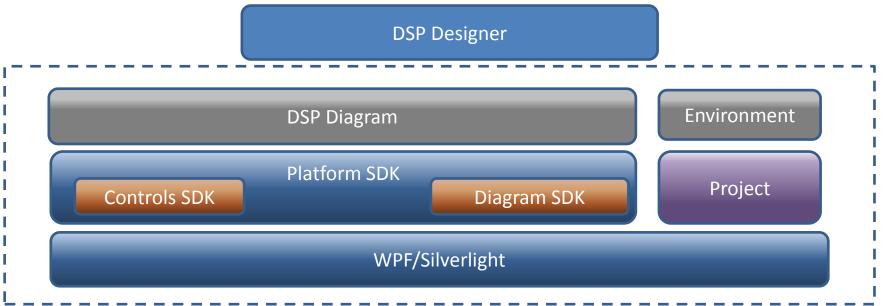

#### An Open API and Software Stack

- Create products for new problem spaces

- Leverage common infrastructure across products

- Scale implementations across platforms desktop OSs to web

- Improve developer efficiency in creating products

- Expect infrastructure to external partners to create products

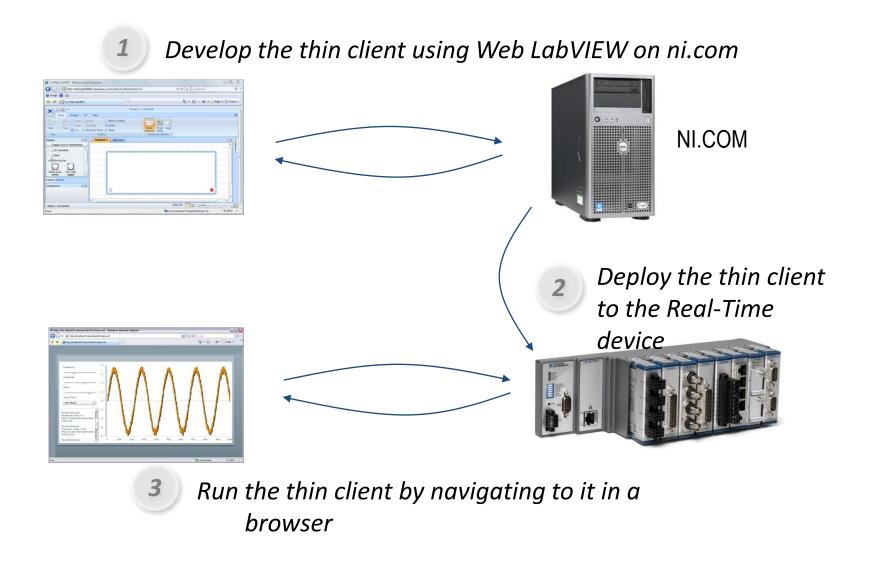

#### Web LabVIEW Development Process