#### SEVENTH FRAMEWORK PROGRAMME

# Challenge 3: Components, systems, engineering ICT-2007.3.3 Embedded systems design

Grant agreement for: Network of Excellence (NoE)

## Annex I - "Description of Work"

Project acronym: ArtistDesign

Project full title: ArtistDesign – Design for Embedded Systems

Grant agreement no.: 214373

Coordinating persons: Joseph Sifakis (Scientific Coordinator)

Bruno Bouyssounouse (Technical coordinator)

**UJF/VERIMAG Laboratory**

Date of preparation of Annex I: March 2nd, 2010

Date of approval of Annex I by Commission 29/3/2010

#### List of Beneficiaries:

UJF Filiale (France), Université Joseph Fourier Grenoble 1 (France), Rheinisch-Westfaelische Technische Hochschule Aachen (Germany), Aalborg Universitet (Denmark), Universidade de Aveiro (Portugal), Alma Mater Studorium - Universita di Bologna (Italy), Technische Universitaet Braunschweig (Germany), Universidad de Cantabria (Spain), Commissariat à l'Energie Atomique (France), Danmarks Tekniske Universitet (Denmark), Universitaet Dortmund (Germany), Ecole Polytechnique Fédérale de Lausanne (Switzerland), Embedded Systems Institute (Netherlands), Eidgenoessische Technische Hochschule Zuerich (Switzerland), Interuniversitair Micro-Electronica Centrum VZW (Belgium), Institut National de Recherche en Informatique et Automatique (France), Technische Universitaet Kaiserslautern (Germany), Kungliga Teknika Hogskolan (Sweden), Linköpings Universitet (Sweden), Lunds Universitet (Sweden), Maelardalens Hoegskola (Sweden), Offis E.V. (Germany), Project on Advanced Research of Architecture and Design of Electronic System (Italy), Universitaet Passau (Germany), Scuola Superiore di Studi Universitari e di Perfezionamento Sant'Anna (Italy), Instituto Superior de Engenharia do Porto (Portugal), Universitaet des Saarlandes (Germany), Universitaet Salzburg (Austria), Uppsala Universitet (Sweden), Technische Universitaet Wien (Austria), University of York (United-Kingdom), Institute of Science and Technology Austria (Austria), Faculdade de Engenharia da Universidade do Porto (Portugal), Universita degli studi di Trento (Italy)

Detailed table is available in section A.1.3.

## **Table of Contents**

| Part | ١                                            | 4                                     |

|------|----------------------------------------------|---------------------------------------|

| Α    | . Budget Breakdown and Projec                | et Summary4                           |

| 1    | Overall budget breakdown for the             | project 4                             |

| 1    | Proiect Summary                              | 5                                     |

| 1    |                                              | 6                                     |

|      |                                              |                                       |

| Part | )<br>                                        | 7                                     |

| В    |                                              | ress Beyond the State of the Art, S/T |

| 1.   | Concept and Project Objectives               | 7                                     |

| M    |                                              | 7                                     |

| M    | n Idea 2                                     | 9                                     |

| 1    | Progress beyond the State of the             | Art11                                 |

|      | •                                            | ded Systems Design11                  |

|      |                                              | gical Excellence through Integration  |

| 1.   | <u> </u>                                     | ystems Design 12                      |

| 1.   | 4. Long-term Integration                     | 14                                    |

| 1    | 3,                                           | Work Plan: Joint Programme of16       |

| 1.   | , ,                                          | on16                                  |

| 1.   |                                              | nponents21                            |

| 1.   | 3 Workpackage List / Overview                | 21                                    |

| 1.   | 4 Deliverables List                          | 22                                    |

| 1.   | 5 Workpackage Descriptions                   | 23                                    |

| 1.   | 6 Efforts for the Full Duration of the Proje | ect                                   |

| 1.   | 7 List of Milestones and Planning of Revi    | iews91                                |

| В    | Implementation                               | 93                                    |

| 2    | Management Structure and proce               | edures93                              |

| 2.   |                                              | 93                                    |

| 2.   | 2 Management Structure                       | 93                                    |

| 2    | Beneficiaries                                | 98                                    |

| 2.   |                                              | 98                                    |

| 2.   |                                              | 98                                    |

| 2.   |                                              | 100                                   |

| 2.   |                                              | 101                                   |

| 2.   | _                                            |                                       |

| 2.   | 6 Partner 6: Bologna                         |                                       |

| 2.2.7        | Partner 7: TUBS                                                               | 104        |

|--------------|-------------------------------------------------------------------------------|------------|

| 2.2.8        | Partner 8: Cantabria                                                          | 105        |

| 2.2.9        | Partner 9: CEA                                                                | 106        |

| 2.2.10       | Partner 10: DTU                                                               | 108        |

| 2.2.11       | Partner 11: Dortmund                                                          | 109        |

| 2.2.12       | Partner 12: EPFL                                                              | 110        |

| 2.2.13       | Partner 12: ESI                                                               | 111        |

| 2.2.14       | Partner 14: ETH Zurich                                                        | 112        |

| 2.2.15       | Partner 15: IMEC                                                              | 113        |

| 2.2.16       | Partner 16: INRIA                                                             | 114        |

| 2.2.17       | Partner 17: TUKL                                                              | 115        |

| 2.2.18       | Partner 18: KTH                                                               | 116        |

| 2.2.19       | Partner 19: Linkoping                                                         | 118        |

| 2.2.20       | Partner 20: ULund                                                             | 119        |

| 2.2.21       | Partner 21: MDH                                                               | 119        |

| 2.2.22       | Partner 22: OFFIS                                                             | 120        |

| 2.2.23       | Partner 23: PARADES                                                           | 121        |

| 2.2.24       | Partner 24: Passau                                                            | 123        |

| 2.2.25       | Partner 25: SSSA-Pisa                                                         | 124        |

| 2.2.26       | Partner 26: Porto                                                             | 125        |

| 2.2.27       | Partner 27: Saarland                                                          | 126        |

| 2.2.28       | Partner 28: PLU-Salzburg                                                      | 127        |

| 2.2.29       | Partner 29: Uppsala                                                           | 128        |

| 2.2.30       | Partner 30: Vienna                                                            | 129        |

| 2.2.31       | Partner 31: York                                                              | 131        |

| 2.2.32       | Partner 32: IST AUSTRIA                                                       | 132        |

| 2.2.33       | Partner 33: UNIV PORTO                                                        | 133        |

| 2.2.34       | Partner 34: TRENTO                                                            | 134        |

| 2.3          | Consortium as a whole                                                         | 136        |

| 2.4          | Resources to be Committed                                                     | 138        |

| B.3          | Impact                                                                        | 142        |

| 3.1          | Expected impacts listed in the work programme                                 | 142        |

| 3.1.1        | Workprogramme                                                                 |            |

| 3.1.2        | Durability and Long-Term Impact                                               |            |

|              |                                                                               |            |

|              | Spreading Excellence, Exploiting Results, Disseminating Knowledge             |            |

| 3.2.1        | Strengthening Excellence through Integration of Multidisciplinary Communities |            |

| 3.2.2        | Spreading Excellence Beyond the Network of Excellence                         | 145<br>145 |

| <b>1</b> 1 1 | CAUSIELO RESUNS INFORMI CONADORADON WITH INDUSTRY                             | 147        |

## Part A

## A.1. Budget Breakdown and Project Summary

## 1.1 Overall budget breakdown for the project

|                    |                | Estim     | ated Eligible |         |                |                 |

|--------------------|----------------|-----------|---------------|---------|----------------|-----------------|

|                    | Organisation   | RTD       | Mgt           | Other   |                | Requested       |

| Participant number | short<br>name  | (A)       | (B)           | (C)     | TOTAL<br>A+B+C | EC Contribution |

| 1                  | Floralis       | 140 657   | 246 000       | 258 689 | 645 346        | 575 017         |

| 2                  | UJF/Verimag    | 296 931   | 66 600        | 121 631 | 485 162        | 410 929         |

| 3                  | Aachen         | 119 179   |               | 0       | 119 179        | 89 383          |

| 4                  | Aalborg        | 199 440   |               | 10 079  | 209 519        | 159 658         |

| 5                  | Aveiro         | 68 627    |               | 2 400   | 71 027         | 53 870          |

| 6                  | Bologna        | 236 832   |               | 6 000   | 242 832        | 183 623         |

| 7                  | TUBS           | 126 008   |               | 3 920   | 129 928        | 98 425          |

| 8                  | Cantabria      | 135 320   |               | 0       | 135 320        | 101 489         |

| 9                  | CEA            | 99 808    |               | 5 500   | 105 308        | 80 356          |

| 10                 | DTU            | 243 784   |               | 13 500  | 257 284        | 196 337         |

| 11                 | Dortmund       | 281 216   |               | 14 100  | 295 316        | 225 011         |

| 12                 | EPFL           | 121 755   |               | 0       | 121 755        | 91 315          |

| 13                 | ESI            | 96 360    |               | 3 000   | 99 360         | 75 269          |

| 14                 | ETHZ           | 149 494   |               | 0       | 149 494        | 112 120         |

| 15                 | IMEC           | 267 378   |               | 1 500   | 268 878        | 202 033         |

| 16                 | INRIA          | 99 079    |               | 13 750  | 112 829        | 88 059          |

| 17                 | Kaiserslautern | 104 880   |               | 4 000   | 108 880        | 82 660          |

| 18                 | KTH            | 194 648   |               | 17 000  | 211 648        | 162 985         |

| 19                 | Linköping      | 117 776   |               | 0       | 117 776        | 88 331          |

| 20                 | Lund           | 98 396    |               | 3 450   | 101 846        | 77 247          |

| 21                 | Malardalen     | 155 758   |               | 4 000   | 159 758        | 120 818         |

| 22                 | OFFIS          | 75 592    |               | 0       | 75 592         | 56 694          |

| 23                 | Parades        | 21 200    |               | 1 976   | 23 176         | 12 576          |

| 24                 | Passau         | 87 459    |               | 0       | 87 459         | 65 594          |

| 25                 | Pisa           | 241 488   |               | 14 000  | 255 488        | 195 115         |

| 26                 | Porto          | 104 880   |               | 2 000   | 106 880        | 80 660          |

| 27                 | Saarland       | 182 211   |               | 0       | 182 211        | 136 658         |

| 28                 | Salzburg       | 68 640    |               | 22 555  | 91 195         | 74 035          |

| 29                 | Uppsala        | 133 408   |               | 0       | 133 408        | 100 055         |

| 30                 | Vienna         | 101 115   | 2 400         | 0       | 103 515        | 78 235          |

| 31                 | York           | 272 676   |               | 3 600   | 276 276        | 208 107         |

| 32                 | IST_Austria    | 78 036    |               | 4 000   | 82 036         | 62 527          |

| 33                 | UnivPorto      | 105 668   |               | 9 350   | 115 018        | 88 601          |

| 34                 | Trento         | 88 278    |               | 0       | 88 278         | 66 208          |

| TO                 | OTAL           | 4 913 977 | 315 000       | 540 000 | 5 768 980      | 4 500 000       |

#### 1.2 Project Summary

Proposal acronym: ArtistDesign

Proposal acronym and full title: ArtistDesign – Design for Embedded Systems

Strategic objectives addressed: Challenge 3: Components, systems, engineering

ICT-2007.3.3 Embedded systems design

The ArtistDesign NoE is the visible result of the ongoing integration of a community, that emerged through the ARTIST FP5 Accompanying Measure and that was organised through the ARTIST2 FP6 NoE.

The central objective for ArtistDesign is to build on existing structures and links forged in ARTIST2, to become a virtual Centre of Excellence in Embedded Systems Design. This is mainly achieved through tight integration between the central players of the European research community. Also, the consortium is smaller, and integrates several new partners. These teams have already established a long-term vision for embedded systems in Europe, which advances the emergence of Embedded Systems as a mature discipline.

ArtistDesign is one of the main focal points for dissemination in Embedded Systems Design, leveraging on well-established infrastructure and links, such as a web. It will extend its dissemination activities, including Education and Training, Industrial Applications, as well as International Collaboration. ArtistDesign will establish durable relationships with industry and SMEs in the area, especially through ARTEMISIA/ARTEMIS.

ArtistDesign will build on existing international visibility and recognition, to play a leading role in structuring the area.

The research effort aims to integrate topics, teams, and competencies, grouped into 4 Thematic Clusters: "Modelling and Validation", "Software Synthesis, Code Generation, and Timing Analysis", "Operating Systems and Networks", "Platforms and MPSoC". "Transversal Integration" covering both industrial applications and design issues aims for integration between clusters.

ArtistDesign has defined a four-year workprogramme, with a strong commitment to integration and sustainability. To achieve the aims, the estimated support from the EC is approximately 4.5 Million Euros. This support is a very small proportion of the overall investment by the core partners.

### 1.3 List of Beneficiaries

| Beneficiary number* | Beneficiary name                                                               | Beneficiary short name                          | Country            |

|---------------------|--------------------------------------------------------------------------------|-------------------------------------------------|--------------------|

| 1<br>Coordinator    | UJF FILIALE                                                                    | FLORALIS                                        | France             |

| 2                   | UNIVERSITE JOSEPH FOURIER GRENOBLE 1                                           | UJF/VERIMAG                                     | France             |

| 3                   | RHEINISCH-WESTFAELISCHE TECHNISCHE<br>HOCHSCHULE AACHEN                        | AACHEN                                          | Germany            |

| 4                   | AALBORG UNIVERSITET                                                            | AALBORG                                         | Denmark            |

| 5                   | UNIVERSIDADE DE AVEIRO                                                         | AVEIRO                                          | Portugal           |

| 6                   | ALMA MATER STUDORIUM - UNIVERSITA DI<br>BOLOGNA                                | BOLOGNA                                         | Italy              |

| 7                   | TECHNISCHE UNIVERSITAET BRAUNSCHWEIG                                           | TUBS                                            | Germany            |

| 8                   | UNIVERSIDAD DE CANTABRIA                                                       | CANTABRIA                                       | Spain              |

| 9                   | COMMISSARIAT À L'ENERGIE ATOMIQUE                                              | CEA                                             | France             |

| 10                  | DANMARKS TEKNISKE UNIVERSITET                                                  | DTU                                             | Denmark            |

| 11                  | UNIVERSITAET DORTMUND                                                          | DORTMUND                                        | Germany            |

| 12                  | ECOLE POLYTECHNIQUE FEDERALE DE<br>LAUSANNE                                    | EPFL                                            | Switzerland        |

| 13                  | EMBEDDED SYSTEMS INSTITUTE                                                     | ESI                                             | Netherlands        |

| 14                  | EIDGENOESSISCHE TECHNISCHE<br>HOCHSCHULE ZUERICH                               | ETH Zurich                                      | Switzerland        |

| 15                  | INTERUNIVERSITAIR MICRO-ELECTRONICA<br>CENTRUM VZW                             | IMEC                                            | Belgium            |

| 16                  | INSTITUT NATIONAL DE RECHERCHE EN INFORMATIQUE ET AUTOMATIQUE                  | INRIA                                           | France             |

| 17                  | TECHNISCHE UNIVERSITAET KAISERSLAUTERN                                         | TUKL                                            | Germany            |

| 18                  | KUNGLIGA TEKNIKA HOGSKOLAN                                                     | KTH                                             | Sweden             |

| 19                  | LINKÖPINGS UNIVERSITET                                                         | LINKOPING                                       | Sweden             |

| 20                  | LUNDS UNIVERSITET                                                              | ULUND                                           | Sweden             |

| 21                  | MAELARDALENS HOEGSKOLA                                                         | MDH                                             | Sweden             |

| 22                  | OFFIS E.V.                                                                     | OFFIS                                           | Germany            |

| 23                  | PROJECT FOR ADVANCED RESEARCH OF ARCHITECTURE AND DESIGN OF ELECTRONIC SYSTEMS | PARADES<br>(until Dec 31 <sup>st</sup><br>2008) | Italy              |

| 24                  | UNIVERSITAET PASSAU                                                            | PASSAU                                          | Germany            |

| 25                  | SCUOLA SUPERIORE DI STUDI UNIVERSITARI E<br>DI PERFEZIONAMENTO SANT'ANNA       | SSSA-PISA                                       | Italy              |

| 26                  | INSTITUTO SUPERIOR DE ENGENHARIA DO PORTO                                      | PORTO                                           | Portugal           |

| 27                  | UNIVERSITAET DES SAARLANDES                                                    | SAARLAND                                        | Germany            |

| 28                  | UNIVERSITAET SALZBURG                                                          | PLU-<br>SALZBURG                                | Austria            |

| 29                  | UPPSALA UNIVERSITET                                                            | UPPSALA                                         | Sweden             |

| 30                  | TECHNISCHE UNIVERSITAET WIEN                                                   | VIENNA                                          | Austria            |

| 31                  | UNIVERSITY OF YORK                                                             | YORK                                            | United-<br>Kingdom |

| 32                  | INSTITUTE OF SCIENCE AND TECHNOLOGY<br>AUSTRIA                                 | IST AUSTRIA                                     | Austria            |

| 33                  | FACULTADE DE ENGENHARIA DA<br>UNIVERSIDADE DO PORTO                            | UNIVPORTO                                       | Portugal           |

| 34                  | UNIVERSITA DEGLI STUDI DI TRENTO                                               | TRENTO                                          | Italy              |

## Part B

## B.1 Concept and Objectives, Progress Beyond the State of the Art, S/T Methodology and Work Plan

Objective: To build on previous integration, and become a virtual Centre of Excellence in Embedded Systems Design:

- Achieve tight integration between the central players of the European research community

- Establish durable relationships with industry and SMEs in the area, especially through ARTEMISIA/ARTEMIS

- Become the main focal point for dissemination, via ARTIST competencies and infrastructure

- Build on existing international visibility and recognition, to play a leading role in structuring the area.

#### 1.1 Concept and Project Objectives

#### Main Idea 1

Embedded systems are essential to ensuring a leading position for Europe in key industrial sectors services. This is well-recognized in the ICT FP7 priorities, and through the ARTEMIS ETP under construction.

#### **About Embedded Systems**

Embedded Systems are components integrating software and hardware jointly and specifically designed to provide given functionalities. These components may be used in many different types of applications, including transport (avionics, space, automotive, trains), electrical and electronic appliances (cameras, toys, television, washers, dryers, audio systems, and cellular phones), power distribution, and factory automation systems.

The extensive use of embedded systems and their integration in everyday products marks a significant evolution in information science and technology. An important requirement for their proliferation is seamless integration with their environment while respecting real-world constraints such as hard deadlines, reliability, availability, robustness, power consumption, and cost.

Embedded systems are deployed in the physical environment, and as such they have a continuous interaction with it. This gives rise to a number of specific characteristics, which play a role in structuring the technical domain, and for determining the relevant areas of research and industrial development:

#### **Economic Stakes for Europe**

Embedded systems are of strategic importance in modern economies. They are used in mass-market products and services, where value is created by supplying either functionality or quality. Functionality is defined as the service rendered to the user. Quality for a given functionality characterizes extra-functional properties of the product or service, such as performance, or dependability. For instance, a cellular phone offers functionality for mobile communication, while quality is characterized by audio fidelity, battery life, and durability.

Embedded technologies confer advantages to system and service developers, in generating added value and enhancing competitivity. The relative weight of software in the value of embedded systems is constantly increasing. Software allows new, complementary services, and differentiation, which brings competitive advantages.

Embedded technologies are the fastest growing sector in Information Technologies.

Europe currently has leading positions in sectors where embedded technologies are central to growth. These sectors currently include avionics, automotive, space, consumer electronics, smart cards, telecom devices, energy distribution, and railway transport. It is anticipated that they will also include distributed services such as e-Health and e-Banking.

In particular, Europe is well-positioned in avionics and space. In the automotive sector, European manufacturers and their suppliers enjoy a leading technological advantage for engine control, and emerging technologies such as brake by wire and drive by wire. Railway signalling in Europe relies on embedded systems, and allows faster, safer, and heavier traffic. Embedded technologies are extensively used to make energy distribution more flexible, especially in view of the coming market liberalization. Embedded technologies are strategic for the European telecommunication sector, which is also well-positioned. Finally, Europe is well-positioned for e-Services (e-Banking, e-Health, e-Training).

#### The FP6/FP7 Perspective - ARTEMIS

Embedded systems have already been one of the priorities in FP6. The European Commission, as well as the member states, is increasingly interested in reinforcing the R&D effort in this area. This is attested by:

- The launching of large R&D projects, focused on design and validation techniques in countries such as Sweden (Uppsala, Mälardalen) and Germany (AVACS, VeriSoft projekt);

- The creation of specialised research institutes, such as the Embedded Systems Institute in Eindhoven, the Centre for Embedded SW Systems in Aalborg;

- National Research Programmes on Embedded Systems, and in particular the creation of "competitivity poles", that federate the efforts of the main players in the area, at a regional level. Amongst these, 3 poles are strongly focused on embedded systems (Systematic, Aerospace Valley, Minalogic);

- Creation of Networks of Excellence (ARTIST2, HiPEAC, HyCon).

The ArtistDesign core partners have been actively involved in leading all these initiatives.

In FP7, several indicators show the clear willingness to make Embedded Systems a top priority for Europe. This is reflected by the significantly increased overall budget of the ICT programme. It is also confirmed by the creation of the ARTEMIS Joint Technology Initiative (JTI), set up to reinforce European R&D in embedded systems. ARTEMIS governance will involve representatives from 3 stakeholders: the European Commission, member states, as well as representatives from corporate industry, SMEs, and Public Research Organisations. These are organised within the ARTEMISIA association.

As the leading Network of Excellence focusing on design for embedded systems, ArtistDesign will have a close working relationship with ARTEMIS and ARTEMISIA. A liaison group composed of ArtistDesign members having responsibilities within ARTEMISIA has been set up to manage interaction. This will concern contributions to the ARTEMIS Strategic Research Agenda (SRA), and the Working Group on Innovation Environment.

Beyond the applied research and development activities driven by its industrial stakeholders, it is essential for the long-term success of ARTEMIS to have an environment supporting upstream research driven by the academic community in the large (universities and research institutes).

Leveraging on existing links between the ArtistDesign NoE leadership and ARTEMIS, ArtistDesign NoE will actively promote structuring within the academic community for effective and efficient interaction with industry via ARTEMISIA.

#### Main Idea 2

Embedded systems design is an emerging scientific discipline, mobilizing a large international community, around a set of fundamental challenging and multi-disciplinary problems. For this discipline to emerge, a considerable focused research effort by the best teams is needed.

#### **Current Scientific Foundations for Systems Design, and their Limitations**

**Design for Systems in General**: Systems design is the process of deriving, from requirements, a model from which a system can be generated more or less automatically. A model is an abstract representation of a system. For example, software design is the process of deriving a program that can be compiled; hardware design, the process of deriving a hardware description from which a circuit can be synthesized. In both domains, the design process usually mixes bottom-up and top-down activities: the reuse and adaptation of existing component models; and the successive refinement of architectural models in order to meet the given requirements.

Design for Embedded Systems: An embedded system is an engineering artefact involving computation that is subject to physical constraints. The physical constraints arise through two kinds of interactions of computational processes with the physical world: (1) reaction to a physical environment, and (2) execution on a physical platform. Accordingly, the two types of physical constraints are reaction constraints and execution constraints. Common reaction constraints specify deadlines, throughput, and jitter; they originate from the behavioural requirements of the system. Common execution constraints put bounds on available processor speeds, power, and hardware failure rates; they originate from the implementation requirements of the system. Reaction constraints are studied in control theory; execution constraints, in computer engineering. Gaining control of the interplay of computation with both kinds of constraints, so as to meet a given set of requirements, is the key to embedded systems design.

The design of embedded systems requires a holistic approach that integrates essential paradigms from hardware design, software design, and control theory in a consistent manner. We postulate that such a holistic approach cannot be simply an extension of hardware design, nor of software design, but must be based on a new foundation that subsumes techniques from both worlds. This is because current design theories and practices for hardware, and for software, are tailored towards the individual properties of these two domains; indeed, they often use abstractions that are diametrically opposed.

#### **Main Challenging Issues**

We need methods and tools for the cost-effective design of systems of guaranteed quality and performance. These should focus on the overall system as the combination of software and hardware interacting with its environment. A key issue is the joint design of both hardware and software to determine tradeoffs between cost and quality and performance.

Embedded systems design raises difficult, fundamental research problems which are at basis of an emerging theory that will bring together Informatics and Physics. Informatics is founded on models and theory that ignore physical time. Existing models and paradigms such as automata, algorithms, computability and complexity theory adopt an abstract "logical" view of time which is difficult to link to physical time. Existing theory does not provide a basis for predicting the dynamic behaviour of application software on a given platform.

We believe that the challenge of designing embedded systems offers a unique opportunity spanning the spectrum from theoretical foundations to engineering practice. To begin with, we need a mathematical basis for systems modelling and analysis which integrates both abstract-machine models and transfer-function models in order to deal with computation and physical constraints in a consistent, operative manner. Based on such a theory, it should be possible to combine practices for critical systems engineering to guarantee functional requirements, with best-effort systems engineering to optimize performance and robustness.

The theory, the methodologies, and the tools need to encompass heterogeneous execution and interaction mechanisms for the components of a system, and they need to provide abstractions that isolate the sub-problems in design that require human creativity from those that can be automated. This effort is a true grand challenge: it demands paradigmatic departures from the prevailing views on both hardware and software design, and it offers substantial rewards in terms of cost and quality of our future embedded infrastructure.

#### **Need for Critical Mass and Excellence**

Embedded Systems Design is a multi-disciplinary area. Its development requires integration of contributions from different topics, and thus critical mass. This is visible in large research centres in the USA, which play a leading role in the area. For example, the excellent position held by UC Berkeley on wireless sensor networks has been made possible by bringing together competencies in architectures, compilers, and telecommunication.

Given the hard problems to be addressed for the emergence of this discipline, it is essential to have, in addition to critical mass, the best possible teams from the contributing topics. Furthermore, the effort needs to be properly structured and motivated to succeed.

ArtistDesign gathers the right critical mass, with the best European teams. Furthermore, most of these teams have participated in ARTIST2, and have already built up momentum and shown their willingness and commitment to collaborate, around a coherent and ambitious workprogramme.

#### 1.2 Progress beyond the State of the Art

#### 1.2.1. Theory Methods and Tools for Embedded Systems Design

Design flow involves topics leading from initial requirements to a final implementation satisfying them. The objective is to study specific needs for these design activities, as well the possibility of integrating them in a coherent design flow.

We distinguish four essential topics, for which existing techniques should be adapted and extended

**Modelling and Validation:** Modelling is an essential activity in the design flow. For embedded systems, we need formal modelling techniques that take into account the characteristics of a system's external and execution environments. Furthermore, these techniques should support component-based construction for heterogeneous components to be applicable throughout the design process. For embedded systems, validation focuses on testing and verification of non functional properties, including performance and dependability.

**Software Synthesis, Code Generation and Timing Analysis**: These are interrelated topics, for which strong integration should be sought. The aim is to study and implement resource-aware synthesis and code generation techniques. These techniques allow the generation of an implementation meeting given user requirements from a functional description of an application (e.g. application software) and a model of a target platform. Timing analysis techniques are needed for building accurate platforms models, used by code generation tools. In particular, they provide estimates about the dynamic characteristics of the platforms e.g.; worst case or best case execution times.

**Real-Time Operating Systems Scheduling and Networks:** The aim is to develop theory methods and tools for new real-time software infrastructures, for the execution and communication between embedded applications. The main problems include adaptive resource management and dependability techniques, in particular to improve robustness to deviations from nominal conditions.

**Platforms and MPSoC Design**: The aim is implementation of complex applications on multicore HW platforms. It raises a number of problems for ensuring predictability and efficiency. These include adaptive techniques for resource management, and the study of reliable programming models for multi-core architectures.

Integrating these results in a coherent design flow is the main scientific and technical objective of the ArtistDesign NoE. This integration will be achieved for design flows ensuring given essential properties such as adaptivity, predictability, dependability, etc. In a specific Workpackage, for each of these properties, we will examine how to combine results in the topics above. Additionally, validation of this integration work will be guided by comparison and analysis of design flows in automotive, multi-media, healthcare, applications.

## 1.2.2. Strengthening Scientific and Technological Excellence through Integration

Through the integration of high-quality scientific teams, achieve the emergence of embedded systems design as a discipline, and the corresponding structured scientific community.

ArtistDesign will integrate the European research community in embedded systems design by implementing a long-term research vision for embedded systems in Europe.

The ambition is to compete on the same level as equivalent centres in the USA (Berkeley, Stanford, MIT, Carnegie Mellon), for both the production and transfer of knowledge and competencies, and for the impact on industrial innovation. ArtistDesign will create a research pipeline with continuous production of top research results. It will proactively invest in research groups to ensure competitivity at an international level.

This objective is achieved by integration around a Joint Programme of Activities, aiming to create critical mass from selected European teams.

The partners' international standing, research and teaching programmes in the field, the technologies they have developed and possess, and their leading presence in international scientific events prove their excellence. The Joint Programme of Activities will integrate the partner institutions mainly by promoting close collaboration and massive researcher exchanges between partners and thus start an "ARTIST culture" within the network.

The long-term ambition is the emergence of Embedded Systems Design as a mature discipline through research projects, integration of communities, education.

#### 1.2.3. Spreading Excellence in Embedded Systems Design

The NoE's influence is greatly expanded through its affiliated partners, who actively participate in the technical work and act as a relay to the greater Embedded Systems Design community. We expect that more affiliated partners will join the project and that the NoE's impacts will continue to grow with time. With this number of excellent people working on the same goals, the visibility of the European research effort in embedded systems design is worldwide. This will progressively create a European embedded systems design community, and spread the "ARTIST culture" in all major research institutions.

To ensure that the next generation of researchers will continue in this direction, ArtistDesign will devote a great deal of effort to spreading our knowledge in education and training. We will establish a vision for Education and Training in embedded systems by promoting reference curricula and training for industrial engineers.

Activities such as joint PhDs between partners, courseware, textbook publications, summer schools, and seminars, will all serve to attract students and young researchers to our research field.

A specific effort is devoted to spreading excellence to industry. All the core partners have strong and lasting collaborations with major industrial players in the area. It is vital for the partners to see the industrial know-how and techniques evolve, through the integration of state of the art results. Concretely, this transfer to industry is through shared PhDs with affiliated industrial partners, by opening the NoE's platforms to industry, and through a strong participation of the partners in Integrated Projects, STREPS, etc. It is worth noting the degree of collaboration between ArtistDesign partners for building Integrated Projects in the area (e.g.: SPEEDS, DECOS, ASSERT, SHAPES).

ArtistDesign will actively work to promote and enable the transfer of partners' results through participation in industrial projects, and training (schools, on-site, etc.). We will represent and promote the highest level of research competence and provide a network that taps into the highest levels of competence. The NoE will analyze and communicate industrial needs to research.

Finally, through the key participation of core partners in ARTEMIS/ARTEMISIA, the NoE will actively contribute to maintaining strong links between Public Research Organisations and Corporate Industry, and SMEs in the area.

ArtistDesign will build up and reinforce existing links between the European embedded systems design community and main international (outside Europe) players in the area. Through the International Collaboration activities in ARTIST FP5 and the ARTIST2 NoE, we have set up regular activities such as:

- High-level meetings (e.g.: in collaboration with the NSF) that gather together international experts from industry and academia to analyse the state of the art and identify promising work directions.

- International workshops on top-priority topics, such as timing analysis, and component-based design, as well as workshops on education.

- International schools in China, and South America, to promote European research results in emerging economies and reinforce our visibility as well as to draw top students.

ArtistDesign will continue to organize these types of events, to reinforce international visibility and recognition. We will go a step further, to develop an International Collaboration programme in embedded systems, involving the main non-European centres of excellence in embedded systems design.

The ArtistDesign NoE will extend the portal initiated in ARTIST2, by adding services for interaction with the embedded systems community in the large. It will act as a repository of knowledge in the area, including courseware, information about standards, methods and tools, research publications and results. This web portal is made available within the NoE core and affiliated partners, and also to other parties according to modalities to be defined.

This repository will be the reference for the embedded systems design community. It will build on the existing ARTIST2 Portal, and offer information about workshops, conferences, schools and seminars, international collaboration, publications, course materials available online, etc..

As was done at the start of ARTIST2, ArtistDesign will hold a press conference to announce the start of the NoE. This is described in further detail in section B.1.3.5 "WP2 Description – JPASE".

#### 1.2.4. Long-term Integration

This section provides the global Indicators for Integration, expressed as high-level objectives, which will deeply and qualitatively change the degree of integration between academic entities in the area.

Embedded systems design is a multidisciplinary area requiring competences from hardware engineering, operating systems and networks, programming and compilation, modelling and software engineering, control engineering. The ArtistDesign NoE gathers together leading European teams from all these areas.

This durable integration is also visible through an organised community that has a concerted action for structuring the area, through joint workshops, conferences, schools and publications.

ArtistDesign will continue and extend these activities, both quantitatively and qualitatively. In setting up the consortium, we have sought the right balance between critical mass, excellence, and commitment from the core partners.

#### Critical Mass

It was essential to gather a sufficient number of partners, to achieve a fair coverage of the main topics in the area, as well as to have the capacity to impact the European research landscape. Nonetheless, to ensure efficiency, we have limited the number of core partners, based on previous experience. At the same time, our impact is amplified through the large number of affiliated academic, SME, industrial and international collaboration partners.

#### Excellence

The ArtistDesign core partners include the main European leading teams, as attested by their leadership in their respective areas, as well as their strong involvement in national and European projects and initiatives.

#### Commitment

The majority of the ArtistDesign core partners were already involved as core partners in the ARTIST2 NoE. They have demonstrated a high degree of investment to achieve the workprogramme objectives, by committing the resources needed, which are an order of magnitude larger than those provided by the NoE financing. We estimate that the effort for implementing the JPA is roughly 10 times the financial contribution for integration.

The momentum and willingness of the consortium to continue working together are very strong. This is a good indication that integration will be sustained even after the end of the contract. ArtistDesign will leverage on the initial results of the ARTIST2 NoE, to achieve a durable structuring effect on European research in a variety of respects:

- 1. The NoE will extend the *integration of academic research*. Clustering around an emerging coherent theoretical embedded systems design framework contributes to the unification of the scientific community. This unification is reinforced through measures for overcoming the inherent contextual, cultural, and disciplinary diversity through implementation of the JPA (schools, joint workshops, etc.).

- 2. We intend to work towards integration between the recently funded IST STREP projects, that have a strong level of ARTIST involvement and leadership:

- ACTORS Adaptivity and Control of Resources in Embedded Systems

- ALL-TIMES Integrating European Timing Analysis Technology

- COMBEST COMponent-Based Embedded Systems design Techniques

- PREDATOR Design for Predictability and Efficiency

- Quasimodo Quantitative System Properties in Model-Driven Design of Embedded Systems.

- MNEMEE

- EMUCO Embedded Multi-Core

- JEOPARD Java Environment for Parallel Realtime Development

- 3. ArtistDesign will impact *R&D* activities from an organizational perspective. The NoE will explicitly aim to create a context, an infrastructure and a culture for embedded systems design. This is achieved via the JPA activities, and also by the growing community spirit generated.

- More specifically, to ensure a durable structuring, and coordination of the embedded systems design community, the NoE actively works in the following directions:

- ➤ Exploitation and improvement of the existing Web Portal and Intranet for disseminating information and coordination R&D activities.

- ➤ Continue efforts to reinforce the Embedded Systems Week, and to place embedded systems design at the heart of the DATE conference. We will pursue interaction with scientific organizations in the area (e.g.: ACM, IEEE, Euromicro, DATE), to further structure the scientific event landscape.

- Work and interaction with and within ARTEMIS/ARTEMISIA is pursued, to ensure tight interaction between the academic and industrial components of the embedded systems design community.

- A very promising perspective we are currently investigating is in setting up a European Institute of Technology (EIT), on Embedded Systems. Funding for EITs is planned within IST FP7. Our community is well-positioned for this, in terms of credibility, critical mass, excellence and organizational infrastructures. Naturally, competition for these funds is fierce. Nonetheless, we are convinced that, if Embedded Systems are selected for funding, that our community will be at the heart of an EIT on this topic.

- ➤ To ensure the sustainability of the community beyond the ArtistDesign funding period, it is important to set up a lasting coordination structure. A solution to be explored would be through a specific ARTEMISIA Working Group.

As a fallback solution, we could alternately set up the *ArtistInstitute* as a non-profit organization. In complement to coordinating the community, it would provide interaction and collaboration with the European large companies and SMEs in Embedded Systems, leveraging on its network of top European researchers.

- 4. ArtistDesign will have structural impact on European education in Embedded Systems Design, by:

- Integrating state of the art knowledge into the curricula, and accelerating the convergence towards unified multi-disciplinary approaches.

- Promoting approaches, techniques, which are well-adapted to meeting current and future industrial needs.

## 1.3 S/T Methodology and Associated Work Plan: Joint Programme of Activities (JPA)

#### 1.3.1 Overall Strategy and General Description

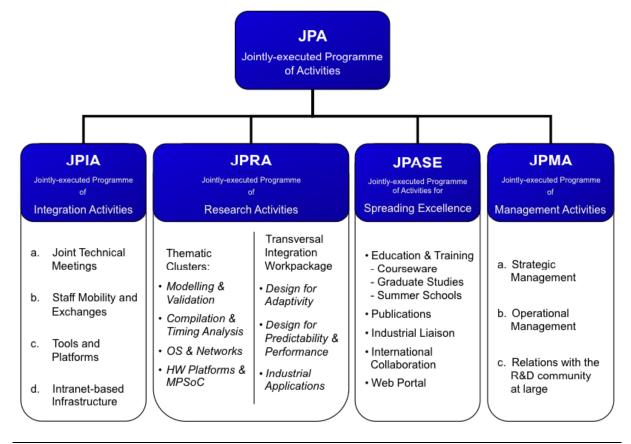

We present an overview of the JPA breakdown, and the way in which the different types of Activities cooperate to achieve the overall objective.

#### Overview

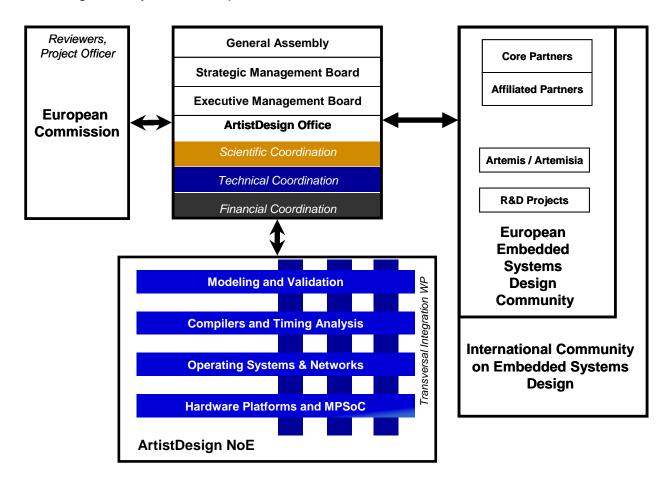

ArtistDesign will act as a *Virtual Centre of Excellence*, composed of a set of virtual teams, called *clusters*. Each cluster gathers together selected teams from partners, to create the critical mass and expertise in one of the essential topics for embedded systems design.

Each cluster acts as a scientific team, with a specific workplan, and it also participates in global Integration activities, as specified in the *Joint Programme of Activities* (JPA). Each cluster has one or more scientific leaders, who lead the team and coordinate the effort.

A founding principle of the ArtistDesign NoE is integration around a common set of essential research topics, which may evolve over the lifetime of the NoE. This concept was initiated in the ARTIST2 NoE, and refined in ArtistDesign.

An essential new structural feature is the Transversal Integration workpackage having far greater independence (separate leaders and independent budget). We expect this to lead to continued integration between the topics.

Each cluster has affiliated partners, serving as relays to the community. These affiliated partners, as well as external parties sharing ArtistDesign's objectives may receive funding and participate in the ArtistDesign Activities according to rules to be defined.

The Joint Programme of Activities is structured as follows:

To enhance the readability of the proposal, we have preserved this structure (and the corresponding reference numbers) wherever possible throughout the document. This diagram can be used as a reference to understand the relative positions between the different Activities.

All the Activities are monitored to check their relative success or failure. Evaluation will rely on internal mechanisms. The overall success criteria for the NoE is the emergence of a European scientific community on embedded systems design, with strong interaction with industry, and internationally recognized excellence.

All the activities are open to the ArtistDesign Affiliated partners. These are not core partners in the consortium, but receive support for travelling to ArtistDesign meetings, and actively contribute to the implementation of the Joint Programme of Activities (JPA). These affiliated partners include industrial, SME, academic, and international affiliates. We will continue to apply the ARTIST2 procedure for joining ArtistDesign as affiliated partners, described here: <a href="http://www.artist-embedded.org/artist/Becoming-an-Affiliated-Partner.html">http://www.artist-embedded.org/artist/Becoming-an-Affiliated-Partner.html</a>

The breakdown for the Jointly-executed Programme of Activities (JPA) is the following:

#### Jointly-executed Programme of Management Activities (JPMA)

In order to ensure correct integration and coordination of activities, and coordination between the partners, the Consortium will carry out a Joint Programme of Management Activities (JPMA). It includes:

#### Strategic Management

The Strategic Management Board (SMB) plays a key role in ensuring ongoing integration at 3 levels: I) within the cluster; II) between clusters; III) with the larger European Embedded Systems Design community.

#### Operational Management

is ensured by the ArtistDesign Office, and the Executive Management Board (composed of the Cluster Leaders). The ArtistDesign Office ensures that all aspects of the NoE are running smoothly, and that progress is made towards the overall NoE objectives. It is composed of the Scientific Coordinator, the Technical Coordinator, and the Legal, Administrative and Financial Coordinator.

#### Relations with the R&D community at large

The NoE has a very strong presence within the embedded systems design community, at all levels. High-level interaction with the main institutions and bodies such as ARTEMIS/ARTEMISIA, professional organisations such as ACM TECS, NSF, DARPA, large conferences, are ensured and supported by various members of the Strategic Management Board, and the Scientific and Technical Coordinators.

#### Jointly-executed Programme of Integrating Activities (JPIA)

Each ArtistDesign research activity will have work within both the JPIA and the JPRA workpackages. The JPIA Activities are carried out on a global, NoE level, transcending the clusters. They form the supporting background for integration of the NoE, and are executed in phase and in interplay with the JPRA research activities. For instance, funds for staff mobility are allocated taking into account the needs for research.

The activities listed here will promote integration of geographically dispersed teams. All these activities will have long-lasting effects, well beyond the duration of the initial EC funding.

These activities include Joint Technical Meetings, Staff Mobility and Exchanges, Tools and Platforms, and an Intranet-based Infrastructure for Communication and Collaboration.

#### Joint Technical Meetings

Joint Technical meetings aim to present, discuss and integrate the ongoing work, and exchange points of view with other teams. They also serve to identify future work directions.

#### Staff Mobility and Exchanges

This is essential for integration within the NoE, including mobility of students and/or researchers, between core teams, or between core teams and affiliated teams. Mobility should be justified by and refer to involvement in an activity from the JPRA or JPIA, or one of the following: co-funded scholarships with industry; exchange of students and personnel within the consortium.

These measures are indicative – ArtistDesign will take the appropriate steps and incentives to ensure integration through mobility.

#### Tools and Platforms

A research platform is composed of competencies, resources, and tools targeting specific technical and scientific objectives around a chosen topic. These are at the state-of-the-art, and are made available to the R&D community for experimentation, demonstration, evaluation, and teaching.

The research platforms, tools and facilities are an essential tool for implementing the JPIA. They will lay the groundwork for the JPRA, allowing common research to occur and capitalisation on research results. Platforms are used as the basis for transfer of research results to industry. They allow teaching practical knowledge of the concepts and techniques.

ArtistDesign platforms are not defined from scratch – they integrate the results of long-term efforts, and are meant to be durable, evolving with the state of the art. The partners are committed to durability, and have invested significant resources into their development. The construction of ArtistDesign has provided the opportunity to assemble existing pieces into a rationally-structured set of platforms, covering the area of embedded systems design.

Some of the ArtistDesign platforms have international visibility, and the ambition is for these to serve as world-wide references in their respective topics.

Joint Management of the Knowledge Portfolio:

We believe that ArtistDesign has an enormous potential in Tools and Platforms. We will set up a repository for managing and disseminating the participating team's IPR, including tools, software and hardware IPs. This repository is used for dissemination purposes, as well as for marketing the partner's achievements. These dissemination efforts is completed through technical meetings and presentations.

#### • Intranet-based Infrastructure for Communication and Collaboration

To overcome the physical, cultural, and topic distances between teams, the ARTIST2 NoE has already set up a common infrastructure for communication and collaborative work between teams. This infrastructure is further refined within ArtistDesign.

#### Jointly-executed Programme of Activities to Spread Excellence (JPASE)

These activities serve as a relay between the NoE and the international embedded systems design community at large. They are managed at the NoE level, and are mostly not specific to any cluster. The JPASE activities are planned by the Strategic Management Board, and are implemented by the Executive Management Board and the ArtistDesign Office.

The JPASE activities consist of the following:

#### Education and Training

Even if the Education and Training activities are open to the community at large, the first beneficiaries are the NoE participants. The NoE will have a strong policy for encouraging education within its ranks. These activities play a double role:

- They work to integrate teams and viewpoints by serving as incubators for developing integrated curricula and materials. To capitalise on these activities over time, the insights gained from one event (e.g.: a summer school) are applied to subsequent events.

- They serve to disseminate results and spread excellence well beyond the partners and affiliated partners of ArtistDesign.

#### • Publications in Conferences and Journals

This is implemented through publication in the main conferences on Embedded Systems Design of the area, as well as the active participation for the organization and management of these events.

#### Industrial Liaison

This consists of actions oriented towards affiliated industrial partners, to transfer results follow and get feedback on the research and integration activities in the JPA (JPRA, JPIA).

#### • International Collaboration

These activities will play a dual role: showcase the participants' results, and reinforce the NoE's leadership role worldwide. They will also collect relevant information about evolution of the state of the art outside Europe.

#### Web Portal

This will play a key supporting role for collaboration and Integration, such as interaction between clusters, management information, such as scholarships, internal events, and progress of the work. The web portal will also be used to disseminate any relevant information to the community at large. The web portal is an essential mechanism for achieving integration and recognition.

#### Jointly-executed Programme of Research Activities (JPRA)

This section describes the JPRA Activities that are decided and executed jointly within ArtistDesign. There are two types of Activities within the JPRA: "Joint Research", and "Tools and Platforms".

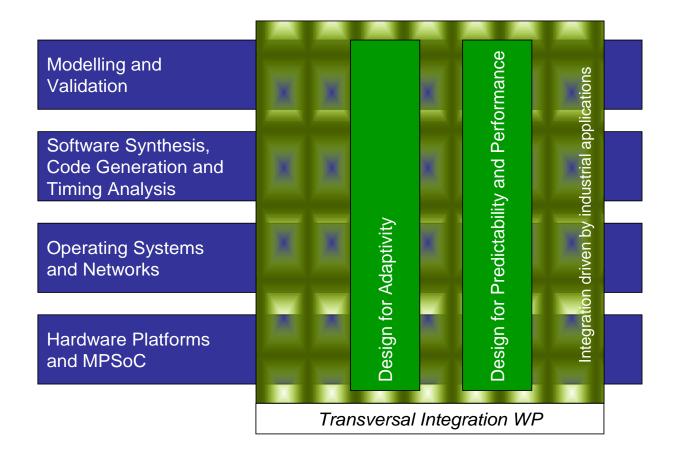

The JPRA is structured into 4 **Thematic** (horizontal) Clusters, and a Transversal Integration workpackage.

Clusters are autonomous entities, with specific objectives, teams, leader(s), and a dedicated yearly budget.

The set of Thematic Clusters cover all the main topics in Embedded Systems Design. The Activities in the Transversal Integration workpackage focus on Design methodologies, with specific objectives (Predictability, Adaptivity).

Each cluster may have one or several Activities, as appropriate.

The detailed descriptions of the "NoE Integration" research activities are provided below.

#### 1.3.2 Timing of Workpackages and their Components

All Workpackages are active throughout the 4-year period.

### 1.3.3 Workpackage List / Overview

The anticipated structure of the area reflects the following decomposition of the embedded systems design flow.

The embedded systems design flow is composed of the following cooperating activities, starting with requirements capture and leading to implementation. These activities must be well coordinated, and supported by tools and methods to ensure satisfactory levels of productivity and quality. Accordingly, we have structured the area of embedded systems design into the following topics.

| uesig    | in into the following topics.                                                                                                                                                       | Type        | Lead          | Lead                              | _                | <b>.</b>       |    |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------|-----------------------------------|------------------|----------------|----|

| WP<br>N° | WP title                                                                                                                                                                            | of activity | partic<br>no. | partic.<br>short name             | Person<br>months | Start<br>nonth |    |

| WP0      | Jointly-executed Programme of Management Activities (JPMA)                                                                                                                          | MGT         | 1             | Floralis                          | 41               | 1              | 48 |

| WP1      | Jointly-executed Programme of Integration Activities (JPIA)                                                                                                                         | RTD         | 1             | UJF/<br>Verimag                   | 161,45           | 1              | 48 |

| WP2      | Jointly-executed Programme of Activities for Spreading Excellence (JPASE)                                                                                                           | OTHER       | 1             | UJF/<br>Verimag                   | 31,86            | 1              | 48 |

| WP3      | Thematic Cluster:  Modeling and Validation  • Activity: Modelling  • Activity: Validation                                                                                           | RTD         | 4             | Aalborg<br>&<br>UJF/<br>Verimag   | 68,25            | 1              | 48 |

| WP4      | Thematic Cluster: Software Synthesis, Code Generation and Timing Analysis (JPRA)  • Activity: Software Synthesis, Code Generation  • Activity: Timing Analysis                      | RTD         | 10            | Dortmund                          | 68,00            | 1              | 48 |

| WP5      | Thematic Cluster: Operating Systems and Networks (JPRA)  • Activity: Resource-Aware OS  • Activity: Scheduling & Resource Mgt  • Activity: Embedded RT Networking                   | RTD         | 24            | SSSA-<br>(Pisa)                   | 35,41            | 1              | 48 |

| WP6      | WP6: Thematic Cluster: Hardware Platforms and MPSoC (JPRA)  • Activity: Platform and MPSoC Design  • Activity: Platform and MPSoC  Analysis                                         | RTD         | 13            | DTU                               | 81,00            | 1              | 48 |

| WP7      | Transversal Integration (JPRA)  • Activity: Design for Adaptivity  • Activity: Design for Predictability and Performance  • Activity: Integration Driven by Industrial Applications | RTD         | 22            | Trento<br>(previously<br>PARADES) |                  | 1              | 48 |

|          | TOTAL                                                                                                                                                                               |             |               |                                   | 575,32           |                |    |

#### 1.3.4 Deliverables List

| 1.3.4 Deliverables List |                                                                     |           |                  |                  |                |  |  |  |  |  |

|-------------------------|---------------------------------------------------------------------|-----------|------------------|------------------|----------------|--|--|--|--|--|

| Del. no.                | Deliverable<br>name                                                 | WP<br>no. | Nature           | Dissem.<br>level | Delivery date  |  |  |  |  |  |

| WP0: Join               | nt Programme of Management Activities                               | S (JPMA   | <b>\</b> )       |                  |                |  |  |  |  |  |

| D1-(0.1)-Y <i>n</i>     | Periodic Report                                                     | WP0       | Report           | REstri<br>cted   |                |  |  |  |  |  |

| D2-(0.2)-Yn             | Project Management Report                                           | WP0       | Report           | REstri<br>cted   |                |  |  |  |  |  |

| WP1: Joii               | nt Programme of Integration Activities (                            | JPIA)     |                  |                  |                |  |  |  |  |  |

| D3.(1.0)-Y <i>n</i>     | Integration Activities Report                                       | WP1       | Report           | <b>PU</b> blic   |                |  |  |  |  |  |

| WP2: Join               | nt Programme of Activities for Spreadin                             | g Exce    | llence (J        | PASE)            |                |  |  |  |  |  |

| D4-(2.0)-Yn             | Spreading Excellence Report                                         | WP2       | Report           | <b>PU</b> blic   |                |  |  |  |  |  |

| WP3: The                | matic Cluster: Modeling and Validation                              | (JPRA)    |                  |                  | These<br>deliv |  |  |  |  |  |

| D5-(3.1)-Yn             | Modeling Report                                                     | WP3       | Report           | <b>PU</b> blic   | erables<br>are |  |  |  |  |  |

| D6-(3.2)-Yn             | Validation Report                                                   | WP3       | Report           | PUblic           | due at:        |  |  |  |  |  |

|                         | ematic Cluster: Software Synthesis, Cod<br>I Timing Analysis (JPRA) | le Gene   | eration          |                  | T0+12          |  |  |  |  |  |

| D7-(4.1)-Y <i>n</i>     | Software Synthesis, Code Generation                                 | WP4       | Report           | <b>PU</b> blic   |                |  |  |  |  |  |

| D8-(4.2)-Yn             | Timing Analysis                                                     | WP4       | Report           | PUblic           | T0+24          |  |  |  |  |  |

| WP5: The                | ematic Cluster: Operating Systems and I                             | Networ    | ks (JPR <i>A</i> | <b>A)</b>        | T0+36          |  |  |  |  |  |

| D9-(5.1)-Yn             | Resource-Aware Operating Systems                                    | WP5       | Report           | <b>PU</b> blic   |                |  |  |  |  |  |

| D10-(5.2)-Yn            | Scheduling and Resource Management                                  | WP5       | Report           | <b>PU</b> blic   | T0+48          |  |  |  |  |  |

| D11-(5.3)-Yn            | Real-Time Networks                                                  | WP5       | Report           | <b>PU</b> blic   |                |  |  |  |  |  |

| WP6: The                | ematic Cluster: Hardware Platforms and                              | MPSoC     | C Design         |                  |                |  |  |  |  |  |

| D12-(6.1)-Yn            |                                                                     | WP6       | Report           | PUblic           |                |  |  |  |  |  |

| D13-(6.2)-Yn            | Platform and MPSoC Analysis                                         | WP6       | Report           | <b>PU</b> blic   |                |  |  |  |  |  |

| WP7: Tra                | nsversal Integration (JPRA)                                         |           |                  |                  |                |  |  |  |  |  |

| D14-(7.1)-Yn            | Design for Adaptivity                                               | WP7       | Report           | PUblic           |                |  |  |  |  |  |

| D15-(7.2)-Yn            | Design for Predictability                                           | WP7       | Report           | PUblic           |                |  |  |  |  |  |

| D16-(7.3)-Yn            | Industrial Integration                                              | WP7       | Report           | <b>PU</b> blic   |                |  |  |  |  |  |

Where n=1,2,3,4 for each end-of-year project review.

#### 1.3.5 Workpackage Descriptions

WP0 Description - JPMA

| WP number          | 0         |                                  | Start date or starting event:  T0 (start of the project) |         |             |     |        |  |  |

|--------------------|-----------|----------------------------------|----------------------------------------------------------|---------|-------------|-----|--------|--|--|

|                    |           |                                  |                                                          | •       | •           | • , |        |  |  |

| WP Title           | Jointly-e | executed Progra                  | amme of M                                                | anageme | nt Activiti | ies | (JPMA) |  |  |

| Activity type      | MGT A     | MGT Management of the consortium |                                                          |         |             |     |        |  |  |

| WP Leader          | Floralis  |                                  |                                                          |         |             |     |        |  |  |

| Participant number | 1         | 2                                | 30                                                       |         |             |     |        |  |  |

| Short name         | Floralis  | UJF/VERIMAG                      | Vienna                                                   |         |             |     |        |  |  |

| Person-<br>months  | 34,00     | 6,50                             | 0,50                                                     |         |             |     |        |  |  |

#### **Objectives**

The NoE Management organization is carried out through three activities: Strategic Management, Operational Management and Relations with the R&D Community at large.

#### **Description of work**

The Management Workpackage includes the Strategic Management and Operational Management activities. Floralis acts jointly with UJF/VERIMAG.

- Strategic Management

- Yearly plenary meetings, at T0, T0+12, T0+24, T0+36, T0+48 are organised, to plan the work in detail.

- Operational Management

- Operational management implements the yearly plenary meeting decisions, and the setting up the infrastructure.

- Relations with the R&D Community at large

- Direct interaction and relations with the community in the large are mainly handled by the ArtistDesign Office. The main strategic directions and orientations are decided the Strategic Management Board.

#### **Deliverables**

D1-(0.1)-Yn Periodic Report

D2-(0.2)-Yn Project Activity Report (where n=1,2,3,4 for each end-of-year project review)

To ensure correct integration and coordination of Activities, and coordination between the partners, the Consortium will carry out a Joint Programme of Management Activities (JPMA). It includes 3 activities: Strategic Management, Operational Management, and Relations with the R&D Community at large.

#### Strategic Management

The ArtistDesign Strategic Management Board handles the major decisions of the NoE, in phase with the formal reviews of the European Commission (initial project kick-off, and annual reviews for JPA reporting and updating). The Strategic Management Board is composed of the following persons:

Joseph Sifakis (UJF/VERIMAG) - chair, Bruno Bouyssounouse (UJF/VERIMAG), Tom Henzinger (IST Austria), Kim Larsen (Aalborg), Peter Marwedel (Dortmund), Reinhardt Wilhelm (Saarland), Giorgio Buttazzo (SSSA-Pisa), Alan Burns (York), Luis Almeida (UnivPORTO), Jan Madsen (DTU), Lothar Thiele (ETH Zurich), Luca Benini (Bologna), Karl-Erik Årzén (ULund), Bengt Jonsson (Uppsala), Alberto Sangiovanni Vincentelli (TRENTO), Albert Benveniste (INRIA)

#### Operational Management

The ArtistDesign Operational Management is carried out by the Executive Management Board and the ArtistDesign Office, acting in tight collaboration. The respective roles of these two bodies are:

- The Executive Management Board is a representative subset of the Strategic Management Board, where each cluster is represented by one leader. It meets on a roughly monthly basis, either via phone conference, or in person. It is composed of: Joseph Sifakis (UJF/VERIMAG) chair, Bruno Bouyssounouse (UJF/VERIMAG), Susanne Graf (UJF/VERIMAG), Kim Larsen (Aalborg), Peter Marwedel (Dortmund), Giorgio Buttazzo (SSSA-Pisa), Jan Madsen (DTU), Karl-Erik Årzén (ULund), Bengt Jonsson (Uppsala), Alberto Sangiovanni Vincentelli (TRENTO).

- The ArtistDesign Office ensures day-to-day management, including scientific, technical, legal, administrative, and financial activities. The Scientific Coordinator is Joseph Sifakis (UJF/VERIMAG). The Technical Coordinator is Bruno Bouyssounouse (UJF/VERIMAG). The legal, administrative and financial coordinators are Liliane Pereira Bahia and Olivier GUERARD (Floralis).

The ArtistDesign operational management implements the major decisions taken by the Strategic Management Board, and reports to it. It includes responsibility for the JPA, and monitors progress on a scientific and technical level. It validates the technical reports produced to the European Commission. The Executive Management Board submits proposals to the Strategic Management Board.

#### Relations with the R&D Community at large

Direct interaction and relations with the community in the large are mainly handled by the ArtistDesign Office. The main strategic directions and orientations are decided the Strategic Management Board.

The main effect of this activity is in coordinating and implementing the Jointly Executed Programme for Spreading Excellence (JPASE).

Relations with the R&D community at large are organized mainly bottom-up, through the organisation of scientific events, publications, distribution of tools and components, industrial partnerships (not funded by ArtistDesign), education; and through the ArtistDesign web pages.

Our policy aims specifically at enforcing integration of existing scientific events in the area, as was done in ARTIST2. An example is our participation in setting up the Embedded Systems Week. For sponsoring scientific events, we will apply the procedures developed in the ARTIST2 NoE (http://www.artist-embedded.org/artist/Allocating-JPASE-Funds.html).

## WP1 Description - JPIA

| WP                  | 1               |                           |                                                             |              | Start da             | ite or sta | rting ev      | ent:  |                |               |         |  |