# ARTIST2 Newsletter n°3

Newsletter

#### INTRODUCTION

This is the third edition of the newsletter for the ARTIST2 Network of Excellence on Embedded Systems Design (<a href="http://www.artist-embedded.org">http://www.artist-embedded.org</a>).

This newsletter is meant to serve the larger embedded systems research and industrial community, by announcing events of interest (workshops, summer schools, high level events, selected publications for a wide audience).

We hope that by providing these pointers, this newsletter will contribute to our overall objective of integration and building excellence within the community.

# **Newsletter Subscription**

Subscription to the newsletter is free of charge. If you would like to be added or removed from the subscription list, simply send a message to the editor:

Bruno.Bouyssounouse@imag.fr

## Online

This newsletter is also available online:

http://www.artist-embedded.org/artist/ Artist2-Newsletter-438.html

# Foreword from the Project Officer

#### Javid KHAN - Scientific Officer DG Information Society and Media - European Commission

The Seventh Framework Programme is upon us and we are all busy preparing for the first calls. The new ICT Workprogramme includes three objectives with Embedded Systems design and Computing Systems in the first call and Networked Embedded Systems in the second call. If you are interested in finding out more or are preparing a proposal idea or looking for partners in Embedded Systems Design have a look at the slides from our recent Information Day on 7th March 2007 (<a href="http://cordis.europa.eu/ist/embedded/infoday-070307.htm">http://cordis.europa.eu/ist/embedded/infoday-070307.htm</a>).

The IST 2006 Event in Helsinki last November was the biggest and best one ever, according to several independent reports. There were over 4500 participants with over 250 speakers, 160 exhibits, over 100 networking sessions and workshops. There were numerous sessions on embedded-systems related activities (<a href="http://ec.europa.eu/information\_society/istevent/2006/cf/search.cfm?searchFor=embedded+systems">http://ec.europa.eu/information\_society/istevent/2006/cf/search.cfm?searchFor=embedded+systems</a>) at the Event.

Congratulations once again on the new and dynamic website. I see that the content is growing and improving - keep up the good work! The site got an 'honourable mention' from the jury in last November's «Best IST Website» contest where 256 websites were entered and 22,000 votes were cast on the internet (http://ec.europa.eu/information\_society/istevent/2006/competitions/websites/index\_en.htm).

The Seventh Framework Programme provides new mechanisms to set up public-private partnerships, known as Joint Technology Initiatives (JTIs). These will be implemented through a Joint Undertaking, whose members will be the European Commission, ARTEMISIA (a non-for-profit industryled association) and Member/Associated States that want to invest in the area. Artemisia was launched in January 2007. Once operational, the Joint Undertaking will launch open Calls for proposals to implement the ARTEMIS Strategic Research Agenda. The total cost of this bold new initiative is 3 Billion euros and we have a lot of work to do in order to put this mechanism in place (http://www.artemis-office.org/).

So, I hope that 2007 will be an exciting year for embedded systems with two calls in and the launch of the Joint Technology Inititative.

# **Table of Contents**

| Introduction, Foreword 1     |

|------------------------------|

| Focus on Execution Platforms |

| Workshops 4                  |

| Conferences 5                |

| Schools and Courses          |

| Other Activities             |

| Invited Articles9            |

| About the Artist2 NoE 10     |

|                              |

## **Mailing List**

To receive frequent information on topics in Embedded Systems Design (workshops, open positions, etc), subscribe to our mailing liet:

http://www.artist-embedded. org/artist/Artist-Mailing-List. html

This list is separate from the one for the Artist newsletter.

# Focus on Execution Platforms

ARTIST2 Newsletter

April 10th 2007

#### Pr Lothar Thiele - ETH Zürich

#### Introduction

In relation to the ARTIST2 network, it is the overall goal of the topic on execution platforms to extend the current state in composability towards issues like modeling of non-functional constraints, power and energy, end-to-end real-time behavior, timing and performance analysis and heterogeneous models of computation. One of the most critical issues to be faced in the research on execution platform is their rapidly growing complexity. Complexity increase is pushed by Moore's law, and by the ever-increasing demand for high performance computing. In addition, the boundaries between hardware and software domains are getting more blurred (dynamically re-configurable hardware, adaptable embedded systems, breakthrough in power consumption and performance) and challenging questions are at the border (trade-offs in mapping applications to hardware and software components, re-configurable hardware, WCET, performance of distributed computer and communication systems).

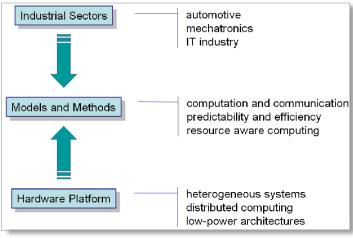

Figure 1

The cluster attempts to combine the diverse knowledge and to integrate different approaches approaches in the area of execution platforms for embedded systems available in Europe and beyond, see Figure 1.

# Cooperation with Industry

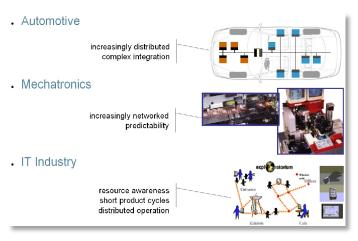

Following Figure 2, the major industrial sectors considered are Automotive and Mechatronics Industry as well as Information Technology.

The automotive industry is currently in a fast and spectacular evolution towards the intelligent, safe, environmental, interconnected, and economic car. Electronics is at the basis of most of this development. This evolution brings a series of challenges in all steps of the development cycle. How to specify and model such a complex system? There is a need for a component based modelling, analysis, and synthesis approach in which independently designed hardware and software components can safely be combined into a working system. How to achieve the ever increasing demand on functionality and safety, at an affordable cost? Modern automotive electronic systems are highly distributed networks with components interacting over various infrastructures. How to achieve a safe and predictable system at such a huge level of complexity and heterogeneity? A well defined methodology is needed for mapping the complex functionalities on predefined distributed automotive platforms. This assumes well defined standards, middleware layers, analysis tools, software generation to ols, design exploration and optimisation approaches. Traditionally, the development of mechatronic systems was a rather sequential process. First the mechanical part was designed, next the hardware infrastructure was fixed, and finally the embedded software was developed. Typically, this lead to many proplems at systems engineering, because only then the interference of design decisions from the disciples became visible. To improve this process and to shorten the time-to-market, there is a clear trend towards concurrent engineering. To be able to detect problems earlier in the development cycle, there a strong need for high-level models that allow early analysis of systemlevel design decisions. Moreover, there is an increasing interest in the use of models to improve the early testing process; for instance, one would like to test the embedded software before its environment is available. Microelectronic technology is continuing to grow according to Moore's law.

However, the need for computation power in industry is growing even faster. This is the case with traditional areas such as technical/scientific computation, and, more recently, modern applications, for instance interactive multimedia, high bandwidth communication, or speech recognition

Many of these applications are running on mobile a computer, which makes issues even more complicated: an unprecedented amount of computation power has to be delivered with very low energy consumption. So, instead of just running after high performance, industry is out after a good performance - energy product.

These unprecedented performance/energy requirements cannot be achieved by further pushing processor technology along the traditional Pentium lines. New architectures are needed in which several lower performance (and less energy hungry) computation nodes are cooperating in order to globally achieve the expected performance. Modern MPSoC and NoC architectures are developed along these lines. There is a strong cooperation between the partners involved in the cluster on 'Execution Platforms' and small and larger enterprises such as Siemens, Atmel,Volvo, Oce, Volkwagen, AbsInt, Intel, STMicroelectronics Coware, ETAS, Freescale, Bulldast. In addition, two start-up companies emerged from activities related to the ARTIST2 network of excellence: Teklatech and SymtaVision.

Figure 2

# **Definition**

This topic is strongly linked to the compilation and implementation of embedded systems. For a given application, it is important to have the technology, methods and tools to make rational choices about the platform and the design used, before proceeding to final implementation. Researchin Execution Platform stargets the development of the theoretical and practical tools for modelling the dynamic behaviour of application software for a given platform. This is a new area of research, which will allow greater flexibility in designing optimal embedded systems.

Further information is available online:

http://www.artist-embedded.org/artist/-Execution-Platforms-.html

#### **Artist2 Partners**

The Execution Platform cluster includes the following Artist2 Partners.

- Lothar Thiele (ETH Zurich)

- Luca Benini (University of Bologna)

- Petru Eles (Linkoping University)

- Rolf Ernst (TU Braunschweig)

- Jan Madsen (TU Denmark)

- Peter Marwedel (Dortmund Univ.)

- Jeroen Voeten (TU Eindhoven)

Further information is available online: http://www.artist-embedded.org/artist/ Execution-Platforms-46.html

#### Research Activities

# Artist2 Research and Integration Activities

- Resource-aware Design (NoE Integration)

- Communication-centric Systems (Cluster Integration)

- Design for Low Power (Cluster Integration)

- System Modelling Infrastructure(Platform)

Further information is available online: http://www.artist-embedded.org/artist/Research-and-Integration-230.html

#### Interview

Q: Tell us about some of the main results in Execution Platforms, in recent years

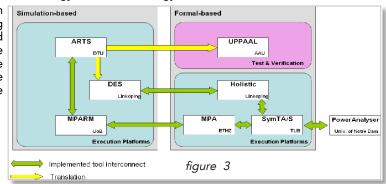

ARTIST2 is a network of excellence. Therefore, the mainfocus of the activities is on integration, i.e. combining different expertise that is available at the top researchsites in Europe. There are several indicators of success that reflect the main results of this form of cooperation. In the previous year, we have been organizing 6 workshopsand tutorials at major conferences such as DATE and RTAS. The cooperation in terms of research becomes most obviousby noting that we have been writing 17 joint publications for major conferences and journals, i.e. publications with coauthors from different ARTIST2 participants. One major highlight is the unification of models and methods for the analysis and simulation of complex distributed embedded systems such as multiprocessors-on-a-chip, see Figure 3. In a huge effort, completely different view-points on the functional and timing evaluation of have been combined. In addition, the various tools that existed at the partner sites are now linked and can inter-operate so as to perform an analysis on various levels of abstraction, with different run-times and different degrees of accuracy.

Q: Are there any significant mid- or long-range trends that can be identified? Would you care to make predictions about what the research/industrial landscape could be like 10 years from now?

Many embedded system applications are implemented today using distributed architectures, consisting of several hardware nodes interconnected in a network.

Each hardware node can consist of a processor, memory, interfaces to I/O and to the network. The networks are using specialized communication protocols, depending on the application area. For example, in the automotive electronics area communication protocols such as CAN, FlexRay and TTP are used. As the complexity of the functionality increases, the way it is distributed has changed. If we take as an example the automotive applications, initially, each function was running on a dedicated hardware node, allowing the system integrators to purchase nodes implementing required functions from different vendors, and to integrate them into their system. Currently, number of such nodes has reached more than 100 in a high-end car, which can lead to large cost and performance penalties. Not only the number of nodes has increased, but the resulting solutions based on dedicated hardware nodes do not use the available resources efficiently in order to reduce costs.

For example, it should be possible to move functionality from one node to another node where there are enough resources (e.g., memory) available. Moreover, emerging functionality, such as brake-by-wire, is inherently distributed, and achieving an efficient fault-tolerant implementation is very difficult in the current setting. With growing embedded system complexity more and more parts of a system are reused or supplied, often from external sources. These parts range from single hardware components or software processes to hardware-software (HW-SW) subsystems

They must cooperate and share resources with newly developed parts such that the design constraints are met. There are many software interface standards such as CORBA, COM or DCOM, to name just a few examples that are specifically designed for that task. Nevertheless in practice, software integration is not a solved but a growing problem. Power management is viewed as a strategic technology both for integrated and distributed embedded systems. In the first area, the trend is toward supporting power management in multi-core architectures, with a large number of power-manageable resourcers. Silicon technology is rapidly evolving to provide an increased level of control of-on chip power resources. Technologies such as multiple power distribution regions, multiple power-gating circuits for partial shutdown, multiple variable-voltage supply circuits are now commonplace. In the area of distributed low-power systems, wireless sensor networks are the key technology drivers, given their tightly power constrained nature. One important trend in this area is toward "battery free" operation. This can be achieved through energy storage devices (e.g. super-capacitors) coupled with additional devices capable of harversting energy from environmental sources (e.g. solar energy, vibrational energy).

Battery-free operation requires carefully balancing harvested energy and stored energy agains the energy consumed by the system, in a compromise between quality of service and sustainable lifetime.

Newsletter

# **Artist Web Portal**

A list of upcoming ARTIST-related events is available online:

http://www.artist-embedded.org/

#### **IRTAW**

13th International Real-Time Ada Workshop April 17-19, 2007 Woodstock, Vermont, USA Sponsored by Artist

The International Real-Time Ada Workshop meetings provide a forum for identifying issues with real-time system support in Ada and for exploring possible approaches and solutions, and has attracted participation from key members of the research, user, and implementer communities worldwide.

http://www.artist-embedded.org/artist/ IRTAW-13.html

# SCOPES 2007

10th International Workshop on **Software and Compilers for Embedded** Systems April 17-19, 2007

Woodstock, Vermont, USA Sponsored by Artist

SCOPES focuses on the software generation process for modern embedded systems. Topics of interest include all aspects of the compilation with suitable process, starting modeling and specification techniques and programming languages for embedded systems.

http://www.artist-embedded.org/artist/ SCOPES-2007.html

# **Upcoming Workshops and Seminars**

Dagstuhl Geometry in Sensor Networks April 9-13th, 2007 Dagstuhl, Germany

Wireless offer sensors exciting new possibilities for both passive monitoring and active intervention in all environments that matter to our health, security, economy, and life. Once deployed, these devices can collaboratively sense and reason about widearea phenomena and provide a distributed awareness that no centralized system can attain.

Geometry plays a pivotal role in determining many important characteristics of these systems. For instance, the topology of the network is determined largely by the sensor locations; popular communication protocols use geographic information or sensor coordinates for routing data within the network; the sensed data is intimately tied to the sensor locations; applications access data based on spatial attributes, and so on. As a result, there has been significant research activity in the past few years on problems that cut across multiple disciplines: networking, distributed algorithms and data structures. computational geometry, databases, graph embedding, topology, etc.

The aim of this seminar is to bring together experts from several areas of computer science and mathematics for discussions and exchange of ideas on the role of geometry in the evolution of sensor networks. The meeting will help identify important problems, research and develop a coherent view of many different ideas being pursued within different communities.

http://www.dagstuhl.de/de/ programm/kalender/semhp/ ?semid=29469

**Towards a Systematic** Approach to ES Design

#### Artist Workshop at Date'07

April 20th, 2007 Nice, France Organised, funded by Artist

European research developing leading-edge tools, working towards a systematic approach Émbedded Systems Design. Industry has strong needs for design methods and tools. Although significant gaps remain between the underlying technologies such as modelling languages and analysis techniques-, a system-oriented approach is the long-term objective.

This workshop aims to:

- Increase awareness for potential industrial users about existing leadingedge academic embedded systems design tools.

- Report on industrial use of these results and tools, through specific cases presented by industrial users.

- Present and discuss industrial needs and challenges to systematic design and development.

- Discuss measures improving accessibility and transfer of academic results.

Embedded systems are employed in a wide range application domains, with differing requirements - leading to different needs in terms of tools. We do however believe that there are many commonalities in dealing with complex embedded systems, such as approaches to architectural design, analysis and testing.

http://www.artist-embedded. org/artist/ARTIST2-Workshopat-Date-07.html

2nd Int'l ARTIST Workshop on **Control for Embedded Systems**

#### Workshop on Control for **Embedded Systems**

May 31st - June 1st 2007 U. of Illinois, USA Sponsored by Artist

The aim of the workshop is to gather key researchers within the control and real-time computing fields to chart the research agenda for the next decade in control for embedded systems. Topics:

- Real-time and Control in Sensor/Actuator Networks

- RT and Control issues in Cyber-Physical Systems

- Event-Based Control and Computing

- Control of Software Errors http://www.artist-embedded. org/artist/Control-for-Embedded-Systems-810.html

#### DCDS'07

June 13-15, 2007 Cachan (Paris), France Organised with Artist partners

The aim of this first IFAC workshop is to provide the communities of safety/ reliability analysis and of DES (Discrete Event Systems) with an opportunity to exchange information and new ideas, and to discuss new developments in the field of dependable control of discrete event critical systems. Research in this field is driven by the needs of many different applications domains, such as production systems, transport systems, embedded systems, ...

The workshop will cover all topics related to specification, design, implementation and operation of dependable controllers for critical discrete svstems.

http://www.artist-embedded. org/artist/DCDS-07.html

# Conferences

## Newsletter

April 10th 2007

# **Other Conferences**

The full set of conferences referenced by Artist is available here: <a href="http://www.artist-embedded.org/artist/">http://www.artist-embedded.org/artist/</a>

#### See Also

#### IESS'07

May 29th - June 1st 2007 Irvine, California, USA

The goals of the International Embedded Systems Symposium are to present exchange and discuss the state of the art, novel ideas, actual research results, and future trends in the field of embedded systems. Contributors and participants from both industry and academia are encouraged to take active part in this symposium. http://www.iess.org/

#### NOCS'07

# May 6-9, 2007

#### **Princeton University, USA**

Network-on-Chip (NoC) is an emerging paradigm using packet-switched networks for communications within large VLSI systems on-chip. NoCs are poised to provide enhanced performance, scalability, modularity, and design productivity as compared with previous communication architectures.

http://www.artist-embedded.org/artist/-International-Symposium-on-.html

#### ECRTS'07

June 4-6, 2007 Pisa, Italy

The nineteenth EUROMICRO Conference on Real-Time Systems covers all aspects of state-of-the-art research and development in real-time computing. We encourage papers on industrial case studies, application of real-time technology on realistic systems, and real-time operating systems implementations.

http://feanor.sssup.it/ecrts07/

# **Upcoming Conferences with Artist Partners**

Design, Automation and Test in Europe

#### DATE'07

April 16-20 2007 Nice, France Sponsored by Artist

The 10th DATE conference and exhibition is Europe's largest event for the design, test and manufacture of electronic systems and circuits.

The five-day event consists of a scientific conference, complemented by commercial exhibition showing the state-of-theart in design and test tools, methodologies, IP and design services, reconfigurable and other hardware platforms, embedded software, and (industrial) design experiences from different application domains, e.g. automotive, wireless, telecom and multimedia applications.

## TECHNICAL CONFERENCE

Keynotes, scientific papers, interactive presentations, design records, discussion panels, hot-topics, tutorials and workshops.

This year there are two dedicated days of specially focused conference sessions in the following areas of design applications

- Ubiquitous Computing and Communications

- Space and Aeronautics

A full list of topics is available online.

# EXHIBITION

#### April 17-19, 2007

Over 100 companies showing the best in design, verification and test tools and platforms for embedded systems and electronic devices, IP cores and design services.

http://www.artist-embedded. org/artist/ DATE.html

Formal Methods and Models for Codesign

#### **MEMOCODE 2007**

May 30th - June 1st 2007 Nice, France Organised with Artist partners

The goal of MEMOCODE 2007, the fifth in a series of successful international conferences, is to gather together researchers and practitioners in the field of the design of modern hardware/ software systems to explore ways in which future design methods can benefit from new results on formal methods. Many abstract models. analysis languages, and techniques produced by formal methods research already proved to provide a sound methodological basis for highlevel modeling, design, and development of hardware/ software systems and for adapting and integrating existing components to meet new requirements. Papers, panel proposals, and tutorial proposals are invited on topics relevant to the application of formal methods to hardware and software design. These topics include, but are not limited to:

- Formal system/property specification languages

- Modeling hardware/ software systems

- Formal methods for performance/power analysis

- Optimization based on formal methods

- Formal verification (model checking, theorem proving)

- Specification-based testing

- Design methodologies based on formal methods

- Component-based design/ design space exploration

http://memocode.irisa.fr/

Computer-Aided Verification

#### **CAV 2007**

July 3-7th 2007 Berlin, Germany Sponsored by Artist

CAV'07 is the 19th in a series dedicated to the advancement of the theory and practice computer-aided formal analysis methods for hardware and software systems. CAV considers it vital to continue its leadership in hardware verification, and maintain its recent momentum in software verification. The conference covers the spectrum from theoretical results to concrete applications, with an emphasis practical verification on tools and the algorithms and techniques that are needed for their implementation. The proceedings of the conference will be published in the Springer-Verlag Lecture Notes in Computer Science series. A selection of papers will be invited to a special issue of the International Journal on Formal Methods and System Design.

Invited Speakers:

- Byron Cook, Microsoft Research

- Thomas Kropf, Robert Bosch AG

- David Russinoff, AMD

http://cav2007.org/

# Schools and Courses

Newsletter

## Other Schools

Past and upcoming schools referenced by Artist are visible on our web portal:

http://www.artist-embedded.org/artist/-Schools-.html

# Other Schools and Courses

• FOSAD 2007 September 9-15, 2007 Bertinoro, Italy

http://www.artist-embedded.org/artist/ FOSAD-877.html

EPSD 2007: Embedded Programmable System Design September 10-14, 2007 EPFL, Lausanne, Switzerland

http://www.artist-embedded.org/artist/-Embedded-Programmable-System-.html

# **Upcoming Schools and Courses**

#### ARTIST2 Graduate Course on Embedded Control Systems

May 7-11, 2007 Lund, Sweden Organised and funded by Artist

The strategic objective of the ARTIST2 Network of Excellence is to strengthen European research in Embedded Systems Design, and promote the emergence of this multi-disciplinary area. One of the main activities in the Network is the Joint Programme of Activities for Spreading Excellence. These are activities for disseminating excellence across all available channels, targeting industry, students, and other European and international research teams.

http://www.artist-embedded.org/artist/-ARTIST-Graduate-Course-on-Embedded-.html

#### Artist2 / UNU-IIST School in China - 2007

August 1-10, 2007 Suzhou (near Shanghai), Organised and funded by Artist

ARTIST2 will organize, in collaboration with UNU-IIST, the 2nd edition of its China on Embedded Systems Design.

#### Lecturers:

- Prof. Karl-Erik Arzen (Lund U., Sweden)

- Prof. Dr. Luca Benini (U. Bologna, Italy)

- Paul Caspi (Verimag Lab, France)

- Kim Larsen (Aalborg U., Denmark)

#### **Coordinating Committee:**

- Zhou Chaochen, Academician of CAS, Institute of Software, CAS, Beijing

- He Jifeng, Academician of CAS, East China Normal University, Shanghai

- Wang Ji, National Lab for Parallel and Distributed Computing, Changsha

- Zhiming Liu, UNU-IIST, Macao

- Zhu Qiaoming, Suzhou University, Suzhou

- Zhou Xinshe, North West Polytechnic Univeristy, Xi'an

- Li Xuandong, Nanjing University, Nanjing

- Bruno Bouyssounouse (Artist2 NoE)

- Joseph Sifakis (Verimag)

- Wang Yi (Uppsala University)

http://www.artist-embedded.org/artist/-Artist2-UNU-IIST-School-in-China-.html

# First European-SouthAmerican School for Embedded Systems

August 20-24, 2007

Buenos Aires - Argentina

Organised and funded by Artist

The purpose of the school is to foster the well established and dynamic research cooperations in the field of embedded systems between groups in Europe and South America, by allowing south-american students (specially graduate), to meet european researchers. We strongly believe this will offer an excellent opportunity to strengthen the relationships with mutual benefit.

The school will be a repeated event on a yearly basis. Besides the lectures given by european researchers, there will be invited talks by southamerican researchers and space (poster session) for graduate students to present and discuss their work.

http://www.artist-embedded.org/artist/-First-European-SouthAmerican-.html

# Embedded Programmable System Design EPSD 2007

Septamber 10-14, 2007 EPFL, Lausanne, Switzerland Sponsored by Artist

Advanced engineering courses will be offered by the Swiss Federal Institute of Technology, Lausanne, Switzerland, during summer period 2007. The invited lecturers are top experts in the field, currently working at leading European and American companies, research institutes and universities active in IC design. Courses will be taught in English. Each attendee will receive a certificate of attendance at the course.

These courses are aimed at providing engineers with up-to-date information on important current issues of design in analog and mixed-mode integrated circuits. This year, the subjects proposedareparticularlyfocusedonLow-Voltage, Low-Power, RF and Wireless Communications, Testing Data-Converters, Transitor-Level Analog Design, Power Management, Low-Noise, Low-Offset, Hostile Environment and Cryptographic Engineering design problems and solutions. In general, the content of the lectures covers introduction, state-of-the-art in the specific field and practical case studies. The intent is to give to the participants a broad coverage of hints and design methods to be applicable in practice.

http://www.artist-embedded.org/artist/-EPSD-2007-.html

# Schools and Courses

**ARTIST2** Newsletter

April 10th 2007

# MODELLING, TESTING, and Verification for Embedded Systems ARTIST2 Winter School 2007 \*\*Farming 1922 2027 - Farming July \*\*Programme Monday, Tebruary 1920 2020 Modeling and Design of Heterogeneous Systems Selected Systems Sel

#### **Past Artist Schools**

ARTIST2 Summer School on Component & Modelling, Testing & Verification, and Statical Analysis of Embedded Systems ARTIST2 Summer School 2005

http://www.artist-embedded.org/artist/-ARTIST2-Summer-School-2005-.html

The first ARTIST / UNU-IIST Spring School on Models, Methods and Tools for Embedded Systems has been held in Xi'an, China, April 3rd – 15th 2006.

# ARTIST2 / UNU-IIST Spring School in China 2006

http://www.artist-embedded.org/artist/-ARTIST2-UNU-IIST-China-School-.html

Further information is available online: <a href="http://www.artist-embedded.org/artist/-Schools-.html">http://www.artist-embedded.org/artist/-Schools-.html</a>

#### ARTIST2 Winter School 2007 - MOTIVES

# OVERVIEW MOdelling, TestIng, and Verification for Embedded Systems

The Winter School offered a number of foundational tutorials, accompanied by a selection of lectures on exciting emerging technologies and industrial applications - given by leading scientific and industrial experts.

This 5-day winter school was for young researchers working or wanting to work in modelling, validation, synthesis and performance analysis of embedded systems, as well as engineers from industry with a practical background in design, control and testing of embedded systems.

The Winter School was organised by the ARTIST2 Network of Excellence, with strong contributions from three of its research clusters: Real-Time Components, Testing & Verification and Compilers & Timing Analysis.

The school was opened for participation by all, although some previous training and/or experience in the fundamentals of computer science and a knowledge of computer architectures was required.

#### **Student Presentations**

Students were invited to send a short abstract (about 200 words) to Jan Reineke (reineke AT cs.uni-sb.de) describing their PhD project and to make a poster (in A3 format).

#### **ORGANISATION**

#### Steering Committee

- Bengt Jonsson (Uppsala Univ., Sweden)

- Kim G. Larsen (Aalborg Univ., Denmark)

- Reinhard Wilhelm (Saarland University, Germany)

#### Organizational Committee

- Bruno Bouyssounouse (Verimag, France)

- Luigi Palopoli (University of Trento, Italy)

- Jan Reineke (Saarland University, Germany)

#### **PROGRAMME**

- Modeling and Design of Heterogeneous Systems Alberto Ferrari (Parades Italy)

Joseph Sifakis (Verimag, France)

Roberto Passerone (Trento, Italy)

Benoit Caillaud (INRIA, France))

- Model Transformation and UML

Reiko Heckel (Leicester, UK)

Andy Schuerr (Darmstadt, Germany)

Wang Yi (Uppsala, Sweden)

Julio Medina (CEA/LIST, France)

- Static Analysis for Safety and Performance

Hanne Riis Nielson (DTU, Denmark)

Reinhard Wilhelm (Saarland, Germany)

Samarjit Chakraborty (Singapore)

Sylvie Putot (CEA, France)

Joerg Bauer (Saarland, Germany)

- Static Analysis for Safety and Performance

Jean-Francois Raskin (ULB, Belgium)

Joost-Pieter Katoen (Aachen, The Netherlands)

Kim Larsen (Aalborg, Denmark)

Giuseppe Lipari (Scuola Superiore Sant'Anna Pisa, Italy)

- Testing and Run-Time Verification

Ed Brinksma (Embedded Systems Institute, The Netherlands) Vlad Rusu (RISA, France) Bernd Finkbeiner (Saarland, Germany)

$\underline{http://www.artist-embedded.org/artist/-MOTIVES-2007..html}$

Newsletter

#### Creation of ARTEMISIA

ARTEMISIA, the ARTEMIS Industrial Association, has been established to collect and represent key European industry players and R&D actors in the future Joint Technology Initiative (JTI) on embedded systems.

The association will promote the creation of a favorable environment for increased understanding and use embedded computer systems. ARTEMISIA will also be activein influencing standards and providing an excellent network for the exchange of technology ideas among potential R&D partners and key industry players.

The ARTEMISIA Steering Board is delighted to invite you to the "ARTEMISIA Setting the scene" Meeting, which will take place on March 21, 2007 in Schiphol, Amsterdam, The Netherlands.

http://www.artemis-office.org/DotNetNuke/ ARTEMISIA/tabid/114/Default.aspx

# Other European NoE & IPs

**High-Performance Embedded Architecture and** Compilation

#### **HiPEAC NoE**

Sept 2004 - Aug 2008 http://www.hipeac.net/

HiPEAC addresses the design and implementation of highperformance commodity computing devices in the 10+ year horizon, covering both the processor design, optimising compiler infrastructure, and evaluation of upcoming applications made possible by the increased computing power of future devices.

Hybrid control: heterogeneity and complexity of networked embedded systems

## **HYCON NoE**

Sept 2004 - Aug 2008 http://www.ist-hycon.org/

HYCON aims to establish a durable community of leading researchers and practitioners who develop and apply the hybrid systems approach to the design of networked embedded control systems.

Hvbrid systems provide a scientific paradigm to systematically address analysis, modelling, the simulation, synthesis, and optimisation of digital controllers physical for plants.

SPEculative and **Exploratory Design in** Systems Engineering

#### **SPEEDS**

May 2006 - April 2009 http://www.speeds.eu.com/

SPEEDS is a concerted effort to define the new generation of end-to-end methodologies, processes and supporting tools for safety-critical embedded system design. They will European systems enable industry to evolve from modelbased design of hardware/ software systems, towards integrated component based construction of complete system virtual models. The technical pillars of the **SPEEDS** approach are: A semantics-based modeling method to:

- support the construction of complex embedded systems by composing heterogeneous subsystems

- enable sound integration of new and existing tools

This modeling approach ,rich-component' defines models to represent both functional and non-functional aspects so that efficient implementations can derived from abstract models Novel formal analysis tools and techniques to assess of properties precisely the system that will allow explore architectural alternatives of implementation platforms and enable correctby-construction designs. Compositionality abstractions will make this approach scalable for large systems.

Controlled sypeculative design is a new tool-supported process which minmizes the risk of concurrent design by establishing activities formal "contracts" between inter- and intra-company design groups.

#### **ARTEMIS**

То secure employment Europe and reinforce European industry's leading position in Embedded Systems technology, thereby yielding both direct and indirect benefits to the European citizen, Artemis will:

- Accelerate the pace of innovation and address the fragmentation of the market by countering the fragmentation of R&D efforts across Europe, private and public, by means of a common and compelling Strategic Research Agenda (SRA)

- Propose practical efficient structures for stimulating Embedded R&D by Systems implementing Joint а Technology Initiative (JTI) under article 171 of the Treaty, thereby:

- Nurture an innovation eco-system based around world-class Centres of Excellence, gathering systems integrators, technology providers (SMEs and academia) with the capacity to rapidly turn research achievements into innovative products, processes and services for the global market.

- Promote Embedded Systems as a respected curriculum for highereducation

- Ensure that these strategic directions are properly coordinated, to form the backbone of a true European Research Area for Embedded Systems

http://www.artemis-office.org/

# **Invited Articles - Thales**

Newsletter

# The UML profile MARTE for Modeling and Analysis of Real-Time and Embedded systems

Laurent Rioux, Dominique Potier - Thalès

THALES and its research partners CEA and INRIA are jointly leading the industry consortium ProMARTE established for the standardisation by the OMG of a new UML profile, MARTE, for the Modeling and Analysis of Real-Time and Embedded systems (<a href="http://www.promarte.org">http://www.promarte.org</a>). The ProMARTE consortium federates tools vendors, industrials and academics partners interested in the definition of a modeling standard to support the real-time and embedded domain.

The upcoming MARTE standard shall replace model-based analysis concepts from the former SPT (Scheduling Performance and Time) profile. The targeted analysis techniques include schedulability analysis, performance analysis, Worst-Case Execution Time (WCET).

MARTE also brings new features such as:

- Modeling constructs for both software and hardware aspects of Real-time and Embedded Systems (RTES)

- Execution platform modeling and allocation of applications onto platforms

- Compliance with related OMG standards: QoS&FT, UML 2.1 and SysML

- Modeling of embedded, reactive, control/command and intensive data-flow computation systems

- Component-based architecture modeling and analysis

- Capability of modeling asynchronous/causal, synchronous/ clocked and real/continuous time

- Capability to model SAE-AADL applications

THALES brings to this initiative expertise and experience in the design of software-intensive real-time embedded systems in the fields of air and ground transportation, security and defence markets. MARTE is part of THALES R&D priority on "Open Software Systems" in terms of standards, technologies and architectures.

Concurrently with the standardisation process, THALES is launching a case study on the use of MARTE for the development of avionics systems with a Model-Driven Engineering approach.

The focus is on the design of a generic flight management system that shall satisfy strict real-time, embeddability and safety constraints. In the case study, we are using the profile MARTE to express these constraints in UML models, with the end goal to link these models to supporting analysis tools.

This case study is carried out in the context of the cooperative R&D project "Usine Logicielle" launched by the French Pôle de Compétitivité (competitiveness cluster) "SYSTEM@TIC PARIS-REGION" (http://www.systematic-paris-region.org).

# Terapix: A parallel architecture providing computing efficiency on FPGA

Philippe Bonnot - Thalès

Image processing applications and especially military optical detection systems require high computation power (in the range of 10 to 100 GOPS) under strong volume constraints. For this reason, reconfigurable components (FPGA) very often constitute the baseline solution. However, such solutions require hardware design, and are consequently not flexible and increase non-recurrent costs. An alternative is to use general purpose processors, but they provide poor density solutions that does not permit to follow anymore the Moore's law pace.

To face these issues, Thales decided to investigate a highly parallel processing architecture on FPGA. This investigation was motivated by the low access cost and the high computing performance expected from FPGA technology as well as flexibility and reusability expected from processing architecture programmability. Whereas being based on FPGA, such a programmable parallel architecture thus enables an application independent approach.

Following a first specification in April 2005, a mock-up had been completed as early as June 2006. This mock-up that embedded only 16 processing elements on a Xilinx Virtex4 FPGA provided 1 GOPS. It permitted to verify the feasibility of the approach and to identify possible specification improvements. A full scale demonstration version embedding 128 processing elements is planned to be available in May 2007. It is expected to reach 20 GOPS and consume 10 W.

A communication and synchronisation API has been developed as well as a library of basic image processing operators. Thanks to that, this approach will permit an estimated application development productivity gain of x10 compared to classical hardware approach and a processing performance gain of x20 compared to classical programmable solutions based on microprocessors. Moreover, the parallel architecture supporting this approach provides a scalable solution able to follow silicon technology progresses. As a consequence of these promising results and perspectives, Thales recently selected this advanced computing solution to implement the image processing module in a major defense programme.

Thales ambition is now to study solutions based on this principle, combining high processing power, high productivity in development and long term availability in other applications requiring high performance computation like Radar, Sonar, Electronic Warfare showing thus a multi-domain usage capability for this approach.

# **Joining Artist2**

To promote Excellence and Integration within the European embedded systems community, Artist2 accepts Affiliated Partners, who may participate in the Artist2 activities (research, integration, spreading excellence).

Costs incurred by Affiliated Partners are generally not eligible for funding. Because of this, hard requirements such as producing the deliverables are waived.

The criteria for acceptance are:

- As is the case for Artist2 core participants, the work done within the teams must be world-class, and have a significant impact on work done in external teams.

- The Affiliated Partners must participate actively in specific Artist2 research or integration activities.

- The cluster leader and scientific coordinator must approve.

The complete list of Affiliated Partners is visible here:

http://www.artist-embedded.org/artist/-Affiliated-Partners-.html

In some cases, Affiliated Partners have become Core Partners over the course of the project.

## **About Artist2**

#### Strategic Objectives

#### PURPOSE

The objective of the ARTIST2 Network of Excellence is to strengthen European research in Embedded Systems Design, and promote the integration of this emerging discipline.

#### **APPROACH**

ARTIST2 implements international and interdisciplinary effort to participate in establishing Embedded Systems Design as a discipline, combining competencies from electrical engineering, computer science, applied mathematics, and control theory. The ambition is to compete on the same level as equivalent centres in the USA (Berkeley, Stanford, MIT, Carnegie Mellon), for both the production and transfer of knowledge and competencies, and for the impact on industrial innovation.

The ARTIST2 Network of Excellence gathers together the best European teams from the composing disciplines, and aims to forge a scientific community. This objective is achieved by integration around a Joint Programme of Activities, aiming to create critical mass from these selected European teams.

#### **CLUSTER TOPICS**

ARTIST2 addresses the full range of challenges related to Embedded Systems Design, covering all aspects, ranging from theory through to applications:

- Real-Time Components

- Adaptive Real Time

- Compilers and Timing Analysis

- Execution Platforms

- Control for Embedded Systems

- Testing and Verification

# ARTIST2 Core Partners

Verimag Laboratory (Joseph Sifakis) • Caisse des Dépots et Consignations (Jean-Noel Forget) • RWTH Aachen (Rainer Leupers) • Aalborg University / CISS (Kim Larsen) • Absint (Christian Ferdinand) University of Aveiro (Luis Almeida) • University of Cantabria (Michael Gonzalez Harbour) • CEA (Francçois Terrier) • Centre Fédéré en Vérification (Pierre Wolper) • Czech Technical University (Zdenek Hanzalek) • University of Dortmund (Peter Marwedel) • Denmark Technical University (Jan Madsen) • ETH Zurich (LotharThiele) • FranceTélécom R&D (Jacques Pulou) • INRIA (Albert Benveniste) • Swedish Royal Institute of Technology - KTH (Martin Torngren) • Linköping University (Petru Eles) • CNRS/LSV Cachan (Philippe Schnoebelen) University of Lund (Karl-Erik Arzen) • Malardalen University (Bjorn Lisper) • OFFIS (Werner Damm) • PARADES (Alberto Sangiovanni Vincentelli) • UP Madrid (Juan de la Puente) • Saarland University (Reinhard Wilhelm) • Eindhoven University of Technology (Jeroen Voeten) • TU Vienna (Hermann Kopetz) • TU Braunschweig (Rolf Ernst) • University of Twente (Ed Brinksma) • University of Bologna (Luca Benini) • Uppsala University (Bengt Jonsson) • UP Valencia (Alfons Crespo) • University of York (Alan Burns) • Polythechnic University of Porto (Eduardo Tovar) • Ecole Polytechnique Fédérale de Lausanne (Tom Henzinger) • Scuola Sant'Anna Pisa (Giorgio Buttazzo) • ACE (Joseph van Vlijmen) • Tidorum (Niklas Holsti) • University of Kaiserslautern (Gerhard Fohler)

# About the Newsletter

http://www.artist-embedded.org/

#### **PURPOSE**

The ARTIST2 Newsletter is widely distributed within the European Embedded Systems research and industrial community, with information about important events of interest (workshops, summer schools, high level events, selected publications for a large audience, etc).

#### SUBMITTING ANNOUNCEMENTS

Anyone may submit announcements or articles for publication. Any information submitted for publication in the newsletter becomes public information, with no rights or restrictions imposed by the original author.

Information submitted will be edited and modified as best suits the needs of the community, at the editor's discretion.

Please note that this procedure will probably evolve over time. Be sure to check the latest issue for upto-date instructions.

#### **Privacy Policy**

ARTIST2 maintains a very strict privacy policy. Under no circumstances will we provide our mailing list to any other party, including the Artist2 partners.

To add or remove persons from the mailing list, simply send a message originating from the mailbox to be added or removed to the editor: Bruno.Bouyssounouse@imag.fr.