TRITA - MMK 2006:11 ISSN 1400 -1179 ISRN KTH/MMK/R-06/11-SE

TRITA - MMK 2006:11 ISSN 1400 -1179 ISRN KTH/MMK/R-06/11-SE

|                                                                | TRITA - MMK 2<br>ISSN 1400 -1<br>ISRN KTH/MMK/R                                                                                                                |            |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| X-CT                                                           | Document type                                                                                                                                                  | Date       |

|                                                                | Technical Report                                                                                                                                               | 2006-09-26 |

| MMK<br>Mechatronics Lab<br>Department of Machine Design        | Author(s)<br>Martin Törngren, Dan Henriksson, Ola Redell,<br>Christoph Kirsch, Jad El-Khoury, Daniel Simon,<br>Yves Sorel, Hanzalek Zdenek and Karl-Erik Årzén |            |

| Royal Institute of Technology, KTH<br>100 44 STOCKHOLM, Sweden | Corresponding author: martin@md.kth.se                                                                                                                         |            |

|                                                                | Title                                                                                                                                                          |            |

|                                                                | Co-design of Control Systems and their real-time<br>implementation - A Tool Survey                                                                             |            |

#### Abstract

Increasing needs for optimized designs and for handling the dependencies among control systems and their real-time implementation, cause a resulting need for tools that have the abilities to support design across these traditional discipline boundaries. Tools supporting such co-design provide new opportunities in developing cost-efficient, dependable and robust solutions where the interactions between control and implementation engineers can be improved, and where further possibilities are obtained by increasing the information flow between the control system and the hardware/software platform during run-time. Work on codesign has the important effect to stimulate new theoretical research directions where more work is needed because of the lack of theory and methods in the field. Co-design related to embedded control system is a fairly new area and most of the methods and theory developed so far are aimed at analysis rather than synthesis. A further great challenge is that of model and tool integration, where there are needs to coordinate and integrate the multitude of aspects and specialized models/tools that are used in the development of embedded control systems. This survey sets the context of embedded control systems development describing what is achievable with current generation industrial tools. The context is further elaborated by discussing categories of tools from different related research disciplines. A set of representative co-design tools are then described in depth and discussed.

# Index

| 1 IN | TRODUCTION                                                            | 9  |

|------|-----------------------------------------------------------------------|----|

| 1.1  | REPORT BACKGROUND                                                     | 9  |

| 1.2  | BACKGROUND AND NEEDS                                                  | 9  |

| 1.3  | OPPORTUNITIES AND CHALLENGES IN CO-DESIGN                             | 11 |

| 1.4  | FOCUS, ORGANIZATION AND CONTENT OF THE SURVEY                         |    |

|      | N OVERVIEW OF EMBEDDED CONTROL SYSTEMS DEVI<br>AVAILABLE TOOL SUPPORT |    |

| 2.1  | MODEL BASED DESIGN AND RAPID CONTROL PROTOTYPING                      |    |

| 2.2  | TARGET CODE GENERATION                                                |    |

| 2.3  | ANALYTICAL VERIFICATION                                               | 21 |

| 2.4  | SIMULATION AND TESTING BASED VERIFICATION AND VALIDATION              | 22 |

| 3 T( | OOLS FROM CLOSELY RELATED DOMAINS                                     | 25 |

| 3.1  | HARDWARE-SOFTWARE CO-DESIGN                                           |    |

| 3.2  | MULTI-MODEL DESIGN ENVIRONMENTS AND HYBRID SYSTEMS                    |    |

| 3.3  | DISCRETE-EVENT SYSTEMS                                                |    |

| 3.4  | NETWORKING TOOLS                                                      |    |

| 3.5  | REAL-TIME SCHEDULING AND COMPUTING                                    |    |

| 3.6  | SAFETY AND RELIABILITY                                                |    |

| 4 O  | VERVIEW OF SELECTED TOOLS                                             |    |

| 4.1  | AIDA                                                                  |    |

| Та   | ool Overview                                                          |    |

| Co   | omparative Aspects                                                    | 35 |

| 4.2  | JITTERBUG                                                             |    |

| Та   | ool Overview                                                          |    |

| Co   | omparative Aspects                                                    | 40 |

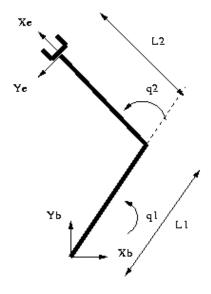

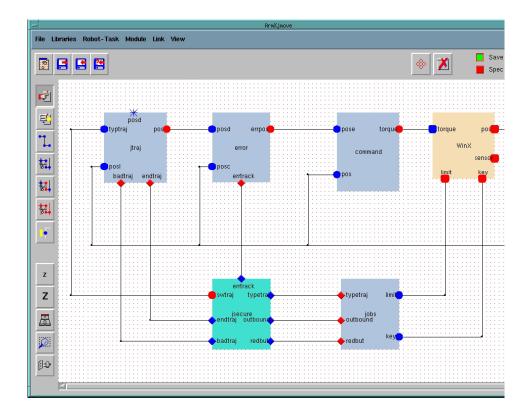

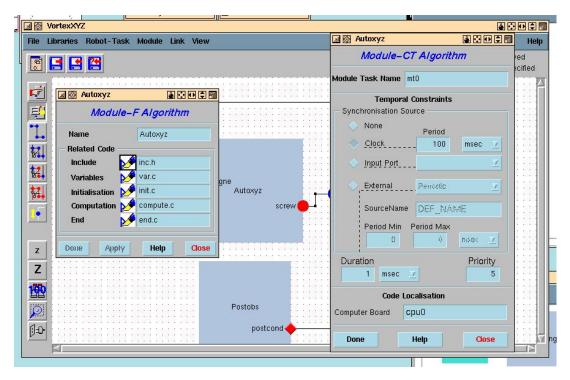

| 4.3  | ORCCAD                                                                |    |

|   | Tool Overview                     | .44  |

|---|-----------------------------------|------|

|   | Comparative Aspects               | .45  |

| 4 | .4 PTOLEMY II                     | .51  |

|   | Tool Overview                     | . 51 |

|   | Comparative Aspects               | . 52 |

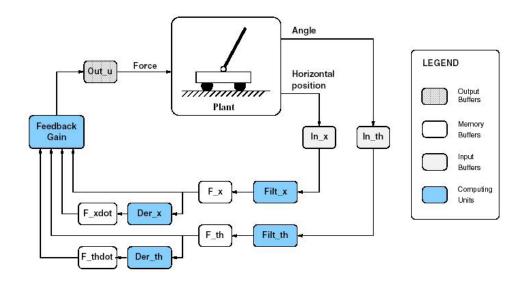

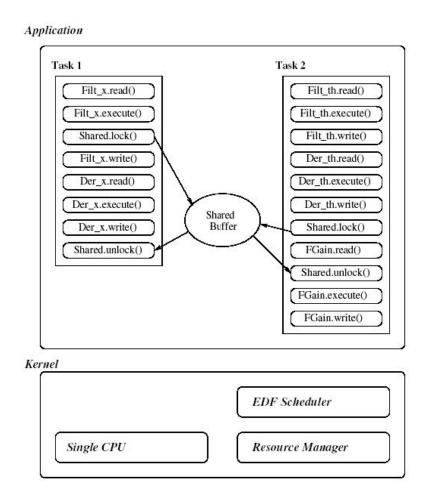

| 4 | .5 RTSIM                          | .55  |

|   | Tool Overview                     | . 55 |

|   | Comparative Aspects               | . 58 |

| 4 | .6 SynDEx                         | .60  |

|   | Tool Overview                     | .60  |

|   | Comparative Aspects               | . 62 |

| 4 | .7 TORSCHE                        | .64  |

|   | Tool Overview                     | .64  |

|   | Comparative Aspects               | .65  |

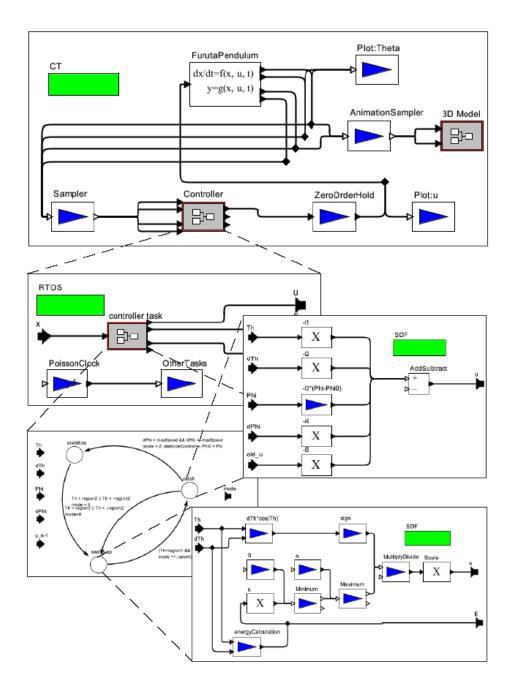

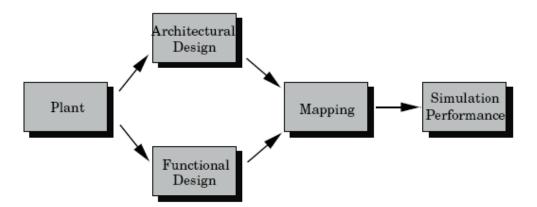

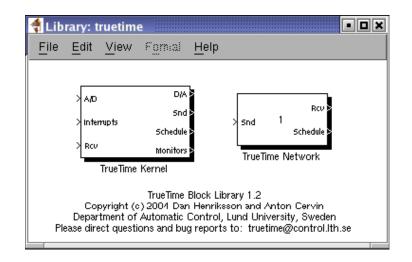

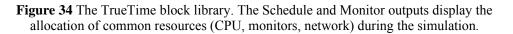

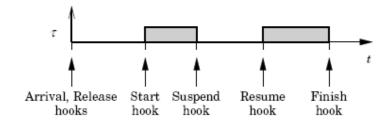

| 4 | .8 TRUETIME                       | .71  |

|   | Tool Overview                     | .71  |

|   | Comparative Aspects               | . 74 |

| 5 | DISCUSSION: TRENDS AND CHALLENGES | .81  |

| 6 | CONCLUSIONS                       | .82  |

| 7 | ACKNOWLEDGEMENTS                  | .83  |

| 8 | REFERENCES                        | .84  |

# 1 Introduction

## 1.1 Report background

This report has been produced as part of the research work carried out by the Control for Embedded Systems Cluster within the ARTIST2 network of excellence [ARTIST2, 2006].

The origin of the report traces back to work carried out at KTH and LTH in work on codesign tools. A first attempt of a tool survey was carried out as part of the Swedish Flexcon project (ending 2005). During the first year of the ARTIST2 project this work was extended to encompass a contextual perspective of industrial tool usage and tools from related domains. During the second year of ARTIST2 this draft report was extended with descriptions of more tools and finalized. A short summary of the report has been published separately [Törngren et al., 2006].

# 1.2 Background and needs

In the early of days of computer control system design, resource constraints were legio. Memory was scarce as was computational performance and accuracy. Failure rates were high and communication rates low. During the 60s-70s the (few) designers working in the area were well aware of the need for co-design of the control systems and its electronics and software implementation; that is, the fact that control design decisions had an impact on the implementation whereas decisions taken in terms of which electronic components to use and how the software was implemented, constrained the control system design. Designers at that time were often responsible for developing both the control system and its implementation, [Motus and Rood, 1994].

Early efforts on real-time implementation environments and code generation can be found in the 1980s in the conferences Computer Aided Control Engineering (often called Computer Aided Control Systems Development, [Control Systems Society, 2004]). As computer-aided engineering tools improved it became possible to support a wider range of tool functionality. Examples of relatively early efforts which in some way address realtime implementation of control systems include

- The Development Framework [Bass et al., 1994], which combined and to some extent integrated control design (in Simulink) with software engineering capabilities using a CASE tool (Software through Pictures)

- The GRAPE tool-set [Lauwereins et al., 1995], developed for digital signal processing systems and supporting distributed systems (allocation, scheduling, partitioning).

- Efforts by Honeywell labs including MetaH and the Parallel Scalable Design Tool-set, [Vestal, 1994; Bhatt et al., 1996]. The MetaH effort has been the basis for further work the Architecture and Analysis Description Language, which now has been standardized by the SAE, [AADL, 2004].

The evolution of electronics and software over the last decades has provided a technology basis making it possible to realize virtually all kinds of control related functionality in different products. Software has become the competitive advantage in embedded control systems allowing unprecedented flexibility. Many examples can be given including the evolution of automotive control systems such as braking control and engine management, the use tracking and focus control in CDs/DVDs (now available per piece at a few dollars cost) to industrial robotics (where software now is the dominating cost in development).

Networking of such embedded control systems have followed the introduction of standalone controllers in a rather rapid pace, being introduced in process control in the 70s, in aerospace in the 80s and in the automotive industry in the 90s. Networking initially had the basic purpose to reduce the cost of installations (reduced cabling, shared sensors, facilitated diagnostics etc.), but once in place, will be used to realize new coordinating of existing subsystems thus creating new functionality. Apart from product internal networks, embedded systems are also increasingly being connected to external systems, for example for maintenance purposes. Again entirely new functionality is possible by such connections, for example coordinating a fleet of vehicles.

In consequence, many computer-controlled systems are today distributed systems consisting of computer nodes and a communication network connecting the various systems. It is not uncommon for the sensor, the actuator, and the control calculations to reside on different nodes in the system. One prominent example of this is modern automotive systems, which contain several embedded ECUs (electronic control units) used for various feedback control tasks, such as engine performance control, anti-lock braking, active stability control, exhaust emission reduction, and cruise control.

While the above mainly shows the possibilities in terms of new functionality and increased performance, this evolution has also drastically increased the complexity of the resulting systems. This complexity has many facets. For example, considering again the automotive industry, a top-of the line car today has some 70 nodes (microprocessor based core entities of the distributed system) which are delivered by some 30 vendors. Within the individual nodes in the networked control loops, the controllers are often implemented as one or several tasks on a microprocessor with a real-time operating system. Often the microprocessor also contains tasks for other functions, e.g., communication and user interfaces. The operating system uses multiprogramming to multiplex the execution of the various tasks. The CPU time and the communication bandwidth can hence be viewed as shared resources for which the tasks compete.

Pursuing the use of embedded control systems further thus requires efficient complexity management. The traditional separation of engineers into different disciplines is closely related to the increasing complexity but the division into disciplines can also create problems. For control systems, the typical separation between control and implementation engineers makes it important to define and appropriately handle design issues that have an impact across these domains. Issues such as control bandwidth and computational structure vs. choice of processors and processor scheduling will affect, and be dependent, on each-other. Ineffective support for communication and analysis across the domains covered by the disciplines may not only cause lengthy and costly iterations but also later product failures with even more serious consequences.

In addition, there is a strong trend within industry today to use commercially available information technology and commercial-off-the-shelf (COTS) components deeper and deeper in the real-time control systems. These components have restricted configurability and may not be well suited for control systems. Limited resources combined with non-optimized hardware and software components introduce non-determinism in the real-time system. Digital control theory normally assumes equidistant sampling intervals and a negligible or constant control delay from sampling to actuation. However, this can seldom be achieved in practice in a resource constrained system. For control systems this is of particular concern. Timing variations in sampling periods and latencies degrade the control performance and may in extreme cases lead to instability. Tough product demands in terms of competition and legislation will moreover cause a need for optimizing system designs where the trade-offs (and design issues) at hand, e.g. control performance vs. word-length/price of processor, will affect more than one engineering domain. The needs for optimization are particularly relevant for large series production where the goal is to make the hardware cost proportion as small as possible. Typical examples are provided by the automotive industry which try to squeeze control functionality onto as small microprocessors/controllers as possible.

Co-design is also required for emerging highly safety-critical applications such as steer and brake by wire. The traditional approaches for achieving highly dependable systems are not really viable here because they are so costly; instead there is a need to combine application and computer system measures in order to develop cost-efficient dependable computer control systems – i.e. co-design between the control system and its implementation is required.

Optimization of the control system implementation will have the effect that resource constraints appear, constraints that to be properly accounted for during control design. Constraints can also occur in products with smaller series. This is for example the case in novel applications such as wireless distributed systems where power and communication constraints will affect the control system design.

All in all there is consequently an increasing need for tools that support co-design of control systems with their electronics and software implementation. For optimal use of computing resources, the control algorithm and the control software designs need to be considered at the same time, or alternatively, given the constraints of e.g. a COTS based platform, the imperfections it provides has to be taken into account in the control design.

## 1.3 Opportunities and challenges in co-design

There are many instances of the control / computer implementation co-design problem. These can typically be formulated as optimization problems; consider the two following examples: Control and scheduling co-design problem: *Given a set of systems to be controlled and a computer with limited computational resources, design a set of controllers and schedule them as real-time tasks such that the overall control performance is optimized.*

Control and cost co-design problem: Given a set of systems to be controlled and control performance specifications for these, choose an implementation in terms of a distributed computer system including deciding the allocation of control functions, their partitioning into tasks, scheduling and triggering, such that the overall production cost is minimized while guaranteeing the specified control performance.

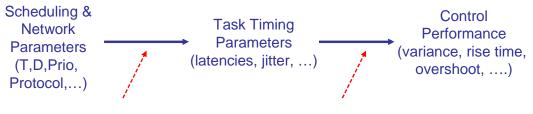

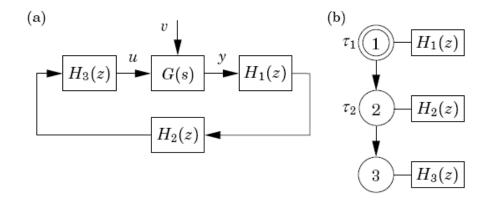

A major challenge, however, in solving these types of optimization problems is that the relations between the involved parameters are non-linear and sometimes even difficult to formulate, see FIG. 1 which illustrates some of the relationships. Although confined optimization problems can be formulated, and sometimes also solved analytically, real problems are even more complex and typically involve optimization of several variables. In realistic settings, the support of simulation and what-if-type analysis is therefore an important approach.

Complex relationship

Complex relationship

Figure 1. Complex relationships between control system qualities and computer system design parameters

As outlined above, there are many variants of the co-design problem and thus problems that tools can be targeted to solve.

Whereas the co-design takes place during system development it can target both design time optimization as well as the design of on-line interactions, for example, dealing with re-configuration in order to handle changing conditions such as changing loads or partial system failures. The definition of the division of responsibilities and the information flow, required during run-time, between the controller and the platform is an important part of the co-design work. Examples of such issues include the determination of where to detect certain conditions such as e.g. a computational failure; should this be the responsibility of the platform or the controller? Where should the resulting error handling be placed?

A key challenge for the implementation of control systems is that of trying to define the appropriate abstractions and their dependencies with discipline specific design parameters (compare with FIG.1). Experiences have shown that research into an interdisciplinary area such as control/computer co-design can help to identify the gaps

between different theories and stimulate entirely new research directions, [Törngren et al., 2001].

# 1.4 Focus, organization and content of the survey

The main focus in this survey is on tools that provide a bridge between the domains of control function and computer system design in that they allow

- one or more trade-offs to be resolved (e.g. cost vs. performance),

- constraints, on behalf of the control or computer system, to shape the design of the other.

Examples of issues involved include from the control side

- choice of controller synthesis method (e.g. taking robustness and compensation with respect to computer system deficiencies into account)

- algorithm computational requirements (e.g. types of arithmetics required

- resulting memory requirements (code and data, volatile-/non volatile storage)

- algorithm structure and information flow (causing data and control flow requirements)

- control design (causing accuracy requirements in computation as well as requirements on assumed timing; delays, periods and admissible jitter)

-

and from the computer system side

- choice of hardware components (affecting cost, quantization in computations, and basic communication and computational speed)

- the choice of networking protocol

- the software logical structure, partitioning into tasks

- the overall execution structure of the system (including the triggering of actions, synchronization and scheduling determining the actual timing of the system).

In addition, certain decision and issues lie in-between these traditional views, for example the allocation of control functionality to computational elements. The execution time of a particular control system function will also depend both on the controller design as well as on the implementation method including the software/hardware platform. Other, noncontrol related functionality, also has to be considered since it can have an impact on for example the system timing.

The focus in the survey in terms of the product life-cycle is on tools that support system design related to modeling, analysis and synthesis. The emphasis is on "upper case" tools - i.e. tools that support design at the conceptual level of function and implementation architecture design. A further delimitation is that the types of analysis in main focus are related to the run-time behavior of the system (e.g. control system, timing behavior and power consumption) – as opposed to non-run time properties (typically more purely structurally related) such as maintainability and hardware reliability.

A challenge in this survey is that fact that the area is very dynamic with new tools frequently emerging and that there are already a multitude of existing tools that in one way or the other support co-design. While academic tools often are dedicated to one or a few tasks, commercial tools often support a wide range of design tasks that may span a large portion of the system development.

The tools chosen for the given focus have in common that they directly support co-design of control systems and their implementation in terms of being able capture the appropriate models, analyse dependencies related to trade-offs and/or capable of constraints based synthesis.

Tools that support a one way synthesis from control specification to implementation, without explicitly (or weakly) formulated constraints or dependencies, are not covered in the survey part, thus for example excluding pure rapid prototyping systems. Generic tools that do not explicitly support control systems have been excluded from the survey. In addition, for tools that have a basic ability for co-design but where there are add-ons that provide much more interesting capabilities, only add-on tools are covered (one example of this is Matlab/Simulink<sup>1</sup> which is not included by itself but rather indirectly since some of the chosen tools are based on it).

The tools chosen for the survey should finally not be seen as exhaustive, but rather as highly representative for the given focus.

The following tools are included in the survey:

- AIDA from the Royal Institute of Technology, Sweden.

- *Jitterbug* and *TrueTime* from Lund University, Sweden

- Ptolemy II from the University of Berkeley, California

- RTSIM from the RETIS Laboratory, Pisa, Italy

- SynDEx and Orccad from INRIA, France

- TORSCHE from the Czech Technical University in Prague

The tools included in this report approach co-design of real-time control systems in different ways, with specific design scenarios and concerns in mind. Some of the tools, such as TrueTime and AIDA, are specially tailored towards control and real-time co-design, whereas for others, such as Ptolemy II, the real-time control systems simulation is just one part of a larger framework. The abstraction level ranges from a very high level of abstraction of the distributed computer system in terms of time-varying delays, jitter in periods and transient faults, to detailed architectural models, as in TrueTime and RTSIM, that actually mimic the operation of for example an RTOS. Some of the tools are more directed towards synthesis, e.g. in terms of code generation such as ORCCAD, but also for the assignment in space and time of control functions, the case for SynDEx and TORSCHE. Finally, the tools also have an origin from different disciplines, but all have been extended to cater for control and computer system co-design.

<sup>&</sup>lt;sup>1</sup> From the Mathworks: http://www.mathworks.com

As an aid to the reader, and also to be able to relate the chosen focus area to other related tools, the survey begins in Section 2 with an overview of control systems development and the functionality that is provided by existing high-end commercial tools. As a further contextual outlook, Section 3 gives an overview of closely related domains with which there are some connections to the tools discussed here. Several examples of tools are given in Section 3, where the reader will note that these tools often are on the boarder-line to the area of co-design treated in this report; examples of such tools include AIRES (from the Univ. of Michigan), Sildex (from TNI), the TT-Tech tool-suite (from TT-Tech) and CAMeL-View (developed at the Univ. of Paderborn, now available as a commercial tool).

Section 4 contains the survey of the above mentioned tools. Finally, Section 5 discusses their characteristics and outlines trends and challenges in the further research and development of co-design tools.

A complementary description of the area of co-design is given in the corresponding Roadmaps by the ARTIST2 Control for Embedded Systems Cluster, [ARTIST2 Control cluster roadmaps, 2006]. These roadmaps are available on-line<sup>2</sup> together with other publications produced by the cluster.

Other useful surveys and roadmaps include the

- Handbook of Networked and Embedded Control Systems [Hristu-Varsakelis and Levine, 2005], which indirectly describes a number of related tools and many of the concerns involved in co-design.

- ARTIST roadmaps [Bouyssounouse and Sifakis, 2005], describing the needs in many application domains and giving examples of tools and their functionalities.

- The COLUMBUS project survey on modeling and tools for hybrid systems [Carloni et al., 2004], giving an overview of tools dedicated to hybrid systems.

<sup>&</sup>lt;sup>2</sup> Publications by the ARTIST2 Control for Embedded Systems Cluster: http://www.md.kth.se/RTC/ARTIST2/publications.html

# 2 An overview of embedded control systems development and available tool support

The strong market demands, an increasingly competitive pressure and the increasing system complexity are driving and making the use of powerful tool environments ever more important.

Control engineering has a strong tradition in model based development, using well founded mathematical concepts for describing the plant to be controlled, the control systems as well as disturbances affecting the plant and sensors. Control engineering models are used to communicate designs among developers (within and in-between companies), for system analysis as well for synthesis. However, industrial adoption and practices still vary to a great extent. Some industrial domains are characterized by control theoretic and model based approaches supporting the development. Other domains, however, such as automotive engine control, rely heavily on look-up tables and calibration of systems for control purposes – i.e. there is less of a tradition of model based control.

The maturity of model based development thus varies a lot but is in general more developed in "Control for embedded systems" compared to "software development for embedded systems". Many domain specific traditions are also in place as mirrored by the wide variety of specialized modelling languages and tools, see e.g. [Bouyssounouse and Sifakis, (2005), and Törngren & Larses (2005)].

The development and tools discussed in this section represent the more advanced model-based development practices that can be found in industry. This section provides an introduction to representative capabilities provided by existing commercial tools, including their support for

- system modeling and design

- rapid control prototyping (RCP), allowing control designs to be quickly prototyped using general purpose controller hardware

- analytical verification of system properties

- code generation from control system models including analysis of quantization effects, e.g., relevant for fixed-point implementation

- testing of generated code and final implementations

Other important capabilities supported by many tools, but not covered in this report, include the calibration of target systems (e.g., over CAN, where for example control parameters and look-up tables can be fine tuned and the control performance analyzed on-line) and configuration management, providing versioning and change management of for example design models, tests and components.

The above listed functionalities are not distinct and can thus be used in different development stages and the functionalities to some extent also overlap. They are briefly described in the following sections.

There exist a large number of tools that support more or less of the above sketched functionality. The tools can differ in the modeling paradigms provided (e.g. continuous-time, discrete-time, vs. discrete-event) and in the provided analysis and synthesis support. The most common type of analysis is that of simulation based

testing; examples of several forms of testing are given in the following sub-sections. Many tools support some form of code generation where two types can be distinguished; code generation for rapid prototyping vs. for production systems. In the former case, there are less stringent requirements on the code generator since prototyping systems typically constitute resource adequate systems, i.e. systems with more than plenty of execution and memory resources. For production code generation there are additional requirements which require more elaborate optimization of the use of execution and memory resources.

Examples of tools that support a larger portion of the above mentioned functionality include the tool chains provided by the companies Mathworks<sup>3</sup>/dSPACE<sup>4</sup>, Etas<sup>5</sup> and Esterel Technologies<sup>6</sup>.

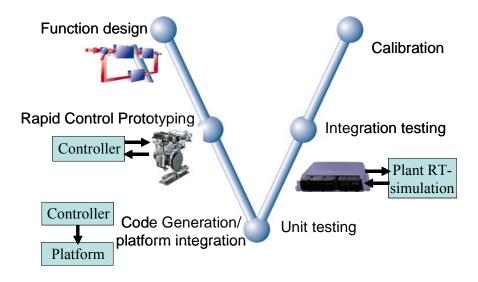

Systems development is often depicted using different process models. The V-model, illustrated in FIG. 2, is such a model, which is commonly used although it is highly simplified.

**Figure 2.** The V-cycle model of control system development, illustrating the use of tools that support various design activities, from early modeling and simulation to hardware in the loop testing.

The V-model does not, for example, illustrate the iterations part of the development and the dependencies that exist between different development stages. The simplifications part of the V-cycle can also be seen by considering tasks that have to be part of control system development. Examples of such tasks include

- Defining initial requirements and constraints

<sup>&</sup>lt;sup>3</sup> http://www.mathworks.com

<sup>&</sup>lt;sup>4</sup> http://www.dspace.com

<sup>&</sup>lt;sup>5</sup> http://en.etasgroup.com/

<sup>&</sup>lt;sup>6</sup> http://www.esterel-technologies.com/

- Defining and planning the development project including choosing supporting tools

- Deciding the control design approach and performing the control design

- Choosing sensors and actuators

- Choosing the computing platform (software and hardware)

- Mapping the control design to the computing platform

- Verifying that the requirements are satisfied by the implementation

- Validating that the solution actually meets stake-holder needs

- Fine tuning the final implementation by calibration

It is clear that all these steps are interdependent and that many different approaches are possible in ordering and/or parallelizing these tasks.

#### 2.1 Model based design and rapid control prototyping

Typical for modern tools is that they support graphical specifications of control functionality. Classical methods of control theory can be used to identify and optimize the control characteristics of the function. As the graphical specifications provide an executable semantics, the control function can be simulated, either by stimulating it with appropriate input values or by having the function in a closed loop with plant and environment models. The graphical specifications include basic components or model elements which can be hierarchically decomposed. In describing the behaviour of each component there are typically several alternatives; a native behavior description can be used (for instance using pre-defined transfer function or state space components) or the behavior of the component can be defined by encapsulating programmed algorithms (e.g. coded in C-code). The components can be treated as white or black boxes.

Furthermore, the graphical specification of the control function can be extended by an appropriate I/O interface specification; in practice these specification are just other components that include code that directly can access I/O devices. The resulting model can be compiled (where code is generated) and executed either on a PC directly or on a separate real-time hardware, each providing connections with the actual controlled system. This stage is called rapid control prototyping. It is an established method for fast design iterations.

In these early stages of the development process a control engineer will usually focus on the functional and behavior of the control function but not on details of a later software implementation on an electronic control unit. Modeling guidelines are important to ensure proper use and maintenance, but can also be required to ensure the proper behavior and the generation of efficient production code.

The design models form a basis for communication, analysis and code generation. Code generation and some specific analysis techniques are described in the following.

#### 2.2 Target code generation

The use of code generation has increased significantly only over the last few years [Reuter et al., 2004]. There are several motives for introducing code generation in the first place including reducing the development time, ensuring consistency among

models - code - and documentation, reduction of programming faults, and ease of porting.

Important requirements on code generation technology are on the other hand to ensure

- efficiency in terms of memory and speed, and

- dependable code generation, providing testing and analysis techniques to ensure that the generated code behaves as intended

Using this technology, a control engineer will deliver an executable graphical specification as a reference for further simulations and as a basis for the generation of code for implementation.

Efficient code generation means that a minimum of execution time, RAM and ROM resources as well as stack size is required to run the code on an embedded processor. This minimizes chip size and costs. But production-quality code generation involves more than just these benchmarks. There are soft criteria that are equally important, including human readability of the code, traceability between code and model and target awareness of the code. Modern code generators typically support also the automatic generation of the software documentation.

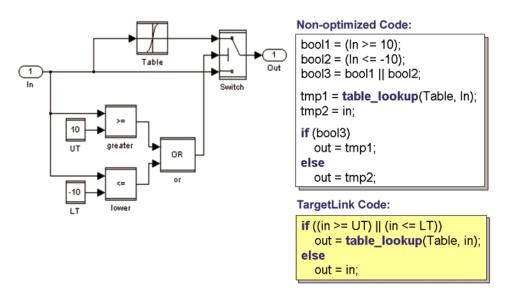

Code generators use a range of techniques to meet such requirements including standard and inter-block optimizations and the use of code pattern libraries. For reasons of efficiency, some production code generators also have the ability to perform processor- and compiler-specific optimizations. FIG.3 illustrates the difference between optimized vs. non-optimized code-generation.

Figure 3. Code generation example; from Simulink to C-code (Courtesy of dSPACE).

Dependable code generation is closely related to the provision of complementary facilities for ensuring that the generated code is correct. For example, even though the control system model may have been verified, bugs in code generators, compilers and even hardware can cause erroneous behaviour. Examples of available testing environments supporting the progression and profiling, from models to implementation, are given in section 2.4.

In the context of this report, it is interesting to note that a code-generator in effect provides an interface between control designers and implementation engineers; it can thus serve as a co-design tool. This is particularly the case for the types of problems considered in this report, where resource constraints appear.

A control system design could in the simplest case correspond to a few discrete-time equations. In practice, a controller contains both state machine logic and such equations. In transferring such a control system design to software there are many decisions to be made and many trade-offs are possible. It is often desirable to minimize the required amounts of memory (e.g. allowing only on-chip memory to be used) and to reduce the execution time of a given algorithm (reducing the delay from sampling to actuation). At the same, it is desirable to use a cheap processor while providing the accuracy needed for computations. Unfortunately, these requirements are contradicting. While reduced memory consumption can be achieved, it typically comes at the cost of increased execution time and reduced accuracy. While execution times of algorithms can be reduced, this in turn typically requires more memory and reduces the accuracy of requirements, etc. Full automatic code generation is very difficult unless some of these constraints can be relaxed.

An example of a code generator that support designers in dealing with such trade-offs is Targetlink from dSPACE. In doing so, the tool provides support for evaluating control performance, execution time and memory consumption for given implementations in terms of choices of variable sizes, scaling of variables etc. For fixed point processor implementations, Targetlink supports scaling tasks and automation wherever possible.

#### 2.3 Analytical verification

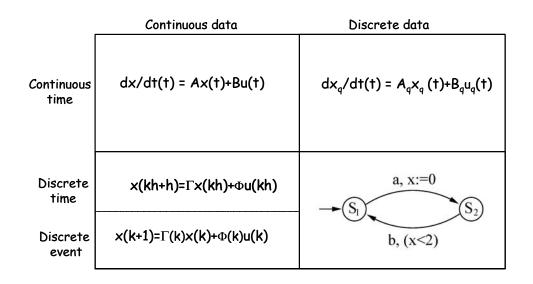

There are several theoretical approaches towards analytical verification of control systems. These approaches are strongly linked to the types of models, or models of computation, that they are developed for. As illustrated in Figure 4, these models could be characterized in terms their notion of data and time. Control theoretic approaches are strong in handling continuous time data and continuous time, for example allowing formal model based analysis of robustness and stability with respect to sensor noise and defects (or just modeling errors) in the controlled plant. The theory is also well developed for period (time-triggered) discrete-time systems whereas there is less work addressing discrete-data (quantization) and even less so for discrete-event systems, [ARTIST2 Control cluster roadmaps, 2006].

More recently, formal techniques with a computer science background have also been made available within in control engineering tools or by exporting models to other tools providing such facilities. Such techniques are applied to the discrete-event system parts (lower right hand part of Fig. 4) of control systems, see e.g. Ranville (2004) and the ARTIST roadmap, [Bouyssounouse and Sifakis, 2005]. The term 'model checking' was introduced in the early eighties. The capabilities of the technology have advanced significantly over the years, and it is now, for example, commonly applied in the area of hardware verification. Model checking is a technique that relies on building a finite state machine model of a system of interest and checking that a desired property holds in that model. One example of the type of

question that can be addressed is as follows: Can the ABS feature be requesting a decrease in engine torque at the same time as the cruise control feature is requesting an increase in engine torque? The use of model checking then requires formulating this type of requirement in the provided formal specification language and a system model that is amenable to analysis.

**Figure 4.** Model categories according to how data and time are represented. Theoretical approaches are less well developed for hybrid systems, where different models are mixed (e.g. a system containing several continuous systems where the connections and activations between them is controlled by a state machine).

A central problem in applying model checking is the scalability of the techniques, suffering from very large state spaces. This problem becomes even more cumbersome when dealing with embedded control systems that are composed of variables, continuous in both range and time, and incorporating a mixture of discrete-event and continuous time systems. Moreover, there has most probably also been a lack of training and in developing appropriate user interfaces. In adopting this technology, methodology and model extraction become important, to actually address the most relevant problems (subsystems, functions) and at the right level of abstraction. The use of such tools is right now emerging in embedded control systems and there is plenty of research in attempting to extend the technology, ([Bouyssounouse and Sifakis, 2005], [Carloni et al., 2004]).

#### 2.4 Simulation and testing based verification and validation

The model-based development approach also brings new opportunities to perform tests<sup>7</sup> at various stages within the development – not only at the end after having built the actual system.

<sup>&</sup>lt;sup>7</sup> Note that the use of the word testing here encompasses tests performed on models, physical systems/components or a combination thereof.

As soon as a model for the control function, a plant model and models of other pertinent aspects of the environment, such as disturbances, are available these models can be used in a closed control loop. The strength of testing through simulation is (at least) four-fold:

- There are few limitations in the types of systems that can be tested, e.g. works for non-linear systems and for hybrid systems

- The test conditions can be well defined and the tests are repeatable

- The tests can be automated.

- The tests can support a wide variety of purposes including verification in early development stages as well as analysis of failures during maintenance.

A corresponding challenge is that of defining relevant test scenarios and also in appropriately managing the test process. However, once such an environment is set up, it can be reused, not only for other systems/products but also incrementally during development. It is for example today common to support so called software-in-theloop (SIL) simulation, where the basic setup is the same but where the control function part of the model has been replaced by the corresponding production code. The behaviour of the production code can then be compared with the behaviour of the function model.

A final step in testing is so called hardware-in-the-loop (HIL) simulation. Here, the real control unit is embedded within a testing environment that typically contains real-time simulation, electrical components emulating parts of the environment and some real physical components. Real-time plant models are required for realistic simulations. HIL simulation covers a brought range of test procedures, including

- correct interaction of networked components,

- test of diagnostic functions and communication,

- electrical fault simulation,

- simulation of not yet existing control units, so-called rest-bus simulation, systematic generation and injection of electrical and logical faults.

#### 3 Tools from closely related domains

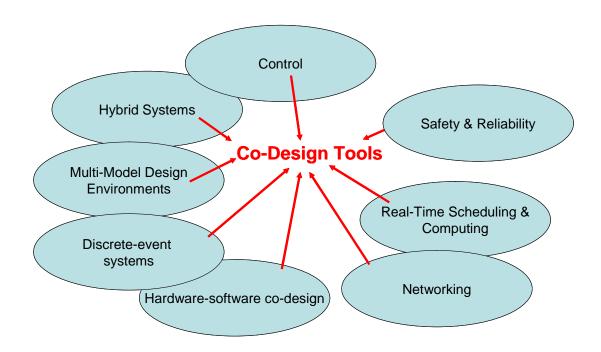

There are many areas and disciplines with tools that have some relation to the type of co-design tools being studied in this survey. FIG. 5 outlines a number of related areas. The characterization is for illustrative purposes mainly but does indicate that the areas are more or less connected and overlapping (all overlaps are not shown!). The purpose of this section is to briefly outline some these related areas and their connection to the tools studied in this report. Some examples are given. The tools covered in section 4 originate from several of the communities shown in FIG. 5.

**Figure 5.** Sample research areas/disciplines with tools with some relation to the co- design of control systems and their implementation. Note that several of these areas address other dimensions of co-design.

#### 3.1 Hardware-software co-design

Tools from the area of hardware-software co-design have many similarities to the types of tools studied in this report, where the main difference is the type of functionality considered (control functions vs. more or less general software). In common are the goals to provide support to designers that assist in mapping functionality to a platform while highlighting relevant trade-offs.

Tools in this area often utilize hardware/software modeling languages such as SystemC and VHDL, which can be seen as a kind of high-level languages including concurrent behavior. There are several examples of commercial design environments (such as those from companies like Xilinx<sup>8</sup>, Cadence<sup>9</sup> and Mentor<sup>10</sup>) that provide integrated design environments where both software and hardware, and the mapping of software onto the hardware, can be specified. The area is intensively evolving.

An interesting research project in this category is Metropolis<sup>11</sup> which has the aim to support design from specification to implementation on hardware and software platforms. Two important parts of Metropolis are its methodology and meta-model (tools are also available). The meta-model serves the purpose to allow different models of computation to be defined. The meta-model allows behaviors to be defined using the basic capabilities of actions, constraints, and their refinements. Quantity constraints enable the specification of performance and cost constraints such as time and power (more information on Metropolis is available in the Hybrid systems tool survey, [Carloni et al., 2004]).

#### 3.2 Multi-model design environments and hybrid systems

Very closely related to hardware-software co-design area, is that of multi-model design environments. A typical example here is Ptolemy II. Ptolemy enables the definition of several model of computation, their assembly as a number of concurrent components and finally the definition of how these heterogeneous models interact. Ptolemy is described in more detail in section 4 since it provides pre-defined models of computation supporting co-design.

There are also modeling languages that in themselves provide a multitude of structural and behavioral descriptions. Examples in this category include UML2 and the AADL. While the UML was initially intended for general purpose software systems, work is being undertaken by the OMG<sup>12</sup> to provide more capabilities for non-functional aspects, e.g. for describing timing behavior and fault-tolerance, by defining UML profiles (an overview of some of these activities are provided in the ARTIST roadmaps, [Bouyssounouse and Sifakis, 2005].). The AADL on the other hand is a language dedicated to support the implementation of control systems, [AADL, 2004]. The AADL standard was developed based on the MetaH effort. A somewhat similar but broader effort is the development of the EAST-ADL, a description language for automotive systems [EAST-ADL, 2004] with some relation to the Autosar<sup>13</sup> initiative. Both the AADL and the EAST-ADL provide constructs and properties required for analysis of safety, reliability and timing, as well as explicit models of software components.

A closely related and partly overlapping area is that of hybrid system tools. These are tools specialized in the modeling, simulation and formal analysis of systems composed of continuous and discrete event systems (manifested by combining differential equations with state machines). There are many tools that provide some support for hybrid systems (and possibly also other models of computations).

<sup>&</sup>lt;sup>8</sup> http://www.xilinx.com/

<sup>&</sup>lt;sup>9</sup> http://www.cadence.com/

<sup>&</sup>lt;sup>10</sup> http://www.mentor.com/

<sup>11</sup> http://www.gigascale.org/metropolis/

<sup>&</sup>lt;sup>12</sup> http://www.omg.org/

<sup>&</sup>lt;sup>13</sup> http://www.autosar.org/

Example tools include Matlab/Simulink with Stateflow, Modelica/Dymola, Sildex and HyVisual. See [Carloni et al., 2004] for an excellent survey of hybrid system tools.

Control systems are more or less intrinsically hybrid systems. However, whereas the hybrid community studies the behavior of interacting continuous and discrete event subsystems, the co-design tools surveyed in this report focus on the interaction between the control system and its implementation. These types of tool categories therefore strongly complement each-other. However, it is often feasible to develop support for co-design functionality on top of the capabilities provided by hybrid system tools. An example of this is Matlab/Simulink from the Mathworks on top of which for example the TrueTime tool is built, further described in section 4.

Many of the hybrid system tools provide code generation. Some also provide explicit support for embedded systems design and in this sense contain ingredients from several of the above mentioned areas. As an example, consider Sildex, a tool-set for formally specifying and designing control and data-oriented real-time embedded systems. Sildex (which is produced by TNI<sup>14</sup>) targets safety-critical embedded software applications and is based on the synchronous language Signal. To describe each component, the user can choose from different styles: data-flow style, state machines, truth tables, or Grafcets. It is also possible to import Simulink diagrams or to write components in the C language.

The Sildex environment conforms to the description of model based design in Section 2.1 in supporting graphical components, their connections and hierarchy. Sildex provides two features for validating a specification diagram. Through simulation it is possible to execute the embedded code generated by the compiler and to study the evolution of the program's state machines and data flows. As a complement, there is a formal proof mechanism of safety properties (analytical verification of state machines as mentioned in Section 2.3). Code generation is support from the models to C and ADA code.

An advantage of Sildex is its foundation on a mathematically well defined language, facilitating the application of various analysis and synthesis techniques. The current focus of SILDEX is on embedded software design and the tool lacks the capability of modeling generic hybrid systems, [Carloni et al., 2004]).

Finally, another class of related efforts are those that instead focus on the integration of different domain tools and/or the management of the superset of information treated by different tools. In systems development there is for example the need to manage the dependencies and to provide traceability between related information artefacts, from requirements documents/models, over designs to implementation. There may also be the need for stronger interactions between domain models, for example the need to support co-simulation between tools describing different behaviors (communication entities) and to support the allocation of functional (or software) models to hardware, when these are described in different tools. A typical scenario is also when a particular design model, e.g. a functional behaviour model, contains basic information that is required for many different types of analysis (e.g. allocation as described above, for safety analysis such as FMEA, or for formal verification purposes). In many cases there is a need to provide model

<sup>&</sup>lt;sup>14</sup> http://www.tni-world.com/

transformations, decide on appropriate model exchange formats and to deal with tool APIs. Representative model integration approaches, and their relation to multi-domain modelling languages are surveyed by [Chen, et al., 2006].

An example of a multi-domain tool environment for mechatronics products and with an emphasis on product development is CAMeL-View. It provides an interactive way to build up models of complex mechatronic systems which include different system domains, such as multi-body, hydraulic, control-engineering and discrete systems. With CAMeL-View the developer is supported by an extensible database comprising predefined components which is similar to Matlab/Simulink. The integration of models taken from Matlab/Simulink and other tools is also supported. For today's design it is also important to include the 3-D graphical description which is a core feature of CAMeL-View. The graphical description can be imported from numerous CAD systems, like OpenInventor, VRML, DXF or IGES. They are reduced automatically for animation purposes. For the analysis the specific model can automatically be transferred to a mathematical representation and to optimized C code especially for real-time simulation and Hardware-in-the-Loop applications. Besides this, CAMeL-View allows to export the model to Matlab/Simulink as an mdl-file including s-functions [iXtronics, 2006].

#### 3.3 Discrete-event systems

This class of tools focuses on event-triggered dynamic systems. In this category there are tools both from the control system community as well as from the computer science community, sometimes allowing limited modeling and analysis of hybrid systems. There are also related tools developed within the Petri Net community.

The tools typically provide simulation, while some of them also provide facilities for formal reasoning about so called liveness and safety properties. A liveness property refers to a condition that will eventually come true. A safety property is a hazardous condition that is desirable to avoid; formal analysis of safety properties can thus be very important for systems with strict safety and reliability requirements (this type of verification is strongly related to analytical verification as disussed in Section 2.3).

There is a multitude of tools supporting discrete-event systems including UML tools and some control engineering tools (e.g. Stateflow as part of Simulink). Extensions of pure state machine formalisms to handle time include timed automata. Timed automata have been used for modeling hybrid systems and real-time systems. It is possible to use such automata for modeling the environment, the application software as well as the system platform. Timing analysis problems can be formulated and solved using model checking [Bouyssounouse and Sifakis, 2005].

Discrete event systems are often used as a basis for developing application specific modeling and analysis capabilities, for example for analysis of network protocols or real-time software. In some cases they have also been extended to included continuous-time modeling capabilities.

#### 3.4 Networking tools

There is a broad range of tools that support modeling and analysis in the area of networking. One class of such tools is typically built upon discrete event simulators,

making it possible to model and simulate the behavior of communication protocols. One example of such a tool is NS-2, frequently used in telecommunication applications.

Networking simulators have been extended to incorporate continuous dynamics (to model plants), thus effectively reaching into the hybrid systems area. There is a close relation to the real-time scheduling and computing area; when dealing with distributed systems the approach taken with resource management (e.g. scheduling) has to cater for both computing and networking resources. This area covers those approaches with a starting point from the network.

Other tools under this heading are dedicated to the configuration of communication systems, including signal interfaces, protocol handling of data and communication scheduling. Examples in this category include tools from Volcano communication technologies<sup>15</sup>, Vector Informatik<sup>16</sup> and TT-Tech<sup>17</sup>.

As an example of tools supporting networks, and in particular distributed systems design, consider the tool-chain provided by the company TT-Tech. This primarily targets distributed systems that are based on the so called Time Triggered Protocol (TTP). The tool-chain also provides an interface to Simulink from the Mathworks.

Once the control application is designed and tasks are assigned to the nodes of the system, the TTP communication messages that need to be exchanged must be defined. The designer completes the cluster design process by configuring the communication system (e.g. TDMA round duration, transmission rate, type of communication controller). All design data created above can subsequently be used by the cluster design tool for TTP-based systems. This tool constructs the TDMA communication schedule and stores it in a message descriptor list which includes the entire configuration of the communication schedule. This configuration is loaded into the communication algorithms of the subsystems into tasks and specifies them. Configurations for certain operating systems can also be defined. It is then possible for the designer to invoke a Simulink code generator to produce application code for the tasks and to download it.

#### 3.5 Real-time scheduling and computing

In the real-time research community, a number of tools have been developed for modeling and analysis purposes. These tools allow multi-tasking systems, and sometimes distributed systems to be modeled and their timing behavior to simulated, analytically assessed or schedules to be generated. For early examples of such tools see Audsley et al. (1994) and Storch and Liu (1996). An example of a more recent tool from this area that has been extended continuous dynamics capabilities is the RTSIM tool, described in more detail in section 4.

When dealing with distributed systems, there is also a need to define the allocation of functions to the nodes of the system and the partitioning of this functionality into

<sup>&</sup>lt;sup>15</sup> http://www.mentor.com/products/sm/volcanoautomotive/

<sup>&</sup>lt;sup>16</sup> http://www.vector-informatik.com/

<sup>&</sup>lt;sup>17</sup> http://www.tttech.com/

tasks. The AIDA tool-set is an example of a tool that supports such architectural design and that moreover has been integrated with control design tools in order to evaluate the resulting control performance. The AIDA tool-set is described in section 4.

AIRES<sup>18</sup> - Automatic Integration of Real-time Embedded Software – is a tool prototype developed within the MOBIES project at the University of Michigan. AIRES was developed to support the analysis of timing and schedulability of embedded software. The tool also has some synthesis capabilities.

In the AIRES tool, the embedded software under development is represented with a component, software architecture and run-time model. The AIRES tool can be used either as a stand-alone analysis and design assistance tool or along with other design tools. The implementation of AIRES includes a graphical modeling environment, a meta-model, and analysis packages. The Generic Modeling Environment (GME) was chosen as the graphic modeling environment for AIRES. The meta-model is implemented as a modeling paradigm in GME and exported as an XML file for sharing among different tools. The analysis algorithms perform component allocation, timing assignment, priority assignment, schedulability, and end-to-end response time analysis. In the prototype, interfaces to design models in Rational Rose and Matlab Simulink/Stateflow have been implemented. Two flavors of the AIRES tool have been implemented: one for avionics applications and one for automotive applications

Another approach to real-time systems programming is represented by Giotto [Giotto, 2003]. Giotto as well as xGiotto have been developed at UC Berkeley from 2000 to 2004, see [Giotto, 2006] for links to a number of papers on Giotto and its tools.

GIOTTO focuses on distributed embedded control systems and as a programming language has a basis in the notion of logical execution time (LET). Giotto programs connect periodic software tasks to sensors and actuators, and specify the exact times when sensors are read and actuators are updated, independently of the number, speed, and utilization of host computers. The duration from reading a sensor to updating an actuator is referred to as the LET of a task if the task is connected to that sensor and actuator. Equivalently, the LET of a task determines the time the task executes logically, i.e., the time the task takes from reading input to writing output, independently of the time the task actually computes. The execution of Giotto and LET programs in general is correct (time-safe) if all tasks compute in real time less or equal than their LET. The LET semantics explicitly distinguishes logical from physical task execution in order to trade off average-case performance for determinism. Even if a task computes in less than its LET, its output is delayed until its LET has elapsed. In the LET paradigm, more and faster host computers will provide more resources not to execute existing programs faster but to accommodate additional computation and programs without changing the real-time behavior of existing programs. LET programs are thus composable with respect to real-time behavior even on distributed systems. LET programming also supports model-based embedded software design in the sense that control models designed in, e.g., Simulink, that use LET semantics can be translated into LET programs written in, e.g., Giotto, and then compiled into executable code that approximates the behavior of the original models in real time. Giotto and other LET programs have been compiled

<sup>&</sup>lt;sup>18</sup> http://kabru.eecs.umich.edu/aires/

into portable real-time code targeting the Embedded Machine, e.g., to control a model helicopter, and into so-called schedule-carrying code for increased efficiency.

In Giotto, the LET of a task must be equal to its period, i.e., the task can only read a sensor at the beginning of its period and update an actuator at the end of its period. The advantage of this rather restrictive model is that checking time safety of Giotto programs is fast even in the presence of multiple so-called modes, and precise if all modes are reachable by mode switching. Giotto programs may specify modes and when to switch modes. Giotto modes are essentially different configurations of tasks, sensors, and actuators. Checking time safety of programs with multiple modes is non-trivial because modes may be switched even before the execution of a mode has been completed.

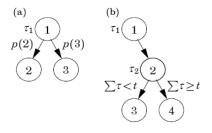

More recent work on extending Giotto has essentially focused on two directions. xGiotto supports mixed sets of time- and event-triggered LET tasks at the expense of checking time safety fast, [XGiotto, 2004]. HTL supports hierarchical program composition where task LETs may be different than task periods at the expense of checking time safety precisely, [HTL, 2006]. In other words, there is an expensive but precise time safety check for xGiotto, and a fast but imprecise time safety check for HTL, i.e., if the time safety check of an HTL program fails, the program may still be time-safe. However, if the time safety check succeeds, tasks in lower levels of the program's hierarchy may be replaced by other tasks without re-checking time safety. The ongoing work on HTL is a collaborative effort between UC Berkeley, EPFL in Switzerland, the University of Salzburg in Austria, and the Technical University of Timisoara in Romania. A prototype tool chain is available at http://htl.cs.uni-salzburg.at.

#### 3.6 Safety and reliability

Tools with an origin in the safety community have evolved rather independently of the other mentioned tools and provide support for example for fault-tree, failure mode effects and hazard analysis. Tools supporting reliability analysis are on the other hand related to tools in the discrete-event area (compare for example Markov chains), and also have a strong connection to formal analysis tools.

There seems to be very few tools that address the intersection between control design and safety/reliability tools. Some exceptions in this regard include the following:

- Bridges between control design and safety tools were developed in the SETTA project, allowing failure modes to be defined within Simulink and export for the generation of fault-trees, [Papadopoulos et al., 2001].

- In work at KTH, based on the experiences with co-simulation [El-khoury, Törngren, 2001], a Simulink library was developed that supports fault-injection in terms of bit-flips in all types of blocks, signals and constants. The library has been used to evaluate the effects of transient hardware faults on control system robustness and in devising control algorithms that are resilient to such faults, [Norberg and Törngren, 2003].

However, there exists a lot of related work in industry with proprietary tooling environments for these purposes.

#### 4 Overview of selected tools

This section is organized as follows. Sub-sections 4.1-4.8 describe the different tools mentioned previously. Each tool is presented by an introductory overview that describes the main use and intentions of the tool. Each tool is visualized by a simple example.

The overview is followed by a more detailed description of various aspects of the tool used for comparison. The comparative aspects are divided in two main areas; the context and purpose of the tool and the actual tool technology.

The context and purpose area treats the following aspects:

- Which are the intended scenarios and development stages that the tool is supporting?

- Which specific activities are supported?

- Which qualities and constraints are addressed?

- Are there any special methodological considerations connected with the tool?

The tool technology area treats

- Description of the tool architecture

- Which inputs does the tool require

- Which outputs are generated

- Modeling content (or semantics)

- Tool automation

- Extensibility

- Availability

#### 4.1 AIDA

#### **Tool Overview**

The Aida toolset [Redell et al., 2004] is an environment for model-based design and analysis of real-time control systems. The most important feature of Aida is that it allows a user to take implementation effects into consideration when analyzing the performance of an automatic control system. Considered implementation effects include delays and time variations in the execution and scheduling of control functions and communication of data. The toolset also supports timing analysis of the real-time design such that an implemented solution can be shown to be schedulable and meet its timing constraints.

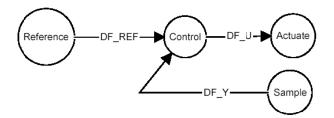

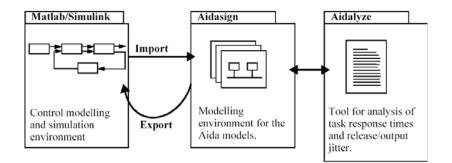

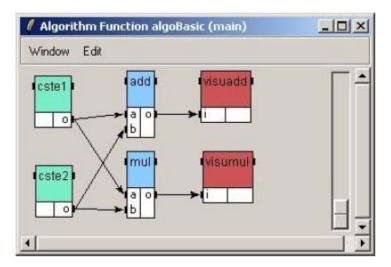

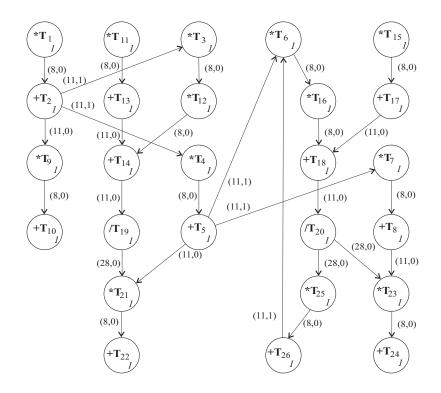

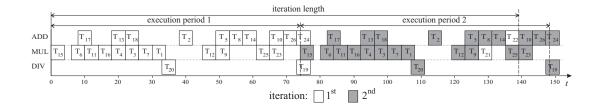

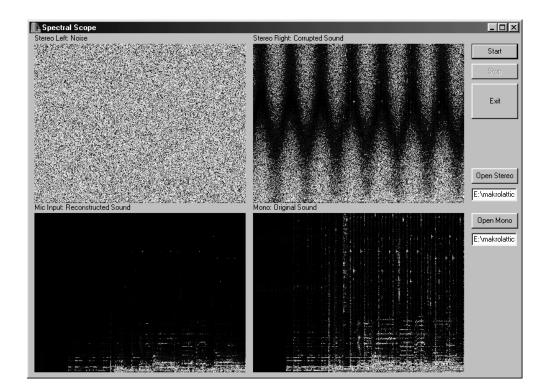

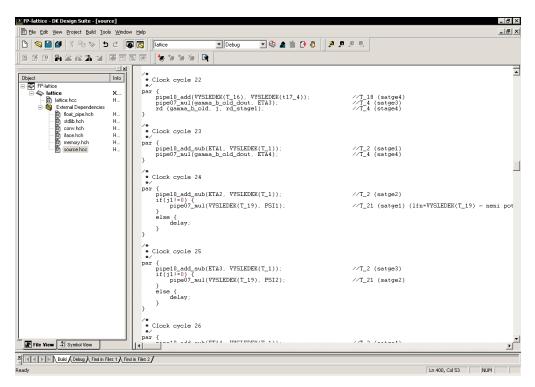

The toolset consists of a modelling environment, *Aidasign*, which interfaces with MATLAB/Simulink [The Mathworks, 2005], and a response time analysis tool, *Aidalyze*. In the toolset, a controller is designed using MATLAB/Simulink, which is an environment familiar to control engineers that supports simulation based analysis of control performance. The real-time system design starts with the translation of the Simulink model to a *data-flow diagram* (DFD) in *Aidasign*. The timing aspects of the controller, such as sampling periods and delays then constitute requirements on the real-time system design. The functions and communication flows specified in the data-flow diagram form the basis for all further modelling in Aida. Apart from being

generated from Simulink models, data-flow diagrams can be specified completely or in parts within Aida. Figure 6 shows an example of a data-flow diagram with four functions and the related data flows connecting them.

Figure 6. An example of an AIDA data flow Diagram

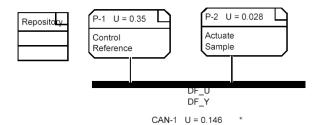

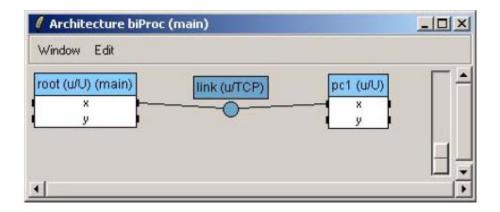

Another fundamental model in Aida is the *hardware structure diagram* (HSD), where the hardware architecture, in terms of processors and their interconnections via communication links, is designed. In the HSD the functions and data flows in the associated data-flow diagram(s) are mapped to processors and communication links, respectively. Figure 7 shows an HSD with two processors (P-1 and P-2) that are interconnected via a CAN-bus (*CAN-1*). The mapping of functions and data flows in Figure 6 is visualised. The utilisation (U) of each component is computed based on underlying models and the repository is used to temporarily store functions and data-flows that have not yet been mapped to any component.

Based on these two fundamental models and the mapping between them, a real-time implementation is designed. The design includes specification of operating system processes; their inter-communication in terms of messages; mapping of messages to CAN-frames; and triggering of process executions.

Figure 7. An example of an AIDA hardware structure diagram

When the real-time system design has been completed, upper and lower bounds on the response times and release/response jitter (variations in release and response times) of the functions, processes and inter-process communications can be derived using the Aidalyze tool. These results can then be exported back to the control domain in the form of a Simulink model augmented with timing and execution order information. Hence, timing effects due to implementation can be incorporated in the control performance analysis through simulation of the generated Simulink diagram.

#### **Comparative Aspects**

**Scenarios Supported.** AIDA is intended for one particular development scenario, but sub-scenarios can be followed as well. The major scenario starts in the control system design tool MATLAB/Simulink in which the data-flows in the control system are specified. The Simulink model is then imported to the Aida toolset in which a data-flow representation of the system is automatically generated. The data-flow model is augmented by the user with estimates of best- and worst-case execution times for functions and communication needs for the data-flows. The resulting model is the base for all other models in the tool-set.

Next, a real-time implementation of the control system is described using the models available in Aida. Given the model description of the implementation, a response time analysis is performed producing bounds on the response times of functions and processes. Finally, a transformed Simulink model can be generated, including delays according to the response time analysis results. The Simulink model can be used in simulation to test the control performance given the implementation induced delays.

**Development Stages and Activities Supported.** The toolset can be used on different early stages in the development, but to make use of the complete scenario outlined above it should be used when the control system design is close to finalized and when the implementation of it is to begin. The hardware architecture could be fixed beforehand, or its design could also be guided by the results of Aida simulations. Hence, the toolset could be used to for example:

- compare and evaluate hardware architectures

- compare and evaluate software architectures

- compare and evaluate control system designs

**Figure 8.** Architectural overview of the Aida toolset, highlighting the three parts: The interface with MATLAB/Simulink; the real-time system modelling environment (Aidasign); and the response time analysis tool (Aidalyze).

**Qualities/Constraints Addressed.** As of today, the timing behaviour of an implementation is addressed through analysis on a real-time scheduling level. The qualities that are addressed include response time bounds and schedulability. Furthermore, using the generated control models augmented with timing information, the control system performance can be evaluated through simulation.

#### Methodological Considerations. See Scenarios.

**Tool Architecture.** The Aida toolset consists of two major parts, Aidasign for modelling of real-time implementations of control systems, and Aidalyze which is a stand-alone tool for response time analysis of distributed fixed-priority scheduled tasks that may be precedence related forming transactions.

Aida interfaces to MATLAB/Simulink, which enables import of control system models and export of the same models augmented with timing information. The interfacing activities are completely controlled from Aidasign. Figure 8 gives an overview of the tool set architecture.

**Tool Inputs.** The user needs to provide estimates of worst (and possibly best) case execution times of the modelled functions, when executing on the modelled processors. Furthermore, the communication needs in each data flow (number of bytes) must to be specified.

In order to use the tool according to the intended scenario, a control system model made in Simulink is also needed. If such a model does not exist, the Aida toolset can be used to bound the response times of a system completely modelled within Aidasign. However, in that case no export to Simulink can be performed.

**Tool Outputs.** Aidalyze produces bounds on the worst- and best-case response times of each function, process and CAN-frame in the system. The Aida tool computes the utilization of each processor and CAN-bus. If a Simulink model is imported to Aida, as a base for the implementation model, a Simulink model augmented with timing information can be generated as an output.

*Modeling Content.* Apart from the modelling capabilities of Simulink, the Aida toolset includes the following models:

• *Data flow diagram* (DFD). Functions are specified and connected by data flow relations in the DFD. A function is parameterized by its minimum and maximum execution times while a data flow is simply described with the number of bytes that it communicates. See Figure 6.

Figure 9. An example of an AIDA function timing and triggering diagram.

Figure 10 Process timing and triggering diagrams for processors P-1 (a) and P-2 (b) of Fig. 7.

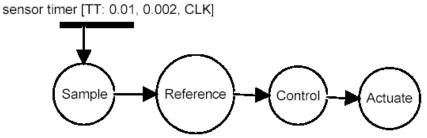

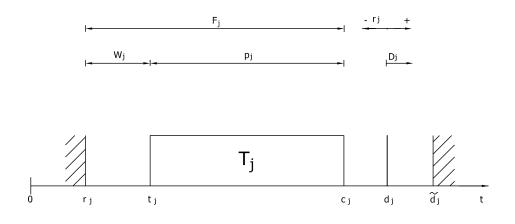

- *Function timing and triggering diagram* (FTTD). The FTTD is used to describe the sequences of precedence-related functions (the control flow) and the triggering of such sequences using periodic (time) or aperiodic (event) triggers. Figure 9 shows an FTTD where the execution sequence of the functions in the example application of Figure 6 have been specified. The diagram also shows a time trigger (TT) named *sensortimer* used to trigger the execution of the sample function. The parameters of the trigger are: the period (0.01); the admissible jitter (0.002); and the name of the source clock (CLK). The FTTD can be interpreted together with the DFD as a way to set the requirements on the implementation and does not directly specify any part of the implementation. FTTDs are therefore not necessary for a complete system description.

- *Hardware structure diagram* (HSD). As described above, the HSD is used to specify the hardware architecture as a network of processors interconnected by CAN buses. Processors are parameterized by a speed factor, used to scale the execution time of allocated functions. CAN buses are also associated with speed parameters, defining the communication speed on the bus. Furthermore, functions and data-flows are mapped to processors and buses in the HSD, as shown in Figure 7.

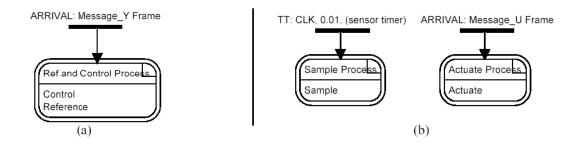

- *Process timing and triggering diagram* (PTTD). For each processor in an HSD there is a PTTD that describes the triggering of the contained processes' execution. Process execution may be triggered by a precedence relationship (completion of another process); by the arrival of a CAN frame; or by time or event triggers. The PTTD is also used to specify the processes by mapping functions in a processor to different processes. A process is assigned a fixed priority for scheduling. Figure 10 shows the PTTDs for the two processors in Figure 7. The execution of the sample process are triggered by a time trigger with period 0.01 while the other two processes are triggered by arriving CAN-frames.

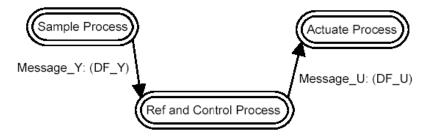

- *Process internal timing and triggering diagram* (PiTTD). The PiTTD is used to define the execution sequence of functions within a process. It simply relates the functions included in a process in precedence order. Figure 11 shows the very simple PiTTD for the Ref and Control process executing in processor P-1.

Figure 11 The process internal timing and triggering diagram of the Ref and Control process.

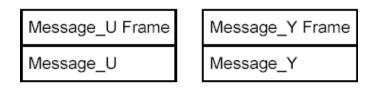

• *Process structure diagram* (PSD). The PSD is basically an implementation version of the DFD. It defines how processes communicate via messages. The messages are composed of data flows that are communicated between functions in different processes. Many data flows may be included in a single message, if these data flows have the same sending and receiving processes. The PSD for the example application is shown in Figure 12. It defines two inter-process messages: *Message\_U* and *Message\_Y*.

Figure 12 The process structure diagram for the example system.

• *Communication link diagram* (CLD). In the CLD the messages that were defined in the PSD are distributed on different CAN frames. One frame may include more than one message, but no more than 8 bytes in total. Figure 13 shows how the messages defined in Figure 12 are allocated to two different CAN frames. The arrivals of these frames are used to trigger the execution of the processes in the PTTDs in Figure 10.

*Tool Automation* The Simulink models are automatically transformed to Aida data-flow models when imported, and timing-augmented Simulink models are automatically generated from the Aida models.

The included tool Aidalyze may be used to perform response time analysis when an implementation model has been completely specified.